Simulation and Prototype model of Power ... - VIT University

Simulation and Prototype model of Power ... - VIT University

Simulation and Prototype model of Power ... - VIT University

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>VIT</strong><br />

<strong>University</strong><br />

Vellore-632 014, Tamil Nadu, India.<br />

www.vit.ac.in<br />

Two Day Workshop on<br />

<strong>Simulation</strong> <strong>and</strong> <strong>Prototype</strong> <strong>model</strong> <strong>of</strong><br />

<strong>Power</strong> Electronics circuits using PSPICE<br />

6 th & 7 th April 2012<br />

TIFAC-CORE IN AUTOMOTIVE INFOTRONICS @<strong>VIT</strong> E<br />

‣ State <strong>of</strong> the art advanced engineering centre for research, consultancy <strong>and</strong> manpower training in<br />

Automotive Infotronics is established at <strong>VIT</strong> <strong>University</strong> promoted by TIFAC (Technology<br />

Information Forecast <strong>and</strong> Assessment Council), under the Mission REACH program.<br />

‣ Offers a full time PG program in Automotive Electronics to provide industry ready engineers.<br />

Background<br />

‣ The purpose <strong>of</strong> the proposed workshop is to provide opportunities for delegates with various<br />

engineering backgrounds to gain knowledge <strong>and</strong> experience on power electronics semiconductor<br />

devices technology, <strong>Simulation</strong> <strong>and</strong> hardware prototype implementation on power electronic<br />

converters circuits. This program will <strong>of</strong>fer student’s systematic training in engineering fields<br />

like Electrical & Electronics, Electronics & Instrumentation <strong>and</strong> other circuit branch fields are<br />

applied.<br />

Programme<br />

This workshop aims to underst<strong>and</strong> <strong>Power</strong> electronics Technology, <strong>Simulation</strong> <strong>and</strong> Hardware<br />

implementation on <strong>Power</strong> electronics converters circuits by ORCAD <strong>and</strong> its applications<br />

Organized by<br />

TIFAC - CORE in AUTOMOTIVE INFOTRONICS<br />

(Sponsored by Department <strong>of</strong> Science <strong>and</strong> Technology, Govt. <strong>of</strong> India)<br />

Coordinators<br />

Dr. K. Ganesan, Director, TIFAC CORE & Senior Pr<strong>of</strong>essor, SITE<br />

V. Gopi Srikanth, Senior Development Engineer, TIFAC CORE<br />

D. Muralidar, Assistant Pr<strong>of</strong>essor, TIFAC CORE<br />

Topics Covered<br />

‣ Introduction to ORCAD Capture Tool<br />

ORCAD tool Introduction<br />

Placing the power electronics components in ORCAD<br />

Creation <strong>of</strong> net list, PSPICE <strong>Simulation</strong> pr<strong>of</strong>ile <strong>and</strong> Debugging the circuit<br />

‣ Technology<br />

<strong>Power</strong> electronics switches<br />

Components & Operation<br />

Single phase half wave controlled rectifier with R ,RL <strong>and</strong> RLE loads<br />

(Hardware prototype <strong>model</strong> using Thyristor <strong>and</strong> gate triggering)<br />

Three phase half wave controlled rectifier with R,RL <strong>and</strong> RLE loads<br />

Single phase fully controlled bridge rectifier by using AC source inductance with R,RL<br />

<strong>and</strong> RLE loads<br />

Three phase fully controlled bridge rectifier by using AC source inductance with R,RL<br />

<strong>and</strong> RLE loads<br />

Single phase type A ,type B, type C, type D choppers<br />

Single phase series <strong>and</strong> parallel voltage source inverters (VSI) using MOSFET as switch<br />

Super Capacitance(Farads) based power efficiency backup <strong>of</strong> 30sec. by analysis,<br />

simulation <strong>and</strong> prototype <strong>model</strong><br />

Analysis, simulation <strong>and</strong> prototype <strong>model</strong> <strong>of</strong> buck <strong>and</strong> boost converters in application to<br />

switched mode power supplies (SMPS)

Participation is open to:<br />

Engineers from Industries<br />

Faculties<br />

Research Scholars<br />

Students<br />

REGISTRATION FEES:<br />

Rs. 1500 per delegate from Industry<br />

Rs. 1200 per delegate from Institute (Faculty)<br />

Rs. 1000 per delegate from Institute (Student & Research Scholar)<br />

Registration charges include Course Material, Lunch & Snacks. The number <strong>of</strong> participants is<br />

limited to 25 based on first come first serve. Accommodation can be arranged in our Guest House on<br />

request based on first come first serve as per Tariff given below:<br />

Tariff per day: Payment through cash<br />

Sl. No. Type Tariff Rs.<br />

1 Main Guest House A/C 1900.00<br />

2 Guest House (Annex) Deluxe A/C 1650.00<br />

Payment through DD drawn in favor <strong>of</strong> “TIFAC CORE, <strong>VIT</strong> <strong>University</strong>”, Payable at Vellore.<br />

Venue:<br />

Room No.: 701, Technology Tower<br />

7 th Floor, <strong>VIT</strong><br />

Date <strong>and</strong> Time:<br />

6 th <strong>and</strong> 7 th April 2012 : 09.30 – 17.00 Hours<br />

HOW TO REACH <strong>VIT</strong><br />

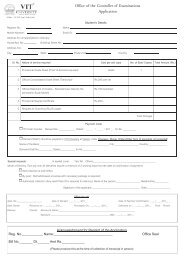

Format for Registration confirmation<br />

Two Days Workshop on<br />

<strong>Simulation</strong> <strong>and</strong> <strong>Prototype</strong> <strong>model</strong> <strong>of</strong><br />

<strong>Power</strong> Electronics circuits using ORCAD<br />

6 th & 7 th April 2012<br />

Name: -----------------------------------------------------------------------------------<br />

Designation: ----------------------------------------------------------------------------<br />

Organization: ---------------------------------------------------------------------------<br />

Address: ---------------------------------------------------------------------------------<br />

--------------------------------------------------------------------------------------------<br />

--------------------------------------------------------------------------------------------<br />

Phone: -------------------------Mobile-------------------------------------------------<br />

Fax: ----------------------------e-mail: -------------------------------------------------<br />

DD Details: -----------------------------------------------------------------------------<br />

Signature <strong>of</strong> the Participant<br />

Payment through DD drawn in favor <strong>of</strong> “TIFAC CORE, <strong>VIT</strong> <strong>University</strong>”, Payable at Vellore.<br />

Please complete <strong>and</strong> mail or fax us above form before 4 th April 2012.<br />

For details about our centre, visit our web site www.vit.ac.in/tifaccore/<br />

For Further Details Please Contact:<br />

Ms. R. Devaki<br />

Mr. V. Gopi Srikanth<br />

Secretary, TIFAC-CORE<br />

Senior Development Engineer<br />

7th Floor, Technology Tower, TIFAC CORE<br />

<strong>VIT</strong>, Vellore-632 014 Cell: 7708244621<br />

Tamil Nadu. Email: gopi.vegi@vit.ac.in<br />

Tel: 0416-2202381<br />

Fax: 0416-2244797 Mr. D. Muralidar<br />

e-mail: tifac@vit.ac.in<br />

Assistant Pr<strong>of</strong>essor, TIFAC CORE<br />

Cell: 9894335864<br />

E-mail: muralidar.d@vit.ac.in

![[26th â 30th Oct 2009] - Result - VIT University](https://img.yumpu.com/48486076/1/184x260/26th-a-30th-oct-2009-result-vit-university.jpg?quality=85)