Compal Confidential - ROM.by

Compal Confidential - ROM.by

Compal Confidential - ROM.by

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

A<br />

B<br />

C<br />

D<br />

E<br />

ZZZ<br />

PCB<br />

Part Number = DAZ0FQ00100<br />

ZZZ<br />

1 1<br />

64M512@<br />

X76244BOL01<br />

Part Number = X76244BOL01<br />

ZZZ<br />

64M1G@<br />

<strong>Compal</strong> <strong>Confidential</strong><br />

X76244BOL03<br />

Part Number = X76244BOL03<br />

ZZZ<br />

128M1G@<br />

X76244BOL05<br />

Part Number = X76244BOL05<br />

ZZZ<br />

128M2G@<br />

2 2<br />

X76244BOL06<br />

Part Number = X76244BOL06<br />

PEW76 Schematics Document<br />

AMD Danube<br />

Champlain Processor with RS880M/SB820/Madison VGA<br />

2010-06-07<br />

3 3<br />

LA5911P REV: 1.0<br />

www.mycomp.su<br />

4 4<br />

A<br />

B<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2010/03/12<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

B<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 1 of<br />

55<br />

C<br />

D<br />

E

A<br />

<strong>Compal</strong> <strong>Confidential</strong><br />

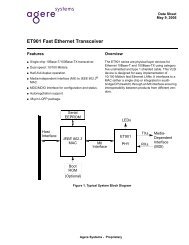

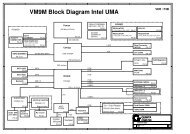

Model Name : NEW75/85/95<br />

B<br />

1 1<br />

2 2<br />

LED<br />

page 40<br />

3 3<br />

RTC CKT.<br />

page 26<br />

LID SW / MEDIA/B<br />

page 39<br />

Power On/Off CKT.<br />

page 41<br />

MINI Card 1<br />

WLAN<br />

page 36<br />

GPP1<br />

LVDS<br />

CRT<br />

page 24<br />

page 26<br />

HDMI Conn.<br />

page 25<br />

Fan Control<br />

VRAM 1GB<br />

64M16 x 8<br />

DDR3<br />

ATI M97<br />

Madisan/Park<br />

uFCBGA-962<br />

page 19, 20<br />

Page 14,15,16,17,18,21,22<br />

LAN(GbE)<br />

Broadcom<br />

BCM57780<br />

GPP0<br />

page 44<br />

Extend Card/B<br />

1. USB X2<br />

2. Cardreader<br />

JM385<br />

page 34<br />

RJ45<br />

page 35<br />

PCI-Express x 16<br />

Gen2<br />

Danube<br />

AMD S1G4 Processor<br />

Touch Pad<br />

EC I/O Buffer<br />

uPGA-638 Package<br />

Champlain<br />

Hyper Transport Link<br />

16 x 16<br />

page 39<br />

page 38<br />

ATI RS880M<br />

uFCBGA-528<br />

A link Express2<br />

Gen1<br />

C<br />

page 4,5,6,7<br />

page 10,11,12,13<br />

ATI SB820M<br />

uFCBGA-605<br />

page 27,28,29,30,31<br />

LPC BUS<br />

ENE KB926<br />

page 38<br />

Int.KBD<br />

BIOS<br />

3.3V 48MHz<br />

page 39<br />

page 39<br />

USB<br />

conn<br />

X 3<br />

3.3V 24.576MHz/48Mhz<br />

S-ATA<br />

USB port 0,1,2<br />

SATA HDD<br />

Conn.<br />

page 36,37 page 27 page 37 page 36<br />

page 32<br />

port 0<br />

CMOS<br />

Camera<br />

CD<strong>ROM</strong><br />

Conn.<br />

page 32<br />

port 1<br />

D<br />

Memory BUS(DDR3)<br />

204pin DDRIII-SO-DIMM X2<br />

Dual Channel BANK 0, 1, 2, 3 page 8,9<br />

1.5V DDRIII 800~1333MHz<br />

Thermal Sensor<br />

ADM1032<br />

Bluetooth<br />

Conn<br />

<br />

USB<br />

HD Audio<br />

www.mycomp.su<br />

Gen2<br />

Clock Generator<br />

ICS9LPRS488<br />

page 6 page 23<br />

Mini<br />

card<br />

(WL)X1<br />

USB port 5 USB port 12 USB port 8<br />

HDA Codec<br />

ALC272X<br />

page 42<br />

Audio AMP<br />

page 43<br />

Phone Jack x2<br />

page 43<br />

page 36<br />

3G/GPS<br />

WWAN<br />

<br />

USB port 9<br />

E<br />

page 36<br />

Card<br />

Reader<br />

USB port 6<br />

DC/DC Interface CKT.<br />

page 45<br />

4 4<br />

Power Circuit<br />

page 46,47,48,49,50,51<br />

52,53,54<br />

A<br />

B<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2009/10/06<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

B<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 2 of<br />

55<br />

C<br />

D<br />

E

5<br />

4<br />

3<br />

2<br />

1<br />

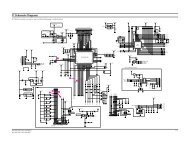

AMD<br />

D<br />

VGA<br />

ATI<br />

Madison/Park<br />

D<br />

C<br />

B<br />

A_SODIMM<br />

B_SODIMM<br />

MEM_MA_CLK1_P/N<br />

MEM_MA_CLK7_P/N<br />

1066MHz<br />

MEM_MB_CLK1_P/N<br />

MEM_MB_CLK7_P/N<br />

1066MHz<br />

AMD<br />

S1G4<br />

CPU SOCKET<br />

GPP_CLK3P<br />

WLAN<br />

Mini PCI Socket<br />

100MHz<br />

CPU_HT_CLKP/N<br />

200MHz<br />

GbE LAN<br />

Broadcom<br />

B57780<br />

GPP_CLK1P/N<br />

100MHz<br />

AMD<br />

VGA_CLKP/N<br />

100MHz<br />

SB<br />

SB820M<br />

Internal CLK GEN<br />

32.768KHz<br />

25MHz<br />

CLK_SBSRC_BCLK/#<br />

100MHz<br />

NB_DISP_CLKP/N<br />

100MHz<br />

NB_HT_CLKP/N<br />

100MHz<br />

www.mycomp.su<br />

AMD<br />

NB<br />

RS880M<br />

C<br />

B<br />

A<br />

A<br />

5<br />

4<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

<strong>Compal</strong> Electronics, Inc.<br />

Issued Date<br />

2005/10/10 Title<br />

Deciphered Date 2010/03/12<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size Document Number Rev<br />

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF R&D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

Custom<br />

401827 D<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 3 of<br />

55<br />

3<br />

2<br />

1

A<br />

B<br />

C<br />

D<br />

E<br />

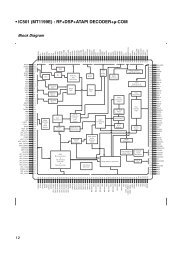

Voltage Rails<br />

STATE<br />

Full ON<br />

SIGNAL<br />

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock<br />

HIGH HIGH HIGH HIGH ON ON ON ON<br />

Power Plane<br />

Description<br />

S1 S3 S5<br />

S1(Power On Suspend)<br />

LOW<br />

HIGH<br />

HIGH<br />

HIGH<br />

ON<br />

ON<br />

ON<br />

LOW<br />

VIN<br />

Adapter power supply (19V)<br />

N/A N/A N/A<br />

B+<br />

AC or battery power rail for power circuit. N/A N/A N/A<br />

+CPU_CORE_0 Core voltage for CPU (0.7-1.2V)<br />

ON OFF OFF<br />

+CPU_CORE_1 Core voltage for CPU (0.7-1.2V) ON OFF OFF<br />

+CPU_CORE_NB Voltage for On-die Northbridge of CPU(0.8-1.1V)ON OFF OFF<br />

+0.9V<br />

0.9V switched power rail for DDR terminator ON ON OFF<br />

+1.1VS<br />

1.1V switched power rail for NB VDDC & VGA ON OFF OFF<br />

+1.2V_HT 1.2V switched power rail ON OFF OFF<br />

+VGA_CORE<br />

0.95-1.2V switched power rail<br />

ON OFF OFF<br />

+1.5VS<br />

1.5V power rail for PCIE Card<br />

ON OFF OFF<br />

+1.8V<br />

1.8V power rail for CPU VDDIO and DDR ON ON OFF<br />

+1.8VS<br />

1.8V switched power rail<br />

ON OFF OFF<br />

+2.5VS<br />

2.5V for CPU_VDDA<br />

ON OFF OFF<br />

+3VALW<br />

3.3V always on power rail<br />

ON ON ON*<br />

+3V_LAN 3.3V power rail for LAN ON ON ON<br />

S3 (Suspend to RAM)<br />

S4 (Suspend to Disk)<br />

1 1<br />

+3VS<br />

+5VALW<br />

+5VS<br />

3.3V switched power rail<br />

5V always on power rail<br />

5V switched power rail<br />

+VSB VSB always on power rail ON ON ON*<br />

+RTCVCC<br />

RTC power<br />

ON ON ON<br />

S5 (Soft OFF)<br />

LOW LOW LOW LOW<br />

2 2<br />

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.<br />

External PCI Devices<br />

Device IDSEL# REQ#/GNT# Interrupts<br />

EC SM Bus1 address<br />

SB820<br />

SM Bus 0 address<br />

Device<br />

Clock Generator<br />

(SILEGO SLG8SP626)<br />

DDR DIMM1<br />

DDR DIMM2<br />

Mini card<br />

Address<br />

1101 001Xb<br />

1001 000Xb<br />

1001 010Xb<br />

ON<br />

ON<br />

ON<br />

OFF<br />

ON<br />

OFF<br />

OFF<br />

ON*<br />

OFF<br />

EC SM Bus2 address<br />

SB820<br />

SM Bus 1 address<br />

4 4<br />

LOW<br />

LOW<br />

LOW<br />

LOW<br />

HIGH<br />

LOW<br />

HIGH<br />

HIGH<br />

Board ID / SKU ID Table for AD channel<br />

Vcc 3.3V +/- 5%<br />

Ra/Rc/Re 100K +/- 5%<br />

Board ID<br />

Rb / Rd / Rf VAD_BID min VAD_BID<br />

typ VAD_BID max<br />

0<br />

0<br />

0 V<br />

0 V 0 V<br />

1 8.2K +/- 5% 0.216 V 0.250 V 0.289 V<br />

2<br />

3<br />

4<br />

18K +/- 5%<br />

33K +/- 5%<br />

56K +/- 5%<br />

0.436 V<br />

0.712 V<br />

1.036 V<br />

0.503 V<br />

0.819 V<br />

1.185 V<br />

0.538 V<br />

0.875 V<br />

1.264 V<br />

5 100K +/- 5% 1.453 V 1.650 V 1.759 V<br />

6<br />

7<br />

200K +/- 5%<br />

NC<br />

1.935 V<br />

2.500 V<br />

2.200 V<br />

3.300 V<br />

2.341 V<br />

3.300 V<br />

BOARD ID Table<br />

Board ID<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

PCB Revision<br />

ON<br />

ON<br />

ON<br />

ON<br />

OFF<br />

OFF<br />

OFF<br />

OFF<br />

OFF<br />

OFF<br />

OFF<br />

OFF<br />

BTO Option Table<br />

BTO Item<br />

BOM Structure<br />

3 3<br />

Device<br />

Address HEX<br />

Device<br />

Address HEX<br />

0<br />

NEW75/85/95<br />

Smart Battery 0001 011X b 16H<br />

ADI ADM1032 (CPU) 1001 100X b 98H<br />

1<br />

PEW76/86/96<br />

GMT G781-1 (GPU) 1001 101X b 9AH<br />

2<br />

PEW56<br />

SB-Temp Sensor<br />

98H<br />

HEX<br />

D2<br />

90<br />

94<br />

Device<br />

Address<br />

BOM Config<br />

Project ID Table<br />

Board ID<br />

3<br />

4<br />

5<br />

6<br />

7<br />

EXT CLKGEN<br />

INT CLKGEN<br />

No USB Patch<br />

Capilano w/ USB patch<br />

Add USB patch<br />

--For SSID define<br />

--For TSI thermal math<br />

PCB Revision<br />

www.mycomp.su<br />

PowerXpress SKU(Madison): 3G@/BT@/UMA@/ VGA@/SG@/EXT@/EXTPW@/VB@/MAD@<br />

PowerXpress SKU(Park): 3G@/BT@/UMA@/ VGA@/SG@/EXT@/EXTPW@/VB@/PARK@<br />

DIS ONLY:(Park) 3G@/BT@/DISO@/ VGA@/EXT@/EXTPW@/PARK@<br />

UMA only SKU: 3G@/BT@/UMA@/ UMAO@/EXT@/VB@<br />

PowerXpress SKU(Madison):3G@/BT@/UMA@/VGA@/SG@/INT@/VB@/MAD@<br />

PowerXpress SKU(Park): 3G@/BT@/UMA@/VGA@/SG@/INT@/VB@/PARK@<br />

DIS ONLY(PARK): 3G@/BT@/DISO@/VGA@/INT@/PARK@<br />

UMA only SKU: 3G@/BT@/UMA@/UMAO@/INT@/VB@<br />

A<br />

B<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2010/03/12<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

B<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 4 of<br />

55<br />

C<br />

D<br />

E

5<br />

4<br />

3<br />

2<br />

1<br />

BATTERY<br />

12.6V<br />

AC ADAPTOR<br />

19V 90W<br />

BATT+<br />

VIN<br />

PU5<br />

CHARGER<br />

ISL6261AHAZ-T<br />

PU15<br />

ISL6265IRZ-T<br />

+CPU_CORE<br />

+CPU_CORE_NB<br />

PU16<br />

APL5508-25DC<br />

+2.5VS<br />

PU12<br />

APL5915<br />

+1.05VS<br />

+CPU_CORE<br />

+CPU_CORE_NB<br />

+1.05VS<br />

+1.1VS<br />

AMD CPU S1G4<br />

0.7~1.3V VDD CORE 36A<br />

0.8~1.2V VDDNB 4A<br />

2.5V VDDA 250mA<br />

1.5V VDDIO 3A<br />

1.05V VDDR 1.5A<br />

1.1V VLDT 1.5A<br />

D<br />

B+<br />

PU7<br />

RT8209BGQW<br />

+1.5V<br />

+1.5V<br />

RAM DDRIII SODIMMX2<br />

1.5V VDD_MEM 4A<br />

0.75V VTT_MEM 0.5A<br />

+0.75VS<br />

PU10<br />

APL5913<br />

D<br />

NorthBridge AMD RS880M<br />

C<br />

B<br />

+INVPWR_B+<br />

LCD panel<br />

15.6"<br />

B+ 300mA<br />

+3.3 350mA<br />

FAN Control<br />

APL5607<br />

PU8<br />

RT8209BGQW<br />

PU6<br />

RT8209BGQW<br />

PU17<br />

APW7138NITRL<br />

PU4<br />

SN0806081 RHBR<br />

+NB_CORE<br />

+1.1VALW<br />

+GPU_CORE<br />

+3VALW<br />

+5VALW<br />

PU19<br />

TSP51117RGYR<br />

+VDDCI<br />

+1.8VS<br />

PU14<br />

PU11<br />

APL5913<br />

MP2121DQ<br />

+1.8VSP2<br />

+1.8VSP1<br />

U34<br />

SI4800BDY +5VS<br />

PU10<br />

APL5913<br />

+1.5V<br />

+1VSG<br />

U37<br />

SI1800BDY<br />

+3VS<br />

U35<br />

SI4800BDY<br />

+1.5VS<br />

+1.1VALW<br />

+1.5VS<br />

www.mycomp.su<br />

+1.1VALW<br />

+1.1VS<br />

U36<br />

SI4800BDY<br />

+1.1VS<br />

Delay<br />

+3VS_DELAY<br />

1.0~1.1V<br />

1.1V_S0<br />

1.8V_S0<br />

3.3V_S0<br />

No Use<br />

VGA ATI Madison / Park<br />

0.85~1.1V<br />

1.0V<br />

1.5V<br />

1.8V<br />

3.3V<br />

SouthBridge AMD SB820M<br />

1.1V_S0<br />

1.1V_S5<br />

VDDC 1.0V-1.1V 7.6A<br />

VDDHTRX+HT 0.68A<br />

VDDPCIE 1.1A<br />

VDDHTTX 0.68A<br />

PLLs 0.23A<br />

VDDA18 0.64A<br />

VDDG18 0.005A<br />

VDDLT18 0.22A<br />

PLLs 0.1A<br />

VDDG33 0.06A<br />

AVDD 0.125A<br />

VDDLT33 0A<br />

VDD18_MEM 1.8V 0.005A<br />

VDD_MEM 1.8V 0.23A<br />

VDDC 29 A<br />

VDDCI 4 A<br />

PCIE_VDDC 2 A<br />

DP[F:A]_VDD10 230 mA<br />

DPLL_VDDC 125 mA<br />

SPV10 100 mA<br />

VDDR1 TBD A<br />

PCIE_PVDD 40 mA<br />

PCIE_VDDR 400 mA<br />

TSVDD 5 mA<br />

VDDR4 TBD mA<br />

VDD_CT 17 mA<br />

DP[F:A]_PVDD 20 mA<br />

DP[F:A]_VDD18 330 mA<br />

AVDD 70 mA<br />

VDD1DI 45 mA<br />

A2VDDQ 1.5 mA<br />

VDD2DI 50 mA<br />

DPLL_PVDD 75 mA<br />

MPV18 150 mA<br />

SPV18 50 mA<br />

VDDR3 60 mA<br />

A2VDD 130 mA<br />

VDDCR_11 1.1V 0.5A<br />

VDDAN_11_PCIE 1A<br />

VDDAN_11_SATA 0.8A<br />

VDDAN_11_CLK 0.4A<br />

VDDCR_11_S 113mA<br />

VDDAN_11_USB_S 200mA<br />

VDDCR_11_USB_S 197mA<br />

VDDPL_11_SYS_S<br />

VRAM 1GB<br />

64Mx16 (K4B1G1646E) * 8<br />

1.5V 2.4 A<br />

C<br />

B<br />

+5VS 500mA<br />

3.3V_S0<br />

VDDIO_33_PCIGP 0.020A<br />

VDDPL_33_PCIE 0.030A<br />

VDDPL_33_SATA 0.020A<br />

VDDPL_33_SYS<br />

U25/U40<br />

TPS2061DRG4 +USB_VCCA<br />

+USB_VCCB<br />

+3VALW<br />

3.3V_S5<br />

VDDIO_33_S<br />

VDDPL_33_USB_S<br />

VDDAN_33_USB_S 0.2A<br />

VDDAN_33_S<br />

VDDXL_33_S<br />

VDDIO_AZ_S<br />

A<br />

USB X3<br />

+5V<br />

Dual+1<br />

2.5A<br />

Audio AMP<br />

TPA6017A2<br />

+5V 25mA<br />

SATA<br />

+5V 3A<br />

+3.3V<br />

Audio Codec<br />

ALC272<br />

+5V 45mA<br />

+3.3VS 25mA<br />

Realtek<br />

RTS5159<br />

+3.3VS 300mA<br />

EC<br />

ENE KB926<br />

+3.3VALW 30mA<br />

+3.3VS 3mA<br />

LAN<br />

Atheros AR8114<br />

+3.3VALW 201mA<br />

ICS9LPRS488B<br />

+3.3V 400mA<br />

+1.1V<br />

Mini Card<br />

+1.5VS 500mA<br />

+3.3VS 1A<br />

+3.3VALW 330mA<br />

RTC<br />

Bettary<br />

No Use<br />

2.5~3.6V<br />

BAT<br />

VDDCR_11_GBE_S<br />

VDDRF_GBE_S<br />

VDDIO_33_GBE_S<br />

VDDIO_GBE_S<br />

VDDIO_18_FC<br />

VDDBT_RTC_G<br />

A<br />

5<br />

4<br />

3<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

<strong>Compal</strong> Electronics, Inc.<br />

Issued Date<br />

2009/3/8 Title<br />

Deciphered Date 2010/03/12<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size Document Number Rev<br />

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF R&D<br />

401827 D<br />

Custom<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Tuesday, September 14, 2010<br />

Date: Sheet of<br />

5 55<br />

2<br />

1

A<br />

B<br />

C<br />

D<br />

E<br />

1 1<br />

H_CADIP[0..15]<br />

H_CADIN[0..15]<br />

H_CADIP[0..15]<br />

H_CADIN[0..15]<br />

+1.1VS<br />

TBD<br />

JCPU1A<br />

+1.1VS<br />

H_CADOP[0..15]<br />

H_CADON[0..15]<br />

C7<br />

H_CADOP[0..15] <br />

H_CADON[0..15] <br />

+1.1VS<br />

250 mil<br />

2<br />

C1<br />

10U_0805_10V4Z<br />

1<br />

2<br />

C2<br />

10U_0805_10V4Z<br />

1<br />

VLDT CAP.<br />

1<br />

1<br />

1<br />

C3<br />

0.22U_0603_16V4Z<br />

C4<br />

0.22U_0603_16V4Z<br />

C5<br />

180P_0402_50V8J<br />

2<br />

2<br />

2<br />

Near CPU Socket<br />

1<br />

C6<br />

180P_0402_50V8J<br />

2<br />

2 2<br />

D1<br />

VLDT_A0<br />

HT LINK VLDT_B0<br />

AE2<br />

2 1<br />

D2<br />

VLDT_A1<br />

VLDT_B1<br />

AE3<br />

D3<br />

10U_0805_10V4Z<br />

VLDT_A2<br />

VLDT_B2<br />

AE4<br />

D4<br />

VLDT_A3<br />

VLDT_B3<br />

AE5<br />

H_CADIP0 E3<br />

H_CADOP0<br />

H_CADIN0<br />

L0_CADIN_H0 L0_CADOUT_H0<br />

AD1<br />

E2<br />

H_CADON0<br />

H_CADIP1<br />

L0_CADIN_L0 L0_CADOUT_L0<br />

AC1<br />

E1<br />

H_CADOP1<br />

H_CADIN1<br />

L0_CADIN_H1 L0_CADOUT_H1<br />

AC2<br />

F1<br />

H_CADON1<br />

H_CADIP2<br />

L0_CADIN_L1 L0_CADOUT_L1<br />

AC3<br />

G3<br />

H_CADOP2<br />

H_CADIN2<br />

L0_CADIN_H2 L0_CADOUT_H2<br />

AB1<br />

G2<br />

H_CADON2<br />

H_CADIP3<br />

L0_CADIN_L2 L0_CADOUT_L2<br />

AA1<br />

G1<br />

H_CADOP3<br />

H_CADIN3<br />

L0_CADIN_H3 L0_CADOUT_H3<br />

AA2<br />

H1<br />

H_CADON3<br />

H_CADIP4<br />

L0_CADIN_L3 L0_CADOUT_L3<br />

AA3<br />

J1<br />

H_CADOP4<br />

H_CADIN4<br />

L0_CADIN_H4 L0_CADOUT_H4<br />

W2<br />

K1<br />

H_CADON4<br />

H_CADIP5<br />

L0_CADIN_L4 L0_CADOUT_L4<br />

W3<br />

L3<br />

H_CADOP5<br />

H_CADIN5<br />

L0_CADIN_H5 L0_CADOUT_H5<br />

V1<br />

L2<br />

H_CADON5<br />

H_CADIP6<br />

L0_CADIN_L5 L0_CADOUT_L5<br />

U1<br />

L1<br />

H_CADOP6<br />

H_CADIN6<br />

L0_CADIN_H6 L0_CADOUT_H6<br />

U2<br />

M1<br />

H_CADON6<br />

H_CADIP7<br />

L0_CADIN_L6 L0_CADOUT_L6<br />

U3<br />

N3<br />

H_CADOP7<br />

H_CADIN7<br />

L0_CADIN_H7 L0_CADOUT_H7<br />

T1<br />

N2<br />

H_CADON7<br />

H_CADIP8<br />

L0_CADIN_L7 L0_CADOUT_L7<br />

R1<br />

E5<br />

H_CADOP8<br />

H_CADIN8<br />

L0_CADIN_H8 L0_CADOUT_H8<br />

AD4<br />

F5<br />

H_CADON8<br />

H_CADIP9<br />

L0_CADIN_L8 L0_CADOUT_L8<br />

AD3<br />

F3<br />

H_CADOP9<br />

H_CADIN9<br />

L0_CADIN_H9 L0_CADOUT_H9<br />

AD5<br />

F4<br />

H_CADON9<br />

H_CADIP10<br />

L0_CADIN_L9 L0_CADOUT_L9<br />

AC5<br />

G5<br />

H_CADOP10<br />

H_CADIN10<br />

L0_CADIN_H10 L0_CADOUT_H10<br />

AB4<br />

H5<br />

H_CADON10<br />

H_CADIP11<br />

L0_CADIN_L10 L0_CADOUT_L10<br />

AB3<br />

H3<br />

H_CADOP11<br />

H_CADIN11<br />

L0_CADIN_H11 L0_CADOUT_H11<br />

AB5<br />

H4<br />

H_CADON11<br />

H_CADIP12<br />

L0_CADIN_L11 L0_CADOUT_L11<br />

AA5<br />

K3<br />

H_CADOP12<br />

H_CADIN12<br />

L0_CADIN_H12 L0_CADOUT_H12<br />

Y5<br />

K4<br />

H_CADON12<br />

H_CADIP13<br />

L0_CADIN_L12 L0_CADOUT_L12<br />

W5<br />

L5<br />

H_CADOP13<br />

3 H_CADIN13<br />

L0_CADIN_H13 L0_CADOUT_H13<br />

V4<br />

H_CADON13<br />

3<br />

M5<br />

H_CADIP14<br />

L0_CADIN_L13 L0_CADOUT_L13<br />

V3<br />

M3<br />

H_CADOP14<br />

H_CADIN14<br />

L0_CADIN_H14 L0_CADOUT_H14<br />

V5<br />

M4<br />

H_CADON14<br />

H_CADIP15<br />

L0_CADIN_L14 L0_CADOUT_L14<br />

U5<br />

N5<br />

H_CADOP15<br />

H_CADIN15<br />

L0_CADIN_H15 L0_CADOUT_H15<br />

T4<br />

P5<br />

H_CADON15<br />

L0_CADIN_L15 L0_CADOUT_L15<br />

T3<br />

H_CLKIP0<br />

J3<br />

L0_CLKIN_H0 L0_CLKOUT_H0<br />

Y1<br />

H_CLKOP0 <br />

H_CLKIN0<br />

J2<br />

L0_CLKIN_L0 L0_CLKOUT_L0<br />

W1<br />

H_CLKON0 <br />

H_CLKIP1<br />

J5<br />

L0_CLKIN_H1 L0_CLKOUT_H1<br />

Y4<br />

H_CLKOP1 <br />

H_CLKIN1<br />

K5<br />

L0_CLKIN_L1 L0_CLKOUT_L1<br />

Y3<br />

H_CLKON1 <br />

H_CTLIP0<br />

N1<br />

L0_CTLIN_H0 L0_CTLOUT_H0<br />

R2<br />

H_CTLOP0 <br />

H_CTLIN0<br />

P1<br />

L0_CTLIN_L0 L0_CTLOUT_L0<br />

R3<br />

H_CTLON0 <br />

H_CTLIP1<br />

P3<br />

L0_CTLIN_H1 L0_CTLOUT_H1<br />

T5<br />

H_CTLOP1 <br />

H_CTLIN1<br />

P4<br />

L0_CTLIN_L1 L0_CTLOUT_L1<br />

R5<br />

H_CTLON1 <br />

FOX_PZ6382A-284S-41F_Champlian<br />

CONN@<br />

www.mycomp.su<br />

4 4<br />

A<br />

B<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2010/03/12<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

Custom<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 6 of<br />

55<br />

C<br />

D<br />

E

A<br />

B<br />

C<br />

D<br />

E<br />

Processor DDR3 Memory Interface<br />

JCPU1C<br />

DDRB_SDQ[63..0]<br />

MEM:DATA<br />

DDRA_SDQ[63..0] <br />

DDRB_SDQ0<br />

C11<br />

DDRA_SDQ0<br />

1 +1.5V<br />

DDRB_SDQ1<br />

MB_DATA0<br />

MA_DATA0<br />

G12<br />

1<br />

A11<br />

DDRA_SDQ1<br />

DDRB_SDQ2<br />

MB_DATA1<br />

MA_DATA1<br />

F12<br />

A14<br />

DDRA_SDQ2<br />

DDRB_SDQ3<br />

MB_DATA2<br />

MA_DATA2<br />

H14<br />

B14<br />

DDRA_SDQ3<br />

DDRB_SDQ4<br />

MB_DATA3<br />

MA_DATA3<br />

G14<br />

G11<br />

DDRA_SDQ4<br />

R1<br />

DDRB_SDQ5<br />

MB_DATA4<br />

MA_DATA4<br />

H11<br />

E11<br />

DDRA_SDQ5<br />

1K_0402_1%<br />

DDRB_SDQ6<br />

MB_DATA5<br />

MA_DATA5<br />

H12<br />

D12<br />

DDRA_SDQ6<br />

DDRB_SDQ7<br />

MB_DATA6<br />

MA_DATA6<br />

C13<br />

A13<br />

DDRA_SDQ7<br />

DDRB_SDQ8<br />

MB_DATA7<br />

MA_DATA7<br />

E13<br />

A15<br />

DDRA_SDQ8<br />

MEM_VREF<br />

DDRB_SDQ9<br />

MB_DATA8<br />

MA_DATA8<br />

H15<br />

A16<br />

DDRA_SDQ9<br />

DDRB_SDQ10<br />

MB_DATA9<br />

MA_DATA9<br />

E15<br />

A19<br />

DDRA_SDQ10<br />

DDRB_SDQ11<br />

MB_DATA10<br />

MA_DATA10<br />

E17<br />

1<br />

1<br />

A20<br />

DDRA_SDQ11<br />

R2<br />

DDRB_SDQ12<br />

MB_DATA11<br />

MA_DATA11<br />

H17<br />

C14<br />

DDRA_SDQ12<br />

1K_0402_1%<br />

DDRB_SDQ13<br />

MB_DATA12<br />

MA_DATA12<br />

E14<br />

D14<br />

DDRA_SDQ13<br />

DDRB_SDQ14<br />

MB_DATA13<br />

MA_DATA13<br />

F14<br />

C18<br />

DDRA_SDQ14<br />

2<br />

DDRB_SDQ15<br />

MB_DATA14<br />

MA_DATA14<br />

C17<br />

2<br />

D18<br />

DDRA_SDQ15<br />

DDRB_SDQ16<br />

MB_DATA15<br />

MA_DATA15<br />

G17<br />

D20<br />

DDRA_SDQ16<br />

DDRB_SDQ17<br />

MB_DATA16<br />

MA_DATA16<br />

G18<br />

A21<br />

DDRA_SDQ17<br />

DDRB_SDQ18<br />

MB_DATA17<br />

MA_DATA17<br />

C19<br />

D24<br />

DDRA_SDQ18<br />

DDRB_SDQ19<br />

MB_DATA18<br />

MA_DATA18<br />

D22<br />

C25<br />

DDRA_SDQ19<br />

DDRB_SDQ20<br />

MB_DATA19<br />

MA_DATA19<br />

E20<br />

B20<br />

DDRA_SDQ20<br />

DDRB_SDQ21<br />

MB_DATA20<br />

MA_DATA20<br />

E18<br />

C20<br />

DDRA_SDQ21<br />

DDRB_SDQ22<br />

MB_DATA21<br />

MA_DATA21<br />

F18<br />

B24<br />

DDRA_SDQ22<br />

DDRB_SDQ23<br />

MB_DATA22<br />

MA_DATA22<br />

B22<br />

C24<br />

DDRA_SDQ23<br />

DDRB_SDQ24<br />

MB_DATA23<br />

MA_DATA23<br />

C23<br />

E23<br />

DDRA_SDQ24<br />

DDRB_SDQ25<br />

MB_DATA24<br />

MA_DATA24<br />

F20<br />

E24<br />

DDRA_SDQ25<br />

DDRB_SDQ26<br />

MB_DATA25<br />

MA_DATA25<br />

F22<br />

G25<br />

DDRA_SDQ26<br />

DDRB_SDQ27<br />

MB_DATA26<br />

MA_DATA26<br />

H24<br />

G26<br />

DDRA_SDQ27<br />

DDRB_SDQ28<br />

MB_DATA27<br />

MA_DATA27<br />

J19<br />

C26<br />

DDRA_SDQ28<br />

DDRB_SDQ29<br />

MB_DATA28<br />

MA_DATA28<br />

E21<br />

D26<br />

DDRA_SDQ29<br />

DDRB_SDQ30<br />

MB_DATA29<br />

MA_DATA29<br />

E22<br />

G23<br />

DDRA_SDQ30<br />

+1.5V<br />

+CPU_VDDR<br />

+CPU_VDDR<br />

DDRB_SDQ31<br />

MB_DATA30<br />

MA_DATA30<br />

H20<br />

G24<br />

DDRA_SDQ31<br />

JCPU1B<br />

DDRB_SDQ32<br />

MB_DATA31<br />

MA_DATA31<br />

H22<br />

AA24<br />

DDRA_SDQ32<br />

2 DDRB_SDQ33<br />

MB_DATA32<br />

MA_DATA32<br />

Y24<br />

Place them<br />

DDRA_SDQ33<br />

2<br />

1.5A<br />

VDDR: DDR3 under 1033MHz<br />

AA23<br />

DDRB_SDQ34<br />

MB_DATA33<br />

MA_DATA33<br />

AB24<br />

close to CPU<br />

D10<br />

DDRA_SDQ34<br />

VDDR1<br />

set to 0.9V to save power<br />

MEM:CMD/CTRL/CLK<br />

VDDR5<br />

W10<br />

AD24<br />

DDRB_SDQ35<br />

MB_DATA34<br />

MA_DATA34<br />

AB22<br />

R368<br />

DDRA_SDQ35<br />

within 1"<br />

C10<br />

VDDR2<br />

VDDR6<br />

AC10<br />

AE24<br />

DDRB_SDQ36<br />

MB_DATA35<br />

MA_DATA35<br />

AA21<br />

B10<br />

DDRA_SDQ36<br />

VDDR3<br />

VDDR7<br />

AB10<br />

AA26<br />

DDRB_SDQ37<br />

MB_DATA36<br />

MA_DATA36<br />

W22<br />

0_0402_5%<br />

AD10<br />

DDRA_SDQ37<br />

VDDR4<br />

VDDR8<br />

AA10<br />

AA25<br />

R4<br />

39.2_0402_1%<br />

DDRB_SDQ38<br />

MB_DATA37<br />

MA_DATA37<br />

W21<br />

DDRA_SDQ38<br />

MEMZP<br />

VDDR9<br />

A10<br />

AD26<br />

DDRB_SDQ39<br />

MB_DATA38<br />

MA_DATA38<br />

Y22<br />

1 2<br />

AF10<br />

DDRA_SDQ39<br />

MEMZN<br />

MEMZP<br />

AE25<br />

AE10<br />

VTT_SENSE<br />

DDRB_SDQ40<br />

DDRA_SDQ40<br />

MEMZN<br />

VDDR_SENSE<br />

Y10<br />

MB_DATA39<br />

MA_DATA39<br />

AA22<br />

1 2<br />

PAD<br />

T1<br />

AC22<br />

R5<br />

39.2_0402_1%<br />

DDRB_SDQ41<br />

MB_DATA40<br />

MA_DATA40<br />

Y20<br />

2<br />

AD22<br />

DDRA_SDQ41<br />

C588<br />

MEM_MA_RST#<br />

MEM_VREF<br />

DDRB_SDQ42<br />

MB_DATA41<br />

MA_DATA41<br />

AA20<br />

DDRA_SDQ42<br />

MEM_MA_RST#<br />

H16<br />

MA_RESET_L<br />

MEMVREF<br />

W17<br />

AE20<br />

DDRB_SDQ43<br />

MB_DATA42<br />

MA_DATA42<br />

AA18<br />

AF20<br />

DDRA_SDQ43<br />

10U_0805_10V4Z<br />

DDRA_ODT0<br />

MEM_MB_RST#<br />

DDRB_SDQ44<br />

MB_DATA43<br />

MA_DATA43<br />

AB18<br />

DDRA_SDQ44<br />

DDRA_ODT0<br />

T19<br />

DDRA_ODT1<br />

MA0_ODT0 MB_RESET_L<br />

B18<br />

MEM_MB_RST# <br />

@ 1 AF24<br />

DDRB_SDQ45<br />

MB_DATA44<br />

MA_DATA44<br />

AB21<br />

DDRA_SDQ45<br />

DDRA_ODT1<br />

V22<br />

MA0_ODT1<br />

AF23<br />

DDRB_ODT0<br />

DDRB_SDQ46<br />

MB_DATA45<br />

MA_DATA45<br />

AD21<br />

U21<br />

DDRA_SDQ46<br />

MA1_ODT0<br />

MB0_ODT0<br />

W26<br />

DDRB_ODT0 <br />

AC20<br />

DDRB_ODT1<br />

DDRB_SDQ47<br />

MB_DATA46<br />

MA_DATA46<br />

AD19<br />

V19<br />

DDRA_SDQ47<br />

MA1_ODT1<br />

MB0_ODT1<br />

W23<br />

DDRB_ODT1 <br />

AD20<br />

DDRB_SDQ48<br />

MB_DATA47<br />

MA_DATA47<br />

Y18<br />

DDRA_SDQ48<br />

DDRA_SCS0#<br />

MB1_ODT0<br />

Y26<br />

AD18<br />

DDRB_SDQ49<br />

MB_DATA48<br />

MA_DATA48<br />

AD17<br />

DDRA_SDQ49<br />

DDRA_SCS0#<br />

T20<br />

DDRA_SCS1#<br />

MA0_CS_L0<br />

AE18<br />

DDRB_SCS0#<br />

DDRB_SDQ50<br />

MB_DATA49<br />

MA_DATA49<br />

W16<br />

DDRA_SDQ50<br />

DDRA_SCS1#<br />

U19<br />

MA0_CS_L1<br />

MB0_CS_L0<br />

V26<br />

DDRB_SCS0# <br />

AC14<br />

DDRB_SCS1#<br />

DDRB_SDQ51<br />

MB_DATA50<br />

MA_DATA50<br />

W14<br />

U20<br />

DDRA_SDQ51<br />

MA1_CS_L0<br />

MB0_CS_L1<br />

W25<br />

DDRB_SCS1# <br />

AD14<br />

V20<br />

DDRB_SDQ52<br />

MB_DATA51<br />

MA_DATA51<br />

Y14<br />

DDRA_SDQ52<br />

MA1_CS_L1<br />

MB1_CS_L0<br />

U22<br />

AF19<br />

DDRB_SDQ53<br />

MB_DATA52<br />

MA_DATA52<br />

Y17<br />

AC18<br />

DDRA_SDQ53<br />

DDRA_CKE0<br />

DDRB_CKE0<br />

DDRB_SDQ54<br />

MB_DATA53<br />

MA_DATA53<br />

AB17<br />

DDRA_SDQ54<br />

DDRA_CKE0<br />

J22<br />

DDRB_CKE0 <br />

DDRA_CKE1<br />

MA_CKE0<br />

MB_CKE0<br />

J25<br />

AF16<br />

DDRB_CKE1<br />

DDRB_SDQ55<br />

MB_DATA54<br />

MA_DATA54<br />

AB15<br />

DDRA_SDQ55<br />

DDRA_CKE1<br />

J20<br />

MA_CKE1<br />

MB_CKE1<br />

H26<br />

DDRB_CKE1 <br />

AF15<br />

DDRB_SDQ56<br />

MB_DATA55<br />

MA_DATA55<br />

AD15<br />

AF13<br />

DDRA_SDQ56<br />

DDRA_CLK0<br />

DDRB_CLK0<br />

DDRB_SDQ57<br />

MB_DATA56<br />

MA_DATA56<br />

AB13<br />

DDRA_SDQ57<br />

DDRA_CLK0<br />

N19<br />

DDRB_CLK0 <br />

DDRA_CLK0#<br />

MA_CLK_H5<br />

MB_CLK_H5<br />

P22<br />

AC12<br />

DDRB_CLK0#<br />

DDRB_SDQ58<br />

MB_DATA57<br />

MA_DATA57<br />

AD13<br />

DDRA_SDQ58<br />

DDRA_CLK0#<br />

N20<br />

MA_CLK_L5<br />

MB_CLK_L5<br />

R22<br />

DDRB_CLK0# <br />

AB11<br />

E16<br />

DDRB_SDQ59<br />

MB_DATA58<br />

MA_DATA58<br />

Y12<br />

DDRA_SDQ59<br />

MA_CLK_H1<br />

MB_CLK_H1<br />

A17<br />

Y11<br />

F16<br />

DDRB_SDQ60<br />

MB_DATA59<br />

MA_DATA59<br />

W11<br />

DDRA_SDQ60<br />

MA_CLK_L1<br />

MB_CLK_L1<br />

A18<br />

AE14<br />

Y16<br />

DDRB_SDQ61<br />

MB_DATA60<br />

MA_DATA60<br />

AB14<br />

DDRA_SDQ61<br />

MA_CLK_H7<br />

MB_CLK_H7<br />

AF18<br />

AF14<br />

AA16<br />

DDRB_SDQ62<br />

MB_DATA61<br />

MA_DATA61<br />

AA14<br />

DDRA_SDQ62<br />

DDRA_CLK1<br />

MA_CLK_L7<br />

MB_CLK_L7<br />

AF17<br />

AF11<br />

DDRB_CLK1<br />

DDRB_SDQ63<br />

MB_DATA62<br />

MA_DATA62<br />

AB12<br />

DDRA_SDQ63<br />

DDRA_CLK1<br />

P19<br />

DDRB_CLK1 <br />

DDRA_CLK1#<br />

MA_CLK_H4<br />

MB_CLK_H4<br />

R26<br />

AD11<br />

DDRB_CLK1#<br />

MB_DATA63<br />

MA_DATA63<br />

AA12<br />

3 DDRA_CLK1#<br />

P20<br />

MA_CLK_L4<br />

MB_CLK_L4<br />

R25<br />

DDRB_CLK1# DDRB_SDM[7..0]<br />

DDRA_SDM[7..0] <br />

DDRB_SDM0<br />

DDRA_SDM0<br />

3<br />

DDRA_SMA[15..0]<br />

DDRB_SMA[15..0] <br />

A12<br />

DDRA_SMA0<br />

N21<br />

DDRB_SMA0<br />

DDRB_SDM1<br />

MB_DM0<br />

MA_DM0<br />

E12<br />

DDRA_SDM1<br />

DDRA_SMA1<br />

MA_ADD0<br />

MB_ADD0<br />

P24<br />

B16<br />

M20<br />

DDRB_SMA1<br />

DDRB_SDM2<br />

MB_DM1<br />

MA_DM1<br />

C15<br />

DDRA_SDM2<br />

DDRA_SMA2<br />

MA_ADD1<br />

MB_ADD1<br />

N24<br />

A22<br />

N22<br />

DDRB_SMA2<br />

DDRB_SDM3<br />

MB_DM2<br />

MA_DM2<br />

E19<br />

DDRA_SDM3<br />

DDRA_SMA3<br />

MA_ADD2<br />

MB_ADD2<br />

P26<br />

E25<br />

M19<br />

DDRB_SMA3<br />

DDRB_SDM4<br />

MB_DM3<br />

MA_DM3<br />

F24<br />

DDRA_SDM4<br />

DDRA_SMA4<br />

MA_ADD3<br />

MB_ADD3<br />

N23<br />

AB26<br />

M22<br />

DDRB_SMA4<br />

DDRB_SDM5<br />

MB_DM4<br />

MA_DM4<br />

AC24<br />

DDRA_SDM5<br />

DDRA_SMA5<br />

MA_ADD4<br />

MB_ADD4<br />

N26<br />

AE22<br />

L20<br />

DDRB_SMA5<br />

DDRB_SDM6<br />

MB_DM5<br />

MA_DM5<br />

Y19<br />

DDRA_SDM6<br />

DDRA_SMA6<br />

MA_ADD5<br />

MB_ADD5<br />

L23<br />

AC16<br />

M24<br />

DDRB_SMA6<br />

DDRB_SDM7<br />

MB_DM6<br />

MA_DM6<br />

AB16<br />

DDRA_SDM7<br />

DDRA_SMA7<br />

MA_ADD6<br />

MB_ADD6<br />

N25<br />

AD12<br />

L21<br />

DDRB_SMA7<br />

MB_DM7<br />

MA_DM7<br />

Y13<br />

DDRA_SMA8<br />

MA_ADD7<br />

MB_ADD7<br />

L24<br />

L19<br />

DDRB_SMA8<br />

DDRB_SDQS0<br />

DDRA_SDQS0<br />

DDRB_SDQS0<br />

DDRA_SDQS0 <br />

DDRA_SMA9<br />

MA_ADD8<br />

MB_ADD8<br />

M26<br />

C12<br />

K22<br />

DDRB_SMA9<br />

DDRB_SDQS0#<br />

MB_DQS_H0<br />

MA_DQS_H0<br />

G13<br />

DDRA_SDQS0#<br />

DDRB_SDQS0#<br />

DDRA_SDQS0# <br />

DDRA_SMA10<br />

MA_ADD9<br />

MB_ADD9<br />

K26<br />

B12<br />

R21<br />

DDRB_SMA10<br />

DDRB_SDQS1<br />

MB_DQS_L0<br />

MA_DQS_L0<br />

H13<br />

DDRA_SDQS1<br />

DDRB_SDQS1<br />

DDRA_SDQS1 <br />

DDRA_SMA11<br />

MA_ADD10<br />

MB_ADD10<br />

T26<br />

D16<br />

L22<br />

DDRB_SMA11<br />

DDRB_SDQS1#<br />

MB_DQS_H1<br />

MA_DQS_H1<br />

G16<br />

DDRA_SDQS1#<br />

DDRB_SDQS1#<br />

DDRA_SDQS1# <br />

DDRA_SMA12<br />

MA_ADD11<br />

MB_ADD11<br />

L26<br />

C16<br />

K20<br />

DDRB_SMA12<br />

DDRB_SDQS2<br />

MB_DQS_L1<br />

MA_DQS_L1<br />

G15<br />

DDRA_SDQS2<br />

DDRB_SDQS2<br />

DDRA_SDQS2 <br />

DDRA_SMA13<br />

MA_ADD12<br />

MB_ADD12<br />

L25<br />

A24<br />

V24<br />

DDRB_SMA13<br />

DDRB_SDQS2#<br />

MB_DQS_H2<br />

MA_DQS_H2<br />

C22<br />

DDRA_SDQS2#<br />

DDRB_SDQS2#<br />

DDRA_SDQS2# <br />

DDRA_SMA14<br />

MA_ADD13<br />

MB_ADD13<br />

W24<br />

A23<br />

K24<br />

DDRB_SMA14<br />

DDRB_SDQS3<br />

MB_DQS_L2<br />

MA_DQS_L2<br />

C21<br />

DDRA_SDQS3<br />

DDRB_SDQS3<br />

DDRA_SDQS3 <br />

DDRA_SMA15<br />

MA_ADD14<br />

MB_ADD14<br />

J23<br />

F26<br />

K19<br />

DDRB_SMA15<br />

DDRB_SDQS3#<br />

MB_DQS_H3<br />

MA_DQS_H3<br />

G22<br />

DDRA_SDQS3#<br />

MA_ADD15<br />

MB_ADD15<br />

J24<br />

DDRB_SDQS3#<br />

E26<br />

DDRA_SDQS3# <br />

DDRB_SDQS4<br />

MB_DQS_L3<br />

MA_DQS_L3<br />

G21<br />

DDRA_SDQS4<br />

DDRB_SDQS4<br />

AC25<br />

DDRA_SDQS4 <br />

DDRA_SBS0#<br />

DDRB_SBS0#<br />

DDRB_SDQS4#<br />

MB_DQS_H4<br />

MA_DQS_H4<br />

AD23<br />

DDRA_SDQS4#<br />

DDRA_SBS0#<br />

R20<br />

DDRB_SBS0# DDRB_SDQS4#<br />

DDRA_SDQS4# <br />

DDRA_SBS1#<br />

MA_BANK0<br />

MB_BANK0<br />

R24<br />

AC26<br />

DDRB_SBS1#<br />

DDRB_SDQS5<br />

MB_DQS_L4<br />

MA_DQS_L4<br />

AC23<br />

DDRA_SDQS5<br />

DDRA_SBS1#<br />

R23<br />

DDRB_SBS1# DDRB_SDQS5<br />

DDRA_SDQS5 <br />

DDRA_SBS2#<br />

MA_BANK1<br />

MB_BANK1<br />

U26<br />

AF21<br />

DDRB_SBS2#<br />

DDRB_SDQS5#<br />

MB_DQS_H5<br />

MA_DQS_H5<br />

AB19<br />

DDRA_SDQS5#<br />

DDRA_SBS2#<br />

J21<br />

MA_BANK2<br />

MB_BANK2<br />

J26<br />

DDRB_SBS2# DDRB_SDQS5#<br />

AF22<br />

DDRA_SDQS5# <br />

DDRB_SDQS6<br />

MB_DQS_L5<br />

MA_DQS_L5<br />

AB20<br />

DDRA_SDQS6<br />

DDRB_SDQS6<br />

AE16<br />

DDRA_SDQS6 <br />

DDRA_SRAS#<br />

DDRB_SRAS#<br />

DDRB_SDQS6#<br />

MB_DQS_H6<br />

MA_DQS_H6<br />

Y15<br />

DDRA_SDQS6#<br />

DDRA_SRAS#<br />

R19<br />

DDRB_SRAS# DDRB_SDQS6#<br />

DDRA_SDQS6# <br />

DDRA_SCAS#<br />

MA_RAS_L<br />

MB_RAS_L<br />

U25<br />

AD16<br />

DDRB_SCAS#<br />

DDRB_SDQS7<br />

MB_DQS_L6<br />

MA_DQS_L6<br />

W15<br />

DDRA_SDQS7<br />

DDRA_SCAS#<br />

T22<br />

DDRB_SCAS# DDRB_SDQS7<br />

DDRA_SDQS7 <br />

DDRA_SWE#<br />

MA_CAS_L<br />

MB_CAS_L<br />

U24<br />

AF12<br />

DDRB_SWE#<br />

DDRB_SDQS7#<br />

MB_DQS_H7<br />

MA_DQS_H7<br />

W12<br />

DDRA_SDQS7#<br />

DDRA_SWE#<br />

T24<br />

MA_WE_L<br />

MB_WE_L<br />

U23<br />

DDRB_SWE# DDRB_SDQS7#<br />

AE12<br />

MB_DQS_L7<br />

MA_DQS_L7<br />

W13<br />

DDRA_SDQS7# <br />

1 2<br />

1 2<br />

1 2<br />

C9<br />

0.01U_0402_25V7K<br />

C8<br />

1000P_0402_50V7K<br />

www.mycomp.su<br />

FOX_PZ6382A-284S-41F_Champlian<br />

CONN@<br />

FOX_PZ6382A-284S-41F_Champlian<br />

CONN@<br />

4 4<br />

A<br />

B<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2010/03/12<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

Custom<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 7 of<br />

55<br />

C<br />

D<br />

E

A<br />

B<br />

C<br />

D<br />

E<br />

+2.5VS<br />

+2.5VDDA<br />

VDDA=0.25A<br />

Champlain: C1E<br />

C1E: LDT_REQ# no connect<br />

CLMC: LDT_REQ# connect to NB<br />

1<br />

FBMA-L11-201209-221LMA30T_0805 1<br />

1<br />

1<br />

LDT_RES# / MEMHOT#<br />

+ C11<br />

4.7U_0805_10V4Z<br />

C12<br />

C13<br />

C14<br />

no support in S1g4<br />

R6<br />

change to SGA00002N80<br />

150U_B_6.3VM_R40M<br />

0.22U_0603_16V4Z<br />

2<br />

2<br />

2<br />

R7<br />

10K_0402_5%<br />

2<br />

JCPU1D<br />

1K_0402_5%<br />

1 1<br />

Q1<br />

F8<br />

CPU_THERMTRIP#_R<br />

VDDA1<br />

VSS<br />

M11<br />

3 1<br />

1 2<br />

H_THERMTRIP# <br />

F9<br />

VDDA2<br />

RSVD11<br />

W18<br />

R8<br />

0_0402_5%<br />

MMBT3904_NL_SOT23-3<br />

CLK_CPU_BCLK<br />

1 2<br />

3900P_0402_50V7K<br />

CPU_CLKIN_SC_P<br />

A9<br />

CPU_SVC<br />

C16<br />

CPU_CLKIN_SC_N<br />

CLKIN_H<br />

SVC<br />

A6<br />

CPU_SVD<br />

CPU_SVC <br />

1 2<br />

A8<br />

SVD<br />

A4<br />

R9<br />

@<br />

0_0402_5%<br />

CLKIN_L<br />

CPU_SVD <br />

MAINPWON <br />

LDT_RST#<br />

B7<br />

+1.5V<br />

H_PWRGD<br />

RESET_L<br />

1 2<br />

R10<br />

A7<br />

R11<br />

300_0402_5%<br />

169_0402_1%<br />

LDT_STOP#<br />

PWROK<br />

F10<br />

CPU_THERMTRIP#_R<br />

LDTSTOP_L THERMTRIP_L<br />

AF6<br />

H_PROCHOT#<br />

T2<br />

PAD<br />

C6<br />

LDTREQ_L PROCHOT_L<br />

AC7<br />

CLK_CPU_BCLK#<br />

1 2<br />

+1.5V<br />

CPU_SIC<br />

MEMHOT_L<br />

AA8<br />

PAD<br />

T3<br />

C15<br />

3900P_0402_50V7K<br />

1 2<br />

AF4<br />

H_PROCHOT#<br />

H_PROCHOT_R# <br />

+1.5V<br />

1 2<br />

CPU_SID<br />

SIC<br />

1 2<br />

R12<br />

1K_0402_5%<br />

AF5<br />

R13<br />

0_0402_5%<br />

R14<br />

1K_0402_5%<br />

SID<br />

AE6<br />

THERMDC_CPU<br />

+1.5VS<br />

ALERT_L<br />

THERMDC<br />

W7<br />

THERMDA_CPU<br />

PROCHOT:<br />

CPU_HTREF0<br />

THERMDA<br />

W8<br />

R15 1 2<br />

44.2_0402_1%<br />

R6<br />

+1.1VS<br />

R16 1 2<br />

44.2_0402_1% CPU_HTREF1<br />

HT_REF0<br />

P6<br />

Input: For HTC Function<br />

HT_REF1<br />

Output: Over Temperature Condition<br />

R17<br />

CPU_VDD0_FB_H<br />

CPU_VDD0_FB_H F6<br />

CPU_VDD0_FB_L<br />

CPU_VDD0_FB_L<br />

VDD0_FB_H VDDIO_FB_H<br />

W9<br />

300_0402_5%<br />

E6<br />

VDD0_FB_L VDDIO_FB_L<br />

Y9<br />

CPU_VDD1_FB_H<br />

CPU_VDD1_FB_H Y6<br />

CPU_VDDNB_FB_H<br />

CPU_VDDNB_FB_H <br />

LDT_RST#<br />

CPU_VDD1_FB_L<br />

VDD1_FB_H VDDNB_FB_H<br />

H6<br />

CPU_VDDNB_FB_L<br />

LDT_RST#<br />

CPU_VDD1_FB_L<br />

AB6<br />

VDD1_FB_L VDDNB_FB_L<br />

G6<br />

CPU_VDDNB_FB_L <br />

+1.5VS<br />

1<br />

CPU_DBRDY<br />

G10<br />

C17<br />

CPU_TMS<br />

DBRDY<br />

AA9<br />

CPU_DBREQ#<br />

CPU_TCK<br />

TMS<br />

DBREQ_L<br />

E10<br />

0.01U_0402_25V4Z<br />

AC9<br />

@<br />

CPU_TRST#<br />

TCK<br />

AD9<br />

CPU_TDO<br />

2<br />

R18<br />

CPU_TDI<br />

TRST_L<br />

TDO<br />

AE9<br />

AF9<br />

TDI<br />

300_0402_5%<br />

+1.5V<br />

CPU_TEST23 AD7<br />

TEST23<br />

TEST28_H<br />

J7<br />

LDT_STOP#<br />

CPU_TEST18<br />

TEST28_L<br />

H8<br />

CPU_SVC<br />

+1.5VS LDT_STOP#<br />

H10<br />

CPU_TEST19<br />

TEST18<br />

1 2<br />

G9<br />

CPU_TEST17<br />

TEST19<br />

TEST17<br />

D7<br />

R19<br />

1K_0402_5%<br />

PAD<br />

T5<br />

1<br />

CPU_TEST16<br />

CPU_SVD<br />

CPU_TEST25H<br />

TEST16<br />

E7<br />

PAD<br />

T6<br />

1 2<br />

C18<br />

E9<br />

CPU_TEST15<br />

CPU_TEST25L<br />

TEST25_H<br />

TEST15<br />

F7<br />

R20<br />

1K_0402_5%<br />

PAD<br />

T7<br />

0.01U_0402_25V4Z<br />

E8<br />

CPU_TEST14<br />

R21<br />

TEST25_L<br />

TEST14<br />

C7<br />

PAD<br />

T8<br />

@<br />

2 2<br />

2<br />

300_0402_5%<br />

CPU_TEST21 AB8<br />

+1.5V<br />

CPU_TEST20<br />

TEST21<br />

TEST7<br />

C3<br />

AF7<br />

CPU_TEST24<br />

TEST20<br />

TEST10<br />

K8<br />

AE7<br />

CPU_TEST25H 1 2<br />

H_PWRGD<br />

CPU_TEST22<br />

TEST24<br />

R22<br />

510_0402_5%<br />

H_PWRGD<br />

AE8<br />

CPU_TEST12<br />

TEST22<br />

TEST8<br />

C4<br />

AC8<br />

CPU_TEST27<br />

TEST12<br />

1 2<br />

1<br />

AF8<br />

R23<br />

@<br />

510_0402_5%<br />

C19<br />

TEST27<br />

CPU_TEST29_H_FBCLKOUT_P<br />

+1.5V<br />

0.01U_0402_25V4Z<br />

TEST29_H<br />

C9<br />

1 2<br />

C2<br />

CPU_TEST29_L_FBCLKOUT_N<br />

TEST9<br />

TEST29_L<br />

C8<br />

2 1<br />

@<br />

R24<br />

0_0402_5% AA6<br />

R25<br />

80.6_0402_1%<br />

CPU_TEST25L<br />

2<br />

TEST6<br />

1 2<br />

R26<br />

@<br />

510_0402_5%<br />

+3VS<br />

A3<br />

RSVD1<br />

RSVD10<br />

H18<br />

1 2<br />

A5<br />

R27<br />

510_0402_5%<br />

RSVD2<br />

RSVD9<br />

H19<br />

B3<br />

RSVD3<br />

RSVD8<br />

AA7<br />

B5<br />

RSVD4<br />

RSVD7<br />

D5<br />

C1<br />

RSVD5<br />

RSVD6<br />

C5<br />

+1.5V<br />

1<br />

FOX_PZ6382A-284S-41F_Champlian<br />

CONN@<br />

C20<br />

CPU_TEST27 1 2<br />

R28<br />

1K_0402_5%<br />

2<br />

U1<br />

@<br />

1<br />

VDD SCLK 8 EC_SMB_CK2<br />

EC_SMB_CK2 <br />

0.1U_0402_16V4Z<br />

1 2<br />

1 2<br />

1 2<br />

1<br />

2<br />

L1<br />

1 2<br />

THERMDA_CPU 2<br />

D+ SDATA<br />

7 EC_SMB_DA2<br />

EC_SMB_DA2 <br />

3 3<br />

THERMDC_CPU 3<br />

CPU_TEST12<br />

D- ALERT#<br />

6<br />

1 2<br />

1 R29<br />

2<br />

1K_0402_5%<br />

4<br />

CPU_TEST18 1 2<br />

C21<br />

THERM# GND 5<br />

R30<br />

1K_0402_5%<br />

100P_0402_50V8J<br />

CPU_TEST19 1 2<br />

@<br />

ADM1032ARMZ_MSOP8<br />

R31<br />

1K_0402_5%<br />

+1.5V<br />

CPU_TEST20 1 2<br />

Address 1001 100X b<br />

R32<br />

1K_0402_5%<br />

CPU_TEST21 1 2<br />

R33<br />

1K_0402_5%<br />

CPU_TEST22 1 2<br />

R34<br />

1K_0402_5%<br />

CPU internal thermal sensor<br />

CPU_TEST24 1 2<br />

R35<br />

1K_0402_5%<br />

CPU_TEST23 1 2<br />

1 2<br />

FDV301N, the Vgs is:<br />

R265<br />

1K_0402_5%<br />

JP2<br />

min = 0.65V<br />

C22<br />

0.1U_0402_16V4Z<br />

Typ = 0.85V<br />

@<br />

@<br />

@<br />

@<br />

1 2<br />

R41<br />

R42<br />

3 4<br />

Max = 1.5V<br />

5 6<br />

CPU_DBREQ#<br />

+3VS 2 1 2 1<br />

R43<br />

CPU_DBRDY<br />

7 8<br />

1 2<br />

@<br />

0_0402_5%<br />

31.6K_0402_1%<br />

30K_0402_1%<br />

CPU_TCK<br />

9 10<br />

11 12<br />

CPU_TMS<br />

+3VS<br />

13 14<br />

CPU_TDI<br />

15 16<br />

2.09V for Gate<br />

CPU_TRST#<br />

Q2<br />

CPU_TDO<br />

17 18<br />

U2<br />

@<br />

19 20<br />

LDT_RST#<br />

CPU_SID<br />

EC_SMB_DA<br />

SB_SID<br />

21 22<br />

HDT_RST#<br />

B<br />

SB_SID T0 SB<br />

3 1<br />

1 2<br />

4<br />

R44<br />

0_0402_5%<br />

23 24<br />

Y<br />

SB_PWRGD <br />

EC_SMB_DA2<br />

26<br />

A<br />

TO EC<br />

1 2<br />

4 4<br />

BSH111 1N_SOT23-3<br />

R45<br />

0_0402_5%<br />

NC7SZ08P5X_NL_SC70-5<br />

CONN@<br />

SAMTEC_ASP-68200-07<br />

S<br />

G<br />

2<br />

D<br />

3300P_0402_50V7K<br />

www.mycomp.su<br />

1<br />

2<br />

220_0402_5% R36<br />

1<br />

2<br />

220_0402_5% R37<br />

1<br />

2<br />

220_0402_5% R38<br />

1<br />

2<br />

300_0402_5% R39<br />

1 2<br />

300_0402_5%<br />

R40<br />

5<br />

P<br />

G<br />

3<br />

1 2<br />

E<br />

+1.5V<br />

1<br />

2<br />

B<br />

2<br />

C<br />

For SCAN connect use<br />

CPU_SIC 3<br />

S<br />

G<br />

2<br />

Q3<br />

1<br />

D<br />

BSH111 1N_SOT23-3<br />

A<br />

EC_SMB_CK<br />

@<br />

1 2<br />

SB_SIC<br />

R46<br />

0_0402_5%<br />

1 2 EC_SMB_CK2<br />

R47<br />

0_0402_5%<br />

B<br />

SB_SIC <br />

T0 SB<br />

TO EC<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2010/03/12<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

Custom<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 8 of<br />

55<br />

C<br />

D<br />

E

A<br />

B<br />

C<br />

D<br />

E<br />

VDD(+CPU_CORE) decoupling.<br />

+CPU_CORE<br />

JCPU1E<br />

AA4<br />

+CPU_CORE<br />

VSS1<br />

VSS66<br />

J6<br />

AA11<br />

VSS2<br />

VSS67<br />

J8<br />

36A<br />

AA13<br />

VSS3<br />

VSS68<br />

J10<br />

G4<br />

VDD0_1 VDD1_1<br />

P8<br />

AA15<br />

VSS4<br />

VSS69<br />

J12<br />

H2<br />

+CPU_CORE<br />

VDD0_2 VDD1_2<br />

P10<br />

AA17<br />

VSS5<br />

VSS70<br />

J14<br />

J9<br />

VDD0_3 VDD1_3<br />

R4<br />

AA19<br />

VSS6<br />

VSS71<br />

J16<br />

J11<br />

VDD0_4 VDD1_4<br />

R7<br />

AB2<br />

VSS7<br />

VSS72<br />

J18<br />

J13<br />

VDD0_5 VDD1_5<br />

R9<br />

AB7<br />

VSS8<br />

VSS73<br />

K2<br />

J15<br />

VDD0_6 VDD1_6<br />

R11<br />

AB9<br />

VSS9<br />

VSS74<br />

K7<br />

1<br />

1<br />

1<br />

1<br />

1<br />

K6<br />

VDD0_7 VDD1_7<br />

T2<br />

AB23<br />

VSS10<br />

VSS75<br />

K9<br />

K10<br />

VDD0_8 VDD1_8<br />

T6<br />

AB25<br />

+ C23<br />

+ C24<br />

+ C25<br />

+ C26<br />

+ C27<br />

VSS11<br />

VSS76<br />

K11<br />

K12<br />

1 VDD0_9 VDD1_9<br />

T8<br />

AC11<br />

330U_X_2VM_R6M<br />

330U_X_2VM_R6M<br />

330U_X_2VM_R6M<br />

330U_X_2VM_R6M<br />

330U_X_2VM_R6M<br />

VSS12<br />

VSS77<br />

K13<br />

1<br />

K14<br />

VDD0_10 VDD1_10<br />

T10<br />

AC13<br />

@<br />

VSS13<br />

VSS78<br />

K15<br />

L4<br />

VDD0_11 VDD1_11<br />

T12<br />

AC15<br />

2<br />

2<br />

2<br />

2<br />

2<br />

VSS14<br />

VSS79<br />

K17<br />

L7<br />

VDD0_12 VDD1_12<br />

T14<br />

AC17<br />

VSS15<br />

VSS80<br />

L6<br />

L9<br />

VDD0_13 VDD1_13<br />

U7<br />

AC19<br />

VSS16<br />

VSS81<br />

L8<br />

L11<br />

Near CPU Socket<br />

VDD0_14 VDD1_14<br />

U9<br />

AC21<br />

VSS17<br />

VSS82<br />

L10<br />

L13<br />

VDD0_15 VDD1_15<br />

U11<br />

AD6<br />

VSS18<br />

VSS83<br />

L12<br />

L15<br />

VDD0_16 VDD1_16<br />

U13<br />

AD8<br />

VSS19<br />

VSS84<br />

L14<br />

M2<br />

VDD0_17 VDD1_17<br />

U15<br />

AD25<br />

VSS20<br />

VSS85<br />

L16<br />

M6<br />

VDD0_18 VDD1_18<br />

V6<br />

AE11<br />

VSS21<br />

VSS86<br />

L18<br />

M8<br />

+CPU_CORE<br />

VDD0_19 VDD1_19<br />

V8<br />

AE13<br />

VSS22<br />

VSS87<br />

M7<br />

M10<br />

+CPU_CORE<br />

VDD0_20 VDD1_20<br />

V10<br />

AE15<br />

VSS23<br />

VSS88<br />

M9<br />

N7<br />

VDD0_21 VDD1_21<br />

V12<br />

AE17<br />

VSS24<br />

VSS89<br />

AC6<br />

N9<br />

+CPU_CORE_NB<br />

VDD0_22 VDD1_22<br />

V14<br />

AE19<br />

VSS25<br />

VSS90<br />

M17<br />

N11<br />

VDD0_23 VDD1_23<br />

W4<br />

AE21<br />

VSS26<br />

VSS91<br />

N4<br />

1<br />

1<br />

1<br />

1<br />

4A<br />

VDD1_24<br />

Y2<br />

AE23<br />

C28<br />

C29<br />

C30<br />

C35<br />

VSS27<br />

VSS92<br />

N8<br />

1<br />

1<br />

1<br />

1<br />

K16<br />

VDDNB_1 VDD1_25<br />

AC4<br />

B4<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

C31<br />

C32<br />

C33<br />

C34<br />

M16<br />

+1.5V<br />

VSS28<br />

VSS93<br />

N10<br />

VDDNB_2 VDD1_26<br />

AD2<br />

B6<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

VSS29<br />

VSS94<br />

N16<br />

P16<br />

2<br />

2<br />

2<br />

2<br />

VDDNB_3<br />

TBD<br />

B8<br />

VSS30<br />

VSS95<br />

N18<br />

T16<br />

+1.5V<br />

VDDNB_4 VDDIO27<br />

Y25<br />

B9<br />

2<br />

2<br />

2<br />

2<br />

VSS31<br />

VSS96<br />

P2<br />

V16<br />

VDDNB_5 VDDIO26<br />

V25<br />

B11<br />

VSS32<br />

VSS97<br />

P7<br />

+CPU_CORE<br />

VDDIO25<br />

V23<br />

B13<br />

VSS33<br />

VSS98<br />

P9<br />

H25<br />

+CPU_CORE<br />

VDDIO1 VDDIO24<br />

V21<br />

B15<br />

VSS34<br />

VSS99<br />

P11<br />

J17<br />

VDDIO2 VDDIO23<br />

V18<br />

B17<br />

VSS35<br />

VSS100<br />

P17<br />

K18<br />

VDDIO3 VDDIO22<br />

U17<br />

B19<br />

VSS36<br />

VSS101<br />

R8<br />

K21<br />

VDDIO4 VDDIO21<br />

T25<br />

B21<br />

VSS37<br />

VSS102<br />

R10<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

K23<br />

VDDIO5 VDDIO20<br />

T23<br />

B23<br />

C36<br />

C37<br />

C38<br />

C39<br />

C41<br />

VSS38<br />

VSS103<br />

R16<br />

C40<br />

K25<br />

VDDIO6 VDDIO19<br />

T21<br />

B25<br />

0.22U_0603_16V4Z<br />

0.01U_0402_25V4Z<br />

180P_0402_50V8J<br />

0.22U_0603_16V4Z<br />

180P_0402_50V8J<br />

VSS39<br />

VSS104<br />

R18<br />

0.01U_0402_25V4Z<br />

L17<br />

VDDIO7 VDDIO18<br />

T18<br />

D6<br />

VSS40<br />

VSS105<br />

T7<br />

M18<br />

VDDIO8 VDDIO17<br />

R17<br />

D8<br />

2<br />

2<br />

2<br />

2<br />

2<br />

VSS41<br />

VSS106<br />

T9<br />

2<br />

M21<br />

VDDIO9 VDDIO16<br />

P25<br />

D9<br />

VSS42<br />

VSS107<br />

T11<br />

M23<br />

Under CPU Socket<br />

VDDIO10 VDDIO15<br />

P23<br />

D11<br />

VSS43<br />

VSS108<br />

T13<br />

M25<br />

2 VDDIO11 VDDIO14<br />

P21<br />

D13<br />

VSS44<br />

VSS109<br />

T15<br />

2<br />

N17<br />

VDDIO12 VDDIO13<br />

P18<br />

D15<br />

VSS45<br />

VSS110<br />

T17<br />

D17<br />

VSS46<br />

VSS111<br />

U4<br />

D19<br />

FOX_PZ6382A-284S-41F_Champlian<br />

VSS47<br />

VSS112<br />

U6<br />

D21<br />

Athlon 64 S1<br />

CONN@<br />

VSS48<br />

VSS113<br />

U8<br />

D23<br />

Processor Socket<br />

VSS49<br />

VSS114<br />

U10<br />

VDDIO decoupling.<br />

D25<br />

VSS50<br />

VSS115<br />

U12<br />

E4<br />

VSS51<br />

VSS116<br />

U14<br />

F2<br />

VSS52<br />

VSS117<br />

U16<br />

+CPU_CORE_NB decoupling.<br />

F11<br />

VSS53<br />

VSS118<br />

U18<br />

F13<br />

+1.5V<br />

VSS54<br />

VSS119<br />

V2<br />

F15<br />

VSS55<br />

VSS120<br />

V7<br />

F17<br />

+CPU_CORE_NB<br />

VSS56<br />

VSS121<br />

V9<br />

F19<br />

VSS57<br />

VSS122<br />

V11<br />

F21<br />

VSS58<br />

VSS123<br />

V13<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

F23<br />

C44<br />

C45<br />

C46<br />

C47<br />

C48<br />

VSS59<br />

VSS124<br />

V15<br />

C50<br />

1<br />

1<br />

1<br />

F25<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

C42<br />

C43<br />

C49<br />

VSS60<br />

VSS125<br />

V17<br />

H7<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

180P_0402_50V8J<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

22U_0805_6.3V6M<br />

VSS61<br />

VSS126<br />

W6<br />

180P_0402_50V8J<br />

H9<br />

2<br />

2<br />

2<br />

2<br />

2<br />

VSS62<br />

VSS127<br />

Y21<br />

2<br />

H21<br />

2<br />

2<br />

2<br />

VSS63<br />

VSS128<br />

Y23<br />

H23<br />

VSS64<br />

VSS129<br />

N6<br />

J4<br />

VSS65<br />

FOX_PZ6382A-284S-41F_Champlian<br />

Under CPU Socket<br />

Athlon 64 S1<br />

CONN@<br />

Processor Socket<br />

+1.5V<br />

Between CPU Socket and DIMM<br />

+1.5V<br />

+CPU_VDDR<br />

Near Power Supply<br />

VDDR decoupling.<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

3 3<br />

C51<br />

C52<br />

C53<br />

C54<br />

C354<br />

C355<br />

C55<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

+ C56<br />

22U_0805_6.3V6M<br />

change to SGA00002N80<br />

150U_B_6.3VM_R40M<br />

2<br />

2<br />

2<br />

2<br />

2<br />

2<br />

2<br />

2<br />

1<br />

1<br />

C64<br />

C65<br />

0.01U_0402_25V4Z<br />

0.01U_0402_25V4Z<br />

2<br />

2<br />

+1.5V<br />

180PF Qt'y follow the distance between<br />

CPU socket and DIMM0. <br />

2<br />

2<br />

1<br />

C68<br />

C66<br />

C67<br />

180P_0402_50V8J<br />

1<br />

0.1U_0402_16V7K<br />

1<br />

0.1U_0402_16V7K<br />

2<br />

+CPU_VDDR<br />

www.mycomp.su<br />

1<br />

C69<br />

1<br />

180P_0402_50V8J<br />

C57<br />

4.7U_0805_10V4Z<br />

2<br />

2<br />

1<br />

C58<br />

4.7U_0805_10V4Z<br />

2<br />

1<br />

1<br />

1<br />

1<br />

1<br />

C59<br />

0.22U_0603_16V4Z<br />

C60<br />

0.22U_0603_16V4Z<br />

C61<br />

1000P_0402_50V7K<br />

C62<br />

1000P_0402_50V7K<br />

C63<br />

180P_0402_50V8J<br />

2<br />

2<br />

2<br />

2<br />

2<br />

JCPU1F<br />

1<br />

C70<br />

180P_0402_50V8J<br />

2<br />

+1.5V<br />

1<br />

1<br />

1<br />

1<br />

1<br />

+ C75<br />

C71<br />

C72<br />

C73<br />

C74<br />

330U_X_2VM_R6M<br />

4.7U_0805_10V4Z<br />

4.7U_0805_10V4Z<br />

4.7U_0805_10V4Z<br />

4.7U_0805_10V4Z<br />

2<br />

2<br />

2<br />

2<br />

2<br />

Near CPU Socket Right side.<br />

+CPU_VDDR<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

1<br />

C76<br />

C77<br />

C78<br />

C79<br />

C80<br />

C81<br />

C82<br />

C83<br />

4.7U_0805_10V4Z<br />

4.7U_0805_10V4Z<br />

0.22U_0603_16V4Z<br />

0.22U_0603_16V4Z<br />

1000P_0402_50V7K<br />

1000P_0402_50V7K<br />

180P_0402_50V8J<br />

180P_0402_50V8J<br />

2<br />

2<br />

2<br />

2<br />

2<br />

2<br />

2<br />

2<br />

4 4<br />

Near CPU Socket Left side.<br />

A<br />

B<br />

Security Classification<br />

<strong>Compal</strong> Secret Data<br />

Issued Date<br />

2008/10/06 Deciphered Date<br />

2010/03/12<br />

Title<br />

<strong>Compal</strong> Electronics, Inc.<br />

SCHEMATIC, MB A5911<br />

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL<br />

Size AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F<strong>ROM</strong> THE CUSTODY OF THE COMPETENT DIVISION OF Document Number Rev<br />

R&D<br />

Custom<br />

401827<br />

D<br />

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS<br />

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.<br />

Date: Tuesday, September 14, 2010<br />

Sheet 9 of<br />

55<br />

C<br />

D<br />

E

A<br />

B<br />

C<br />

D<br />

E<br />

+VREF_DQ<br />

+1.5V<br />

+1.5V<br />

JDIMM1<br />

1<br />

VREF_DQ VSS1<br />

2<br />

3<br />

DDRA_SDQ4<br />

DDRA_SDQ0<br />

VSS2<br />

DQ4<br />

4<br />

5<br />

DDRA_SDQ5<br />

DDRA_SDQ1<br />

DQ0<br />

DQ5<br />

6<br />

7<br />

DQ1<br />

VSS3<br />

8<br />

9<br />

DDRA_SDQS0#<br />

DDRA_SDM0<br />

VSS4<br />

DQS#0<br />

10<br />

DDRA_SDQS0# <br />

11<br />

DDRA_SDQS0<br />

DM0<br />

DQS0<br />

12<br />

DDRA_SDQS0 <br />

13<br />

DDRA_SDQ[0..63]<br />

DDRA_SDQ2<br />

VSS5<br />

VSS6<br />

14<br />

DDRA_SDQ6<br />

DDRA_SDQ[0..63] <br />

15<br />

DDRA_SDQ3<br />

DQ2<br />

DQ6<br />

16<br />

17<br />

DDRA_SDQ7<br />

DDRA_SDM[0..7]<br />

DQ3<br />

DQ7<br />

18<br />

DDRA_SDM[0..7] <br />

19<br />

1 DDRA_SDQ8<br />

VSS7<br />

VSS8<br />

20<br />

DDRA_SDQ12<br />

1<br />

21<br />

DDRA_SDQ9<br />

DQ8<br />

DQ12<br />

22<br />

23<br />

DDRA_SDQ13<br />

DQ9<br />

DQ13<br />

24<br />

25<br />

DDRA_SMA[0..15]<br />

DDRA_SMA[0..15] <br />

DDRA_SDQS1#<br />

VSS9<br />

VSS10<br />

26<br />

DDRA_SDM1<br />

DDRA_SDQS1#<br />

27<br />

DDRA_SDQS1<br />

DQS#1<br />

DM1<br />

28<br />

MEM_MA_RST#<br />

DDRA_SDQS1<br />

29<br />

DQS1 RESET#<br />

30<br />

MEM_MA_RST# <br />

31<br />

DDRA_SDQ10<br />

VSS11 VSS12<br />

32<br />

33<br />

DDRA_SDQ14<br />

DDRA_SDQ11<br />

DQ10<br />

DQ14<br />

34<br />

35<br />

DDRA_SDQ15<br />

DQ11<br />

DQ15<br />

36<br />

37<br />

DDRA_SDQ16<br />

VSS13 VSS14<br />

38<br />

39<br />

DDRA_SDQ20<br />

DDRA_SDQ17<br />

DQ16<br />

DQ20<br />

40<br />

41<br />

DDRA_SDQ21<br />

DQ17<br />

DQ21<br />

42<br />

43<br />

DDRA_SDQS2#<br />

VSS15 VSS16<br />

44<br />

DDRA_SDM2<br />

DDRA_SDQS2#<br />

45<br />

DDRA_SDQS2<br />

DQS#2<br />

DM2<br />

46<br />

DDRA_SDQS2<br />

47<br />

DQS2<br />

VSS17<br />

48<br />

49<br />

DDRA_SDQ22<br />

DDRA_SDQ18<br />

VSS18<br />

DQ22<br />

50<br />

51<br />

DDRA_SDQ23<br />

DDRA_SDQ19<br />

DQ18<br />

DQ23<br />

52<br />

53<br />

DQ19<br />

VSS19<br />

54<br />

55<br />

DDRA_SDQ28<br />

DDRA_SDQ24<br />

VSS20<br />

DQ28<br />

56<br />

57<br />

DDRA_SDQ29<br />

+VREF_CA<br />

+1.5V<br />

DDRA_SDQ25<br />

DQ24<br />

DQ29<br />

58<br />

59<br />

+VREF_DQ<br />

+1.5V<br />

DQ25<br />

VSS21<br />

60<br />

61<br />

DDRA_SDQS3#<br />

DDRA_SDQS3# <br />

DDRA_SDM3<br />

VSS22 DQS#3<br />

62<br />

63<br />

DDRA_SDQS3<br />

DM3<br />

DQS3<br />

64<br />

DDRA_SDQS3 <br />

65<br />

R310<br />

DDRA_SDQ26<br />

VSS23 VSS24<br />

66<br />

67<br />

DDRA_SDQ30<br />

R48<br />

1K_0402_1%<br />

DDRA_SDQ27<br />

DQ26<br />

DQ30<br />

68<br />

69<br />

DDRA_SDQ31<br />

1K_0402_1%<br />

DQ27<br />

DQ31<br />

70<br />

71<br />

VSS25 VSS26<br />

72<br />

+VREF_CA<br />

+VREF_DQ<br />

DDRA_CKE0<br />

DDRA_CKE1<br />

DDRA_CKE0<br />

73<br />

CKE0<br />

CKE1<br />

74<br />

DDRA_CKE1 <br />

75<br />

VDD1<br />

VDD2<br />

76<br />

1<br />

2<br />

1<br />

77<br />

DDRA_SMA15<br />

1<br />

2 1<br />

C235<br />

C680<br />

DDRA_SBS2#<br />

NC1<br />

A15<br />

78<br />

C351<br />

DDRA_SMA14<br />

DDRA_SBS2#<br />

79<br />

C84<br />

C85<br />

C10<br />

@<br />

R315<br />

BA2<br />

A14<br />

80<br />

81<br />

@<br />

R49<br />

1K_0402_1%<br />

DDRA_SMA12<br />

VDD3<br />

VDD4<br />

82<br />

DDRA_SMA11<br />

1K_0402_1%<br />

2<br />

1<br />

2<br />

83<br />

DDRA_SMA9<br />

A12/BC#<br />