Algorithm and VLSI Architecture for Linear MMSE Detection in MIMO ...

Algorithm and VLSI Architecture for Linear MMSE Detection in MIMO ...

Algorithm and VLSI Architecture for Linear MMSE Detection in MIMO ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Algorithm</strong> <strong>and</strong> <strong>VLSI</strong> <strong>Architecture</strong> <strong>for</strong> <strong>L<strong>in</strong>ear</strong><br />

<strong>MMSE</strong> <strong>Detection</strong> <strong>in</strong> <strong>MIMO</strong>-OFDM Systems<br />

A. Burg, S. Haene, D. Perels, P. Luethi, N. Felber <strong>and</strong> W. Fichtner<br />

Integrated Systems Laboratory, ETH Zurich, Switzerl<strong>and</strong><br />

{ apburg,haene,perels,luethi,felber,fw } @iis.ee.ethz.ch<br />

Abstract- The paper describes an algorithm <strong>and</strong> a correspond<strong>in</strong>g<br />

<strong>VLSI</strong> architecture <strong>for</strong> the implementation of l<strong>in</strong>ear <strong>MMSE</strong> Idle Dtat Idle<br />

detection <strong>in</strong> packet-based <strong>MIMO</strong>-OFDM communication systems.<br />

The advantages of the presented receiver architecture are<br />

low latency, high-throughput, <strong>and</strong> efficient resource utilization,<br />

s<strong>in</strong>ce the hardware required <strong>for</strong> the computation of the <strong>MMSE</strong><br />

estimators is reused <strong>for</strong> the detection. The algorithm also supports<br />

the extraction of soft <strong>in</strong><strong>for</strong>mation <strong>for</strong> channel decod<strong>in</strong>g.<br />

Data frame<br />

<strong>Detection</strong> latency<br />

<strong>MIMO</strong> detectioni<br />

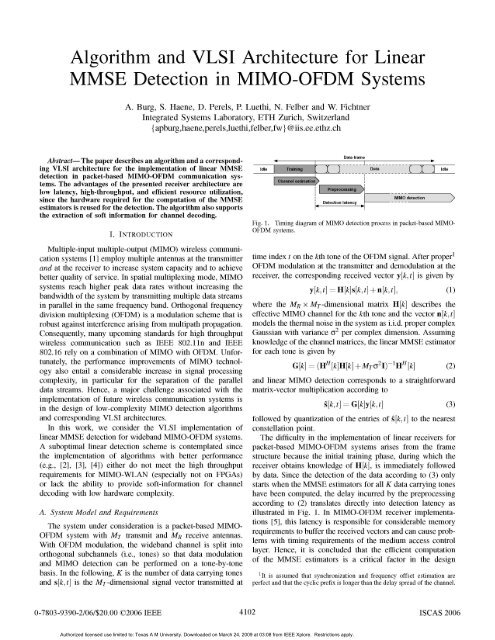

Fig. 1. Tim<strong>in</strong>g diagram of <strong>MIMO</strong> detection process <strong>in</strong> packet-based <strong>MIMO</strong>-<br />

I. INTRODUCTION OFDM systems.<br />

Multiple-<strong>in</strong>put multiple-output (<strong>MIMO</strong>) wireless communication<br />

systems [1] employ multiple antennas at the transmitter time <strong>in</strong>dex t on the kth tone of the OFDM signal. After proper<br />

<strong>and</strong> at the receiver to <strong>in</strong>crease system capacity <strong>and</strong> to achieve OFDM modulation at the transmitter <strong>and</strong> demodulation at the<br />

better quality of service. In spatial multiplex<strong>in</strong>g mode, <strong>MIMO</strong> receiver, the correspond<strong>in</strong>g received vector y[k, t] is given by<br />

systems reach higher peak data rates without <strong>in</strong>creas<strong>in</strong>g the y[k, t]= H[k]s[k, t] + n[k, t], (1)<br />

b<strong>and</strong>width of the system by transmitt<strong>in</strong>g multiple data streams<br />

<strong>in</strong> parallel <strong>in</strong> the same frequency b<strong>and</strong>. Orthogonal frequency where the MR X MT-dimensional matrix H[k] describes the<br />

division multiplex<strong>in</strong>g (OFDM) is a modulation scheme that is effective <strong>MIMO</strong> channel <strong>for</strong> the kth tone <strong>and</strong> the vector n[k, t]<br />

robust aga<strong>in</strong>st <strong>in</strong>terference aris<strong>in</strong>g from multipath propagation. models the thermal noise <strong>in</strong> the system as i.i.d. proper complex<br />

Consequently, many upcom<strong>in</strong>g st<strong>and</strong>ards <strong>for</strong> high throughput Gaussian with variance (Y per complex dimension. Assum<strong>in</strong>g<br />

wireless communication such as IEEE 802.1 <strong>in</strong> <strong>and</strong> IEEE knowledge of the channel matrices, the l<strong>in</strong>ear <strong>MMSE</strong> estimator<br />

802.16 rely on a comb<strong>in</strong>ation of <strong>MIMO</strong> with OFDM. Un<strong>for</strong>- <strong>for</strong> each tone is given by<br />

tunately, the per<strong>for</strong>mance improvements of <strong>MIMO</strong> technol- G[k] = (HH [k]H[k] +MT 2I) l HH[k] (2)<br />

ogy also entail a considerable <strong>in</strong>crease <strong>in</strong> signal process<strong>in</strong>g<br />

complexity, <strong>in</strong> particular <strong>for</strong> the separation of the parallel <strong>and</strong> l<strong>in</strong>ear <strong>MIMO</strong> detection corresponds to a straight<strong>for</strong>ward<br />

data streams. Hence, a major challenge associated with the matrix-vector multiplication accord<strong>in</strong>g to<br />

implementation of future wireless communication systems is<br />

<strong>in</strong> the design of low-complexity <strong>MIMO</strong> detection algorithms s[k,t] G[k]y[k,t] (3)<br />

<strong>and</strong> correspond<strong>in</strong>g <strong>VLSI</strong> architectures. followed by quantization of the entries of s[k, t] to the nearest<br />

In this work, we consider the <strong>VLSI</strong> implementation of constellation po<strong>in</strong>t.<br />

l<strong>in</strong>ear <strong>MMSE</strong> detection <strong>for</strong> wideb<strong>and</strong> <strong>MIMO</strong>-OFDM systems. The difficulty <strong>in</strong> the implementation of l<strong>in</strong>ear receivers <strong>for</strong><br />

A suboptimal l<strong>in</strong>ear detection scheme is contemplated s<strong>in</strong>ce packet-based <strong>MIMO</strong>-OFDM systems arises from the frame<br />

the implementation of algorithms with better per<strong>for</strong>mance structure because the <strong>in</strong>itial tra<strong>in</strong><strong>in</strong>g phase, dur<strong>in</strong>g which the<br />

(e.g., [2], [3], [4]) either do not meet the high throughput receiver obta<strong>in</strong>s knowledge of H[k], is immediately followed<br />

requirements <strong>for</strong> <strong>MIMO</strong>-WLAN (especially not on FPGAs) by data. S<strong>in</strong>ce the detection of the data accord<strong>in</strong>g to (3) only<br />

or lack the ability to provide soft-<strong>in</strong><strong>for</strong>mation <strong>for</strong> channel starts when the <strong>MMSE</strong> estimators <strong>for</strong> all K data carry<strong>in</strong>g tones<br />

decod<strong>in</strong>g with low hardware complexity.<br />

have been computed, the delay <strong>in</strong>curred by the preprocess<strong>in</strong>g<br />

accord<strong>in</strong>g to (2) translates directly <strong>in</strong>to detection latency as<br />

A. System Model <strong>and</strong> Requirements illustrated <strong>in</strong> Fig. 1. In <strong>MIMO</strong>-OFDM receiver implementa-<br />

The system under consideration is a packet-based <strong>MIMO</strong>- tions [5], this latency is responsible <strong>for</strong> considerable memory<br />

requirements to buffer the received vectors <strong>and</strong> can cause prob-<br />

OFDM systemwtth MT transmit <strong>and</strong> MR recetve antennas. par than th-eA<br />

0-7803-9390-2/06/$20.00~~~lem ©2006 IEEEn 4102emnt 2006du<br />

acsscnto ISCA<br />

Authorized licensed use limited to: Texas A M University. Downloaded on March 24, 2009 at 03:08 from IEEE Xplore. Restrictions apply.

of packet-based <strong>MIMO</strong>-OFDM receivers. However, it is also number of multiplications2 <strong>and</strong> divisions is given by<br />

noted that the correspond<strong>in</strong>g operation is only per<strong>for</strong>med once 5 2T5 2<br />

at the start of the frame so that, without special provisions, the CMult =2MRMT + 5MRM -MT +MT<br />

potentially costly hardware <strong>for</strong> the preprocess<strong>in</strong>g will be idle CDiv2MR (6)<br />

most of the time.<br />

Contribution: In this paper an algorithm <strong>for</strong> efficient tone- In order to map recursion (5) to hardware, its compact<br />

by-tone l<strong>in</strong>ear preprocess<strong>in</strong>g of channel state <strong>in</strong><strong>for</strong>mation <strong>in</strong> mathematical description is exp<strong>and</strong>ed as shown <strong>in</strong> Alg. 1. The<br />

<strong>MIMO</strong>-OFDM systems is presented, together with a hardware- operation sequence is designed to reduce the dynamic range<br />

efficient <strong>VLSI</strong> architecture <strong>for</strong> its realization. The described of <strong>in</strong>termediate results <strong>and</strong> to m<strong>in</strong>imize the number of costly<br />

receiver constitutes the basis <strong>for</strong> the soft-output demapper divisions, while keep<strong>in</strong>g the number of multiplications low.<br />

described <strong>in</strong> [6] which yields a 5-6 dB ga<strong>in</strong> <strong>in</strong> terms of signal<br />

to noise ratio (SNR) over a hard-decision <strong>MMSE</strong> decoder. <strong>Algorithm</strong> 1 <strong>Algorithm</strong> <strong>for</strong> comput<strong>in</strong>g the <strong>MMSE</strong> estimator<br />

The reported ASIC <strong>and</strong> FPGA area <strong>and</strong> per<strong>for</strong>mance figures P(M) 1l I<br />

provide reference <strong>for</strong> the true silicon complexity of l<strong>in</strong>ear <strong>for</strong> MT6M<br />

2lfrj=I...MR do<br />

<strong>MMSE</strong> receivers <strong>for</strong> <strong>MIMO</strong>-OFDM systems. 3 g =P(j-i)HH<br />

Outl<strong>in</strong>e: The next section <strong>in</strong>troduces the algorithm <strong>for</strong> 4: S= 1 + Hj (note that S is strictly positive)<br />

the computation of the l<strong>in</strong>ear <strong>MMSE</strong> detectors. Section III 5: Se elog25S - 2Sel/<br />

describes a scalable <strong>VLSI</strong> architecture <strong>for</strong> the proposed al- 6: g = 5mg<br />

gorithm. Area <strong>and</strong> per<strong>for</strong>mance figures <strong>for</strong> ASIC <strong>and</strong> FPGA 7: p(j) = p(j-1) - ggH2-Se<br />

implementations are provided <strong>in</strong> Section IV. Section V con- 8: end <strong>for</strong><br />

cludes the paper. 9: G =P(MR)HH<br />

II. PREPROCESSING ALGORITHM III. <strong>VLSI</strong> ARCHITECTURE<br />

<strong>Algorithm</strong> choices <strong>for</strong> the implementation of (2) are either The choice of a suitable hardware architecture <strong>for</strong> the<br />

based on QR-decomposition [7] us<strong>in</strong>g unitary trans<strong>for</strong>mations implementation of Alg. 1 depends on the system specifications<br />

or on direct matrix <strong>in</strong>version algorithms with conventional <strong>and</strong> on the available area: The most area efficient solution<br />

arithmetic. The ma<strong>in</strong> advantages of the QR approach lie <strong>in</strong> its is a fully decomposed, processor-like architecture. However,<br />

favorable numerical properties <strong>in</strong> fixed-po<strong>in</strong>t implementations such a m<strong>in</strong>imum-area solution cannot meet the low-latency<br />

<strong>and</strong> <strong>in</strong> the availability of a wide range of regular array archi- requirements of <strong>MIMO</strong>-OFDM systems. A highly parallel<br />

tectures [8], [9] <strong>for</strong> their implementation. The ma<strong>in</strong> arguments<br />

architecture achieves higher throughput but suffers signifi<strong>for</strong><br />

direct matrix <strong>in</strong>version are the lower number of operations cantly from the fact that data dependencies <strong>and</strong> the desire<br />

compared to QR decomposition <strong>and</strong> the fact that the matrix <strong>for</strong> a regular data flow m<strong>and</strong>ate a sequential execution of the<br />

(HH [k]H[k] +MTG2I) I is produced as an <strong>in</strong>termediate result. <strong>in</strong>dividual steps <strong>in</strong> Alg. 1. S<strong>in</strong>ce these steps differ significantly<br />

In fact, the diagonal entries of this matrix are required <strong>for</strong> the <strong>in</strong> the number of required operations, a massively parallel<br />

computation of soft-outputs [10], [6]. architecture would result <strong>in</strong> a poor utilization of process<strong>in</strong>g<br />

resources. In a moderately parallel <strong>VLSI</strong> architecture the<br />

The implementation that is described <strong>in</strong> this paper relies<br />

number of process<strong>in</strong>g resources is chosen so that their<br />

on direct matrix <strong>in</strong>version. The correspond<strong>in</strong>g algorithm iS<br />

average<br />

utlzto. shg.Moto.h tp nAl.1rqieete<br />

borrowed from the updat<strong>in</strong>g procedure of the Kalman ga<strong>in</strong> <strong>in</strong><br />

Kalman filter<strong>in</strong>g applications. The basic idea is to start from MT or a multiple Of MT multiplications. Hence, choos<strong>in</strong>g<br />

the trivial <strong>in</strong>verse Of MT.2I <strong>and</strong> to obta<strong>in</strong> (HHH + MTG2I) 1 an MT-fold degree of parallelism leads to a high hardware<br />

utilization.<br />

through a series of MR rank-one updates by us<strong>in</strong>g the matrix<br />

<strong>in</strong>version lemma. The iteration is <strong>in</strong>itialized by sett<strong>in</strong>g A. Moderately Parallel <strong>Architecture</strong><br />

p(O)<br />

M<br />

<strong>and</strong> proceeds by comput<strong>in</strong>g<br />

The high-level block diagram of the proposed moderately<br />

1 I (4) parallel architecture is shown <strong>in</strong> Fig. 2. The circuit employs<br />

MTG2<br />

step 4) <strong>and</strong> the pseudo float<strong>in</strong>g-po<strong>in</strong>t division <strong>in</strong> step 5). The<br />

HH p(j-l) connections <strong>in</strong> the array are local, mean<strong>in</strong>g that only neigh-<br />

(5) bor<strong>in</strong>g PEs are connected with each other. Each PE ma<strong>in</strong>ly<br />

p(i) =p(i-1) HI iH.Pi<br />

'<br />

MT identical process<strong>in</strong>g elements (PEs) arranged <strong>in</strong> a circular<br />

array <strong>and</strong> a common 1/ Y-block that computes the additions <strong>in</strong><br />

V 1 + HHP(j-1)HH'i conta<strong>in</strong>s a complex-valued multiplier, an adder <strong>and</strong> some local<br />

storage registers as shown <strong>in</strong> Fig. 3. All <strong>in</strong>termediate variables<br />

where H1 denotes the jth row of H. After MR iterations, are stored locally, equally distributed over the PBs. For the<br />

p(MR)~~~~~~~~~~<br />

. HH+MGI (R n H hr h 21n terms of complex-valued multiplications. The few real-valued mul<strong>in</strong>dex<br />

of the OFDM tone has been omitted <strong>for</strong> brevity. The tiplications are counted as complex-valued, assum<strong>in</strong>g a dedicated <strong>VLSI</strong><br />

complexity of the above described algorithm <strong>in</strong> terms of the architecture with multipliers optimized <strong>for</strong> complex-valued coefficients.<br />

4103<br />

Authorized licensed use limited to: Texas A M University. Downloaded on March 24, 2009 at 03:08 from IEEE Xplore. Restrictions apply.

Fr r s r r ' X S r fl X r wr wr tm ~~~~~~~~~~~~~~~~~~~Cycles<br />

PE(1) PH'l 4P4,2"j 2 P3,3 P2,4 [PHj]I<br />

27 t | zt z t| z t PE(3) _31 jl+22j2+l3j3

10T Ntpie°e FPGA Implementation. For the implementation of the de-<br />

4Nopipel<strong>in</strong>ed 6 sign (<strong>for</strong> MT = MR = 4) on a XILINX XC2V6000-6 FPGA,<br />

WW Area Time/Inv. WW = 18 was chosen as the device conta<strong>in</strong>s hardwired multi-<br />

18 69k 0.68 ,us O pliers of that size. The pipel<strong>in</strong>ed version operates with a clock<br />

1 75k 0.72 ,ls B<br />

t<br />

rate of 40 MHz <strong>and</strong> requires 2.2 ps to compute the <strong>MMSE</strong><br />

~1c<br />

21 85k<br />

0_ 74 _s_|_A_ estimator of one tone. Hence, <strong>for</strong> example, the detection<br />

______ ______ ______ ______ ______ latency <strong>in</strong> a system with K= 64 tones adds up to 141 ps. The<br />

_ _ _<br />

throughput <strong>in</strong> detection mode is 10 Mvps. In terms of area,<br />

the design consumes 16 out of 144 multipliers <strong>and</strong> 3'416 logic<br />

slices out of a total of 33'792.<br />

1 0 Pp_P;el<strong>in</strong>ed iW=18 V. CONCLUSIONS<br />

18<br />

CDiv = 8Tmecpd --v. WW=_1_9 In packet-based <strong>MIMO</strong>-OFDM systems even allegedly low-<br />

Area<br />

TmE/v.58 , WW-20 complexity l<strong>in</strong>ear detectors pose a considerable implementa-<br />

1_9 78k GE 0.6 ,us\ WW=21 tion challenge. The presented algorithm <strong>and</strong> the scalable <strong>VLSI</strong><br />

20 82k GE 0.6 ,us 'Float<strong>in</strong>g- architecture <strong>for</strong> the computation of the <strong>MMSE</strong> estimators<br />

-3 21 -89k GE 0.61[,us po<strong>in</strong>t_ ___<br />

10 o 1 0 25 30s35o 40 partially solve this problem <strong>for</strong> <strong>MIMO</strong>-OFDM systems with a<br />

1 0 1 5 20 25 30 35 40SNR small number of tones (K < 64). A first important advantage of<br />

the presented approach is that it reduces silicon area by reus<strong>in</strong>g<br />

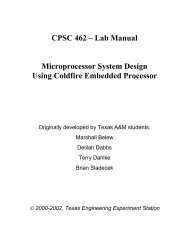

Fig. 5. Fixed-po<strong>in</strong>t BER simulation <strong>and</strong> <strong>VLSI</strong> implementation results the same hardware <strong>for</strong> the preprocess<strong>in</strong>g <strong>and</strong> the <strong>for</strong> the<br />

<strong>for</strong> <strong>MMSE</strong> detection <strong>in</strong> a system with MT = MR = 4 <strong>and</strong> with 16-QAM detection. The second advantage is the ability to easily extract<br />

modulation. soft bit-metrics <strong>for</strong> a subsequent channel decoder [6]. The<br />

ma<strong>in</strong> drawback are the considerable numerical requirements.<br />

Moreover, it is noted that <strong>for</strong> systems with a large number<br />

after the operations associated with steps 3), 4), 6), 7) <strong>and</strong> 9) of tones, preprocess<strong>in</strong>g latency is still too high. A possible<br />

of Alg. 1. As a result, the number of cycles <strong>in</strong>creases to solution to this problem has recently been proposed <strong>in</strong> [11].<br />

tCPd = MR (3MT + 6) -MT + 2+ MRCDiV (8) ACKNOWLEDGEMENT<br />

This work is supported by the STREP project No. IST<strong>and</strong><br />

the number of cycles <strong>for</strong> the division must also be 026905 (MASCOT) with<strong>in</strong> the sixth framework programme<br />

<strong>in</strong>creased to match the higher clock rate.<br />

of the European Commission.<br />

REFERENCES<br />

IV. IMPLEMENTATION RESULTS [1] G. Fosch<strong>in</strong>i <strong>and</strong> M. Gans, "On limits of wireless communications <strong>in</strong> a<br />

fad<strong>in</strong>g environment when us<strong>in</strong>g multiple antennas," Wireless Personal<br />

ASIC critical design is Communications, vol. 6, no. 3, pp. 311-334, 1998.<br />

ASIC Implementation. A crlhcal deslgn parameter 1S the [2] Z. Guo <strong>and</strong> P. Nilsson, "A 53.3 Mb/s 4 x 4 16-QAM <strong>MIMO</strong> decoder <strong>in</strong><br />

wordlength of the complex-valued datapath. The correspond- 0.35pm CMOS," <strong>in</strong> Proc. IEEE ISCAS, May 2005, pp. 4947-4950.<br />

<strong>in</strong>g trade-offs between silicon area, bit error rate (BER) per<strong>for</strong>- [3] A. Burg, M. Borgmann, M. Wenk, M. Zellweger, W. Fichtner, <strong>and</strong><br />

mance, <strong>and</strong> the computation time <strong>for</strong>mance, a s<strong>in</strong>gle <strong>and</strong> the <strong>MMSE</strong> computationtie<strong>for</strong>as<strong>in</strong>gleMMSH. B6lcskei, "<strong>VLSI</strong> implementation of <strong>MIMO</strong> detection us<strong>in</strong>g the sphere<br />

estimator decoder algorithm," IEEE Journal of Solid-State Circuits, 2005.<br />

is illustrated <strong>in</strong> Fig. 5 <strong>for</strong> a system with MT = MR = 4. [4] M. Wenk, M. Zellweger, A. Burg, N. Felber, <strong>and</strong> W. Fichtner, "K-Best<br />

The <strong>VLSI</strong> implementation results are based on a 0.25 pm <strong>MIMO</strong> detection <strong>VLSI</strong> architectures achiev<strong>in</strong>g up to 424 Mbps," <strong>in</strong> Proc.<br />

simulationstheentIEEE<br />

Int. Symp. on Circuits <strong>and</strong> Systems, May 2006.<br />

technology <strong>and</strong> <strong>for</strong> the BERtechnology simulations <strong>and</strong> <strong>for</strong>the BER entries of H[k] [5] D. Perels, S. Haene, P. Luethi, A. Burg, N. Felber, W. Fichtner, <strong>and</strong><br />

are assumed i.i.d. Rayleigh fad<strong>in</strong>g with variance one, so that H. B6lcskei, "ASIC implementation of a <strong>MIMO</strong>-OFDM transceiver <strong>for</strong><br />

the received SNR is given by 17/2. For the computation of 192 mbps WLANs," <strong>in</strong> Proc. IEEE ESSCIRC, Sept. 2005, pp. 215-218.<br />

the <strong>MMSE</strong> estimator, H [k] is represented <strong>in</strong> a block float<strong>in</strong>g- [6] s. Haene, A. Burg, D. Perels, P. Luethi, N. Felber, <strong>and</strong> W. Fichtner,<br />

"Silicon implementation of an <strong>MMSE</strong>-based soft demapper <strong>for</strong> <strong>MIMO</strong>po<strong>in</strong>t<br />

<strong>for</strong>mat <strong>and</strong> WW denotes the wordwidth of the real-valued BICM," <strong>in</strong> Proc. IEEE Int. Symp. on Circuits <strong>and</strong> Systems, May 2006.<br />

multipliers which constitute the complex-valued multipliers [7] Z. Khan, T. Arslan, J. S. Thompson, <strong>and</strong> A. T. Erdogan, "Area & power<br />

efficient <strong>VLSI</strong> architecture <strong>for</strong><br />

<strong>in</strong> the PEs. The clock rates of the unpipel<strong>in</strong>ed designs are<br />

comput<strong>in</strong>g pseudo <strong>in</strong>verse of channel<br />

ln t PsT ccrsfhu pnamatrix <strong>in</strong> a <strong>MIMO</strong> wireless system," <strong>in</strong> Proc. IEEE Int. Conf on <strong>VLSI</strong><br />

between 93 MHz <strong>and</strong> 101 MHz, depend<strong>in</strong>g on the wordlength. Design (<strong>VLSI</strong>D), Jan. 2006, pp. 734-737.<br />

The pipel<strong>in</strong>ed implementations achieve between 167 MHz <strong>and</strong> [8] G. Lightbody, R. Woods, <strong>and</strong> R. Walke, "Design of a parameterized<br />

silicon <strong>in</strong>tellectual<br />

176 MHz. For the computation of the <strong>MMSE</strong> estimators, the<br />

property core <strong>for</strong> QR-based RLS filter<strong>in</strong>g," IEEE<br />

Trans. on <strong>VLSI</strong> Systems, vol. 11, pp. 659-678, 2003.<br />

ga<strong>in</strong> from the higher clock frequency rema<strong>in</strong>s small due to [9] F. Edman <strong>and</strong> V. Owall, "A scalable pipel<strong>in</strong>ed complex valued matrix<br />

the <strong>in</strong>crease <strong>in</strong> the number of cycles. However, a significant <strong>in</strong>version architecture," <strong>in</strong> Proc. IEEE ISCAS, 2005, pp. 4489-4492.<br />

per<strong>for</strong>mance improvement is achieved from pipel<strong>in</strong><strong>in</strong>g when<br />

[10] I. B. Coll<strong>in</strong>gs, M. R. G. Butler, <strong>and</strong> M. McKay, "Low complexity<br />

ceiver design <strong>for</strong> <strong>MIMO</strong> bit-<strong>in</strong>terleaved coded modulation," <strong>in</strong> Proc. 8th<br />

re-<br />

the circuit operates <strong>in</strong> detection mode, because dur<strong>in</strong>g this IEEEInt. Symposium on Spread Spectrum Techniques <strong>and</strong> Applications,<br />

operation no pipel<strong>in</strong>e bubbles need to be <strong>in</strong>serted. Without 2004, pp. 12-16.<br />

... . ~~~~~~~~~~~~~[11]<br />

D. Cescato, M. Borgmann, H. Boilcskei, J. C. Hansen, <strong>and</strong> A. Burg,<br />

pipel<strong>in</strong><strong>in</strong>g, 23-25 millilon (received) vectors per second (Mvps) "Interpolation-based QR decomposition <strong>in</strong> <strong>MIMO</strong>-OFDM systems,"<br />

can be processed, while with pipel<strong>in</strong><strong>in</strong>g throughput <strong>in</strong>creases <strong>in</strong> Proc. IEEE Workshop on Signal Process<strong>in</strong>g Advances <strong>in</strong> Wireless<br />

to 42-44 Mvps. Communications (SPAWC), June 2005, pp. 945-949.<br />

4105<br />

Authorized licensed use limited to: Texas A M University. Downloaded on March 24, 2009 at 03:08 from IEEE Xplore. Restrictions apply.