CV - NED University

CV - NED University

CV - NED University

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

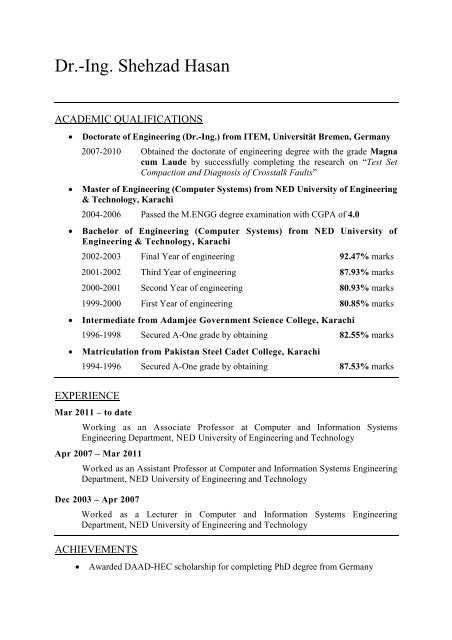

Dr.-Ing. Shehzad Hasan<br />

ACADEMIC QUALIFICATIONS<br />

<br />

<br />

Doctorate of Engineering (Dr.-Ing.) from ITEM, Universität Bremen, Germany<br />

2007-2010 Obtained the doctorate of engineering degree with the grade Magna<br />

cum Laude by successfully completing the research on “Test Set<br />

Compaction and Diagnosis of Crosstalk Faults”<br />

Master of Engineering (Computer Systems) from <strong>NED</strong> <strong>University</strong> of Engineering<br />

& Technology, Karachi<br />

2004-2006 Passed the M.ENGG degree examination with CGPA of 4.0<br />

Bachelor of Engineering (Computer Systems) from <strong>NED</strong> <strong>University</strong> of<br />

Engineering & Technology, Karachi<br />

<br />

<br />

2002-2003 Final Year of engineering 92.47% marks<br />

2001-2002 Third Year of engineering 87.93% marks<br />

2000-2001 Second Year of engineering 80.93% marks<br />

1999-2000 First Year of engineering 80.85% marks<br />

Intermediate from Adamjee Government Science College, Karachi<br />

1996-1998 Secured A-One grade by obtaining 82.55% marks<br />

Matriculation from Pakistan Steel Cadet College, Karachi<br />

1994-1996 Secured A-One grade by obtaining 87.53% marks<br />

EXPERIENCE<br />

Mar 2011 – to date<br />

Working as an Associate Professor at Computer and Information Systems<br />

Engineering Department, <strong>NED</strong> <strong>University</strong> of Engineering and Technology<br />

Apr 2007 – Mar 2011<br />

Worked as an Assistant Professor at Computer and Information Systems Engineering<br />

Department, <strong>NED</strong> <strong>University</strong> of Engineering and Technology<br />

Dec 2003 – Apr 2007<br />

Worked as a Lecturer in Computer and Information Systems Engineering<br />

Department, <strong>NED</strong> <strong>University</strong> of Engineering and Technology<br />

ACHIEVEMENTS<br />

<br />

Awarded DAAD-HEC scholarship for completing PhD degree from Germany

PUBLICATIONS<br />

1. Shehzad Hasan, Ajoy K. Palit and Walter Anheier, "Fault Diagnosis of Crosstalk<br />

Induced Glitches and Delay Faults", in Proceedings of the 13 th IEEE International<br />

Symposium on Design and Diagnostics of Electronic Circuits and Systems, DDECS<br />

2010, 14 th - 16 th April 2010, Vienna, Austria<br />

2. Shehzad Hasan, Ajoy K. Palit, and Walter Anheier, "Test Pattern Generation and<br />

Compaction for Crosstalk Induced Glitches and Delay Faults", in Proceedings of<br />

the 23 rd IEEE International Conference on VLSI Design, VLSI 2010, 3 rd - 7 th January<br />

2010, Bangalore, India<br />

3. Ajoy K. Palit, Shehzad Hasan, and Walter Anheier, "Decoupled Victim Model for the<br />

Analysis of Crosstalk Noise between On-chip Coupled Interconnects", in<br />

Proceedings of the 11 th IEEE Electronics Packaging Technology Conference, EPTC<br />

2009, 9 th - 11 th December 2009, Singapore<br />

4. Shehzad Hasan, Ajoy K. Palit, and Walter Anheier, "Equivalent Victim Model of the<br />

Coupled Interconnects for Simulating Crosstalk Induced Glitches and Delays", in<br />

Proceedings of the 13 th IEEE Workshop on Signal Propagation on Interconnects, SPI<br />

2009, 12 th - 15 th May 2009, Strasbourg, France<br />

5. Shehzad Hasan, Ajoy K. Palit, Kishore K. Duganapalli, and Walter Anheier,<br />

"Compaction of Test Set for Crosstalk Induced Glitch Faults using Pattern<br />

Sequencing", in Proceedings of the 21 st Workshop für Testmethoden und<br />

Zuverlässigkeit von Schaltungen und Systemen, February 2009, Bremen, Germany<br />

6. Ajoy K. Palit, Shehzad Hasan, Kishore K. Duganapalli, and Walter Anheier,<br />

"Distributed RLGC Transient Model of Coupled Interconnects in DSM Chips for<br />

Crosstalk Noise Simulation", in Proceedings of the 2 nd IEEE Electronics System-<br />

Integration Technology Conference, 1 st - 4 th Sept 2008, Greenwich, London<br />

POSTERS<br />

1. Shehzad Hasan, "Test Pattern Generation and Compaction for Crosstalk Induced<br />

Glitch Faults", in Informal Proceedings of the 14 th IEEE European Test Symposium,<br />

ETS 2009, PhD Forum, 25 th - 29 th May 2009, Seville, Spain<br />

2. Shehzad Hasan, Ajoy K. Palit and Walter Anheier, "Crosstalk Glitch Fault ATPG<br />

with Test Compaction", at <strong>University</strong> Booth Section of Design Automation and Test<br />

in Europe Conference, DATE 2009, 20 th - 24 th April 2009, Nice, France<br />

3. Shehzad Hasan, Ajoy K. Palit, Kishore K. Duganapalli and Walter Anheier, "Test<br />

Compaction of Crosstalk Faults through Fault List Reordering ", at <strong>University</strong><br />

Booth Section of Design Automation and Test in Europe Conference, DATE 2008,<br />

10 th -14 th March 2008, Munich, Germany<br />

MEMBERSHIP<br />

Member of IEEE since 2007 (no. 90425240)<br />

<br />

Life Member of the Pakistan Engineering Council (no. COMP/2084)