National Level Workshop on VLSI, MEMS ... - VIT University

National Level Workshop on VLSI, MEMS ... - VIT University

National Level Workshop on VLSI, MEMS ... - VIT University

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Address for Corresp<strong>on</strong>dence<br />

Dr. A. Ravi Sankar, Prof. / SENSE,<br />

Prof. Augusta Sophy, Asst. Prof. / SENSE,<br />

<strong>VIT</strong> <strong>University</strong> (Chennai Campus),<br />

Vandalur – Kelambakkam Road,<br />

Chennai – 600 048.<br />

Telefax : (044) 3993 2555<br />

Teleph<strong>on</strong>e: (044) 3993 1274/43<br />

Email: ravisankar.a@vit.ac.in, augustasophyt.t@vit.ac.in<br />

Facilitators<br />

1. Prof. M Kalyan Chakravarti, AP/SENSE (8148736577)<br />

2. Prof. Reena, AP/SENSE (9840837624)<br />

3. Prof. Rani Alex, ACP/SENSE (9094908549)<br />

Target Participants<br />

Faculty members, Research Scholars and graduate students<br />

from Engineering Instituti<strong>on</strong>s and participants from Industry.<br />

Registrati<strong>on</strong> Fee<br />

Faculty/Industry participants: Rs. 1000/ -<br />

Research Scholars/ students: Rs. 700/-<br />

Registrati<strong>on</strong> fee includes registrati<strong>on</strong> kit, lunch and<br />

refreshment for both the days. Local accommodati<strong>on</strong> will be<br />

provided based <strong>on</strong> request by mail/ph<strong>on</strong>e atleast a week<br />

before the event at nominal cost.<br />

Payment Mode<br />

The Registrati<strong>on</strong> form in the prescribed format, al<strong>on</strong>g with<br />

n<strong>on</strong>-refundable DD drawn in favour of “<strong>VIT</strong> <strong>University</strong>,<br />

Chennai Campus”, payable at Chennai, to be sent to the<br />

above menti<strong>on</strong>ed c<strong>on</strong>tact address <strong>on</strong> or before 30 Nov. 2011.<br />

Important Dates<br />

Last date for registrati<strong>on</strong> : 06-12-2011<br />

Durati<strong>on</strong> of program : 09 th & 10 th Dec. 2011<br />

Objective of the Program<br />

The objective of the workshop is to bring people engaged in<br />

teaching, research, industries and educati<strong>on</strong> together to<br />

enhance their knowledge level in the fields of <strong>VLSI</strong>, <strong>MEMS</strong><br />

and their Integrati<strong>on</strong>. Eminent resource pers<strong>on</strong>s from<br />

academia and industries will share and disseminate scientific<br />

knowledge and design methodologies, which will help the<br />

participants to set new millst<strong>on</strong>es in the above menti<strong>on</strong>ed<br />

fields of research for their pursuit.<br />

The FDP program will mainly focus <strong>on</strong> the following<br />

parameters:<br />

a) Fr<strong>on</strong>tend and backend design of <strong>VLSI</strong> circuits<br />

b) Digital IC design flow using Mentor EDA tool flow<br />

c) Functi<strong>on</strong>al Verificati<strong>on</strong> Synthesis, simulati<strong>on</strong><br />

mismatches - a study using Modelsim, Le<strong>on</strong>ardo<br />

Spectrum and precisi<strong>on</strong> RTL<br />

d) Comparis<strong>on</strong> between ASIC and FPGA synthesis flow<br />

e) Focus <strong>on</strong> backend design flow with relevant details<br />

<strong>on</strong> physical design & verificati<strong>on</strong><br />

f) Overview of parasitic extracti<strong>on</strong> and back annotati<strong>on</strong><br />

g) Process modeling and electromechanical design<br />

<strong>MEMS</strong> and Micro-sensors<br />

h) Multi-physics analysis and system level modeling of<br />

<strong>MEMS</strong> and Micro-sensors<br />

Program Highlights<br />

Lectures by academics and researchers from reputed<br />

instituti<strong>on</strong>s, such as IISc, and IIT Madras, <strong>VIT</strong> Chennai<br />

Campus, followed by presentati<strong>on</strong>s, dem<strong>on</strong>strati<strong>on</strong>s and<br />

hands-<strong>on</strong> training by the EDA Tool vendors.<br />

Day 1<br />

Sessi<strong>on</strong> I Lecture by Dr Navakantha Bhat, Prof.,<br />

Department of ECE, IISc, Bangalore<br />

Sessi<strong>on</strong> II C<strong>on</strong>cepts of Full custom & semicustom IC<br />

Design flow<br />

Sessi<strong>on</strong> III<br />

Overview of Netlist to GDS flow<br />

Sessi<strong>on</strong> IV - Hands-<strong>on</strong> sessi<strong>on</strong> <strong>on</strong> schematic and layout<br />

simulati<strong>on</strong>s - C<strong>on</strong>cepts of physical verificati<strong>on</strong> –LVS<br />

checks<br />

- Physical Verificati<strong>on</strong> using Calibre & Post Layout<br />

Simulati<strong>on</strong> using ELDO<br />

Day 2<br />

Sessi<strong>on</strong> I Mentor Graphics Tools - C<strong>on</strong>cepts of parasitic<br />

extracti<strong>on</strong> and back annotati<strong>on</strong><br />

Sessi<strong>on</strong> II <strong>MEMS</strong> Design Flow using Intellisuite<br />

Sessi<strong>on</strong> III Process simulati<strong>on</strong> - 3D Builder – Case Study<br />

– Pressure/Accelerati<strong>on</strong> Sensor – Simulati<strong>on</strong><br />

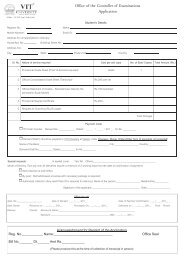

<str<strong>on</strong>g>Nati<strong>on</strong>al</str<strong>on</strong>g> <str<strong>on</strong>g>Level</str<strong>on</strong>g> <str<strong>on</strong>g>Workshop</str<strong>on</strong>g> <strong>on</strong><br />

<strong>VLSI</strong>, <strong>MEMS</strong> & INTEGRATION<br />

December 09-10, 2011<br />

REGISTRATION FORM<br />

Name :............................................................<br />

Designati<strong>on</strong> :............................................................<br />

Department :............................................................<br />

Address : ...........................................................<br />

: ...........................................................<br />

: ...........................................................<br />

Mobile No :............................................................<br />

Email ID :............................................................<br />

Payment Details<br />

DD No.: …………………. ..........................................<br />

Date: ………………<br />

Amount Rs.: ……………..<br />

Bank: ……………………..<br />

Signature & Date

<strong>VIT</strong> <strong>University</strong> - Chennai Campus<br />

<strong>VIT</strong> <strong>University</strong> has made a mark in the field of higher<br />

educati<strong>on</strong> in India during the past 25 years, imparting quality<br />

educati<strong>on</strong> in a cross-cultural ambience, intertwined with<br />

extensive applicati<strong>on</strong> oriented research. <strong>VIT</strong> has secured the<br />

8th positi<strong>on</strong> (India Today 2010) am<strong>on</strong>g the Engineering<br />

Instituti<strong>on</strong>s in India. It was established by the well-known<br />

educati<strong>on</strong>alist and former Parliamentarian, Dr.G.Viswanathan,<br />

Founder and Chancellor. Being a visi<strong>on</strong>ary, he transformed<br />

<strong>VIT</strong> into a Center of Excellence in higher technical educati<strong>on</strong>.<br />

His dream has materialized further as the new campus at the<br />

heart of the Chennai City, as <strong>VIT</strong> <strong>University</strong>, Chennai Campus<br />

(<strong>VIT</strong>-CC). Spearheaded by Mr. G. V. Selvam, Vice President,<br />

the instituti<strong>on</strong> is making leaps and bounds in professi<strong>on</strong>al<br />

programs. The Vice President has a missi<strong>on</strong> to make this<br />

instituti<strong>on</strong> a global center with the latest learning facilities. Dr.<br />

V. Raju, former Professor of State <strong>University</strong> of New York,<br />

USA, currently the Vice Chancellor, strives to internati<strong>on</strong>alize<br />

the educati<strong>on</strong>al standards. Dr. Anand A. Samuel, Pro-Vice<br />

Chancellor leads the team in Chennai with the following<br />

objectives:<br />

• To maximize Industrial C<strong>on</strong>nectivity and create Centers of<br />

Excellence in niche areas of research<br />

•To enrich Technological and Managerial Human Capital<br />

nurtured in a multicultural ambience<br />

• To provide a platform for the agglomerati<strong>on</strong> of ideas of<br />

pers<strong>on</strong>nel from various walks of life for learning enrichment<br />

• To create opportunities and exploit the available resources<br />

to benefit industry /society<br />

• To encourage participati<strong>on</strong> in the <str<strong>on</strong>g>Nati<strong>on</strong>al</str<strong>on</strong>g> Agenda of<br />

knowledge building<br />

• To foster Internati<strong>on</strong>al collaborati<strong>on</strong>s for mutual benefits in<br />

all fr<strong>on</strong>tier areas of research.<br />

The School<br />

The School of Electr<strong>on</strong>ics Engineering at <strong>VIT</strong> <strong>University</strong> was<br />

established for imparting a state-of the- art educati<strong>on</strong>, training<br />

and research in the field of Electr<strong>on</strong>ics and Communicati<strong>on</strong><br />

Engineering and allied areas. It offers B.Tech., and Ph. D.<br />

Programmes in the domain of Electr<strong>on</strong>ics and<br />

Communicati<strong>on</strong> Engineering. The expertise of the faculty<br />

members include <strong>VLSI</strong>, Optical Communicati<strong>on</strong>, Image and<br />

Signal Processing and all fr<strong>on</strong>tier areas.<br />

Mentor Graphics<br />

Mentor Graphics® provides<br />

software and hardware<br />

design soluti<strong>on</strong>s enabling<br />

companies to develop faster and efficient electr<strong>on</strong>ic products<br />

more cost-effectively. It helps engineers in overcoming the<br />

design challenges in the increasingly complex worlds of board<br />

and SoC designs.<br />

CoreEL Technologies<br />

CoreEL echnologies is a technology company with<br />

businesses spread across design services & product<br />

development, distributi<strong>on</strong> and training. Head Quartered in<br />

Bangalore, India, CoreEL is a leading provider of <strong>VLSI</strong> &<br />

Embedded System design services and Intellectual Property.<br />

Its Services offerings include Distributi<strong>on</strong> of Silic<strong>on</strong> soluti<strong>on</strong>s,<br />

EDA tools, COTS products, Engineering Services (Turn Key<br />

Systems Design, Turn Key FPGA Design and High Speed<br />

PCB Design), Educati<strong>on</strong> and Manufacturing.<br />

Sp<strong>on</strong>sored by<br />

TMI Systems<br />

And<br />

<str<strong>on</strong>g>Nati<strong>on</strong>al</str<strong>on</strong>g> <str<strong>on</strong>g>Level</str<strong>on</strong>g> <str<strong>on</strong>g>Workshop</str<strong>on</strong>g> <strong>on</strong><br />

<strong>VLSI</strong>, <strong>MEMS</strong> & INTEGRATION<br />

December 09-10, 2011<br />

CO-ORDINATORS<br />

Dr. V.S. Kanchana Bhaaskaran, Prof. / ECE<br />

Dr. A. Ravisankar Prof. / ECE<br />

Organized by<br />

<strong>VIT</strong> <strong>University</strong> (Chennai Campus)<br />

School of Electr<strong>on</strong>ics Engineering<br />

Vandalur – Kelambakkam Road,<br />

Chennai 600048<br />

Telefax : (044) 3993 2555<br />

Teleph<strong>on</strong>e: (044) 3993 1274/43<br />

www.vit.ac.in

![[26th â 30th Oct 2009] - Result - VIT University](https://img.yumpu.com/48486076/1/184x260/26th-a-30th-oct-2009-result-vit-university.jpg?quality=85)