Lecture 12 - Webstaff.kmutt.ac.th - kmutt

Lecture 12 - Webstaff.kmutt.ac.th - kmutt

Lecture 12 - Webstaff.kmutt.ac.th - kmutt

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

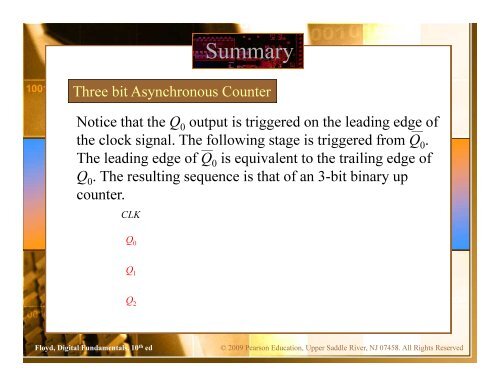

Summary<br />

Three bit Asynchronous Counter<br />

Notice <strong>th</strong>at <strong>th</strong>e Q 0 output is triggered on <strong>th</strong>e leading edge of<br />

<strong>th</strong>e clock signal. The following stage is triggered from Q 0 .<br />

The leading edge of Q 0 is equivalent to <strong>th</strong>e trailing edge of<br />

Q 0 . The resulting sequence is <strong>th</strong>at of an 3-bit binary up<br />

counter.<br />

CLK<br />

Q 2<br />

0 0 0 0 1 1 1 1 0<br />

1 2 3 4 5 6 7 8<br />

Q 0<br />

0 1 0 1 0 1 0 1 0<br />

Q 1<br />

0 0 1 1 0 0 1 1 0<br />

Floyd, Digital Fundamentals, 10 <strong>th</strong> ed<br />

© 2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved