4.à¹à¸à¸¥à¸¢à¸à¹à¸à¸ªà¸à¸à¸à¸¥à¸²à¸¢à¸ าภ1/2556

4.à¹à¸à¸¥à¸¢à¸à¹à¸à¸ªà¸à¸à¸à¸¥à¸²à¸¢à¸ าภ1/2556

4.à¹à¸à¸¥à¸¢à¸à¹à¸à¸ªà¸à¸à¸à¸¥à¸²à¸¢à¸ าภ1/2556

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

รหัส................................................... ชื่อ-นามสกุล...........................................................................................<br />

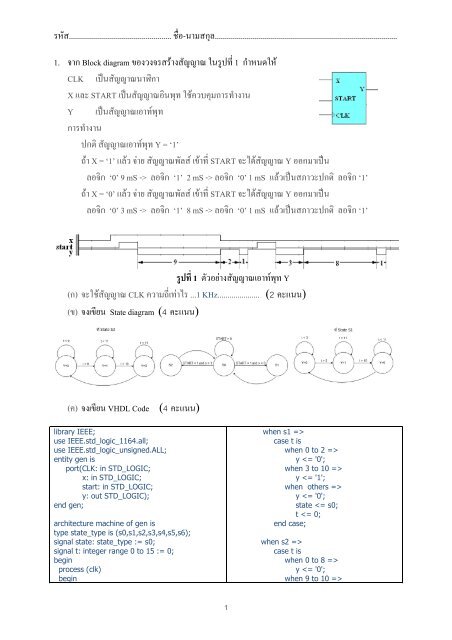

1. จาก Block diagram ของวงจรสร้างสัญญาณ ในรูปที่ 1 ก าหนดให้<br />

CLK เป็นสัญญาณนาฬิกา<br />

X และ START เป็นสัญญาณอินพุท ใช้ควบคุมการท างาน<br />

Y เป็นสัญญาณเอาท์พุท<br />

การท างาน<br />

ปกติ สัญญาณเอาท์พุท Y = ‘1’<br />

ถ้า X = ‘1’ แล้ว จ่าย สัญญาณพัลส์ เข้าที่ START จะได้สัญญาณ Y ออกมาเป็น<br />

ลอจิก ‘0’ 9 mS -> ลอจิก ‘1’ 2 mS -> ลอจิก ‘0’ 1 mS แล้วเป็นสภาวะปกติ ลอจิก ‘1’<br />

ถ้า X = ‘0’ แล้ว จ่าย สัญญาณพัลส์ เข้าที่ START จะได้สัญญาณ Y ออกมาเป็น<br />

ลอจิก ‘0’ 3 mS -> ลอจิก ‘1’ 8 mS -> ลอจิก ‘0’ 1 mS แล้วเป็นสภาวะปกติ ลอจิก ‘1’<br />

รูปที่ 1 ตัวอย่างสัญญาณเอาท์พุท Y<br />

(ก) จะใช้สัญญาณ CLK ความถี่เท่าไร ...1 KHz..................... (2 คะแนน)<br />

(ข) จงเขียน State diagram (4 คะแนน)<br />

(ค) จงเขียน VHDL Code<br />

(4 คะแนน)<br />

library IEEE;<br />

use IEEE.std_logic_1164.all;<br />

use IEEE.std_logic_unsigned.ALL;<br />

entity gen is<br />

port(CLK: in STD_LOGIC;<br />

x: in STD_LOGIC;<br />

start: in STD_LOGIC;<br />

y: out STD_LOGIC);<br />

end gen;<br />

architecture machine of gen is<br />

type state_type is (s0,s1,s2,s3,s4,s5,s6);<br />

signal state: state_type := s0;<br />

signal t: integer range 0 to 15 := 0;<br />

begin<br />

process (clk)<br />

begin<br />

when s1 =><br />

case t is<br />

when 0 to 2 =><br />

y <br />

y <br />

y

รหัส................................................... ชื่อ-นามสกุล...........................................................................................<br />

if clk = '1' and clk'event then<br />

t<br />

y

รหัส................................................... ชื่อ-นามสกุล...........................................................................................<br />

library IEEE;<br />

use IEEE.std_logic_1164.all;<br />

use IEEE.std_logic_unsigned.ALL;<br />

entity counter is<br />

port(CLK: in STD_LOGIC;<br />

C: in STD_LOGIC;<br />

E: in STD_LOGIC;<br />

y: out STD_LOGIC_VECTOR(2 downto<br />

0));<br />

end counter;<br />

architecture moore_beh of counter is<br />

type state_type is (s0,s1,s2,s3,s4,s5,s6,s7);<br />

signal state: state_type;<br />

begin<br />

process (clk)<br />

begin<br />

if (clk = '1' and clk'event) and (C ='1' )then<br />

case state is<br />

when s0 =><br />

if E = '0' then<br />

state

รหัส................................................... ชื่อ-นามสกุล...........................................................................................<br />

(ค) จงเขียน State diagram ของวงจรนี้ (3 คะแนน)<br />

X = 1<br />

X = 0<br />

X = 0<br />

S0/00 S1/00<br />

X = 0<br />

S2/00<br />

X = 1<br />

S3/01<br />

X = 0<br />

X = 1<br />

S3/00<br />

X = 1<br />

S5/10<br />

(ง) จงเขียน VHDL Code (7 คะแนน)<br />

library IEEE;<br />

use IEEE.std_logic_1164.all;<br />

use IEEE.std_logic_unsigned.ALL;<br />

entity seq is<br />

port(CLK: in STD_LOGIC;<br />

x: in STD_LOGIC;<br />

y: out STD_LOGIC_VECTOR(1 downto 0));<br />

end seq;<br />

architecture moore_beh of seq is<br />

type state_type is (s0,s1,s2,s3,s4,s5);<br />

signal state: state_type;<br />

begin<br />

process (clk)<br />

begin<br />

if clk = '0' and clk'event then<br />

case state is<br />

when s0 =><br />

if x = '0' then<br />

state

รหัส................................................... ชื่อ-นามสกุล...........................................................................................<br />

(ข) จงเขียน VHDL Code (7 คะแนน)<br />

library IEEE;<br />

use IEEE.std_logic_1164.all;<br />

use IEEE.std_logic_unsigned.ALL;<br />

use IEEE.std_logic_textio.all;<br />

use STD.textio.all;<br />

entity seq_teb is<br />

end seq_teb;<br />

architecture seq_beh of seq_teb is<br />

component seq<br />

port(CLK: in STD_LOGIC;<br />

x: in STD_LOGIC;<br />

y: out STD_LOGIC_VECTOR(1 downto<br />

0));<br />

end component;<br />

signal sclk, sx : std_logic;<br />

signal sy : std_logic_vector(1 downto 0);<br />

begin<br />

DUT: seq port map(CLK => sclk, x => sx, y =><br />

sy);<br />

begin<br />

wait for 50 ns;<br />

while not endfile(STIMULI_IN) loop<br />

sclk

![03-datatype [à¸à¹à¸²à¸à¸à¸¢à¹à¸²à¸à¹à¸à¸µà¸¢à¸§]](https://img.yumpu.com/38706121/1/184x260/03-datatype-a-aaaa-aaaaaaauaa.jpg?quality=85)