ä½åèAESä¿¡æ¯å®å ¨è¯ç设计ä¸å®ç° - ä¸å½ç§å¦é¢æ·±å³å è¿ææ¯ç 究é¢

ä½åèAESä¿¡æ¯å®å ¨è¯ç设计ä¸å®ç° - ä¸å½ç§å¦é¢æ·±å³å è¿ææ¯ç 究é¢

ä½åèAESä¿¡æ¯å®å ¨è¯ç设计ä¸å®ç° - ä¸å½ç§å¦é¢æ·±å³å è¿ææ¯ç 究é¢

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Vol. 3 No.4 / Apr. 2009<br />

低 功 耗 AES 信 息 安 全 芯 片 设 计 与 实 现<br />

章 成 旻 梁 允 萍 黄 墩 峰 李 烨<br />

摘 要 个 性 化 的 远 程 医 疗 是 医 疗 保 健 服 务 发 展 的 必 然 趋 势 , 远 程 信 息 处 理 对 保 护 用 户 数 据 传 输 的 安 全 性 和 设 备 的 功 耗<br />

方 面 都 提 出 了 更 高 的 要 求 。 高 级 加 密 标 准 AES 是 当 前 最 为 安 全 有 效 的 商 用 对 称 加 密 算 法 , 成 为 信 息 安 全 的 首 选 算 法 。 而 相<br />

比 于 软 件 实 现 ,AES 硬 件 芯 片 显 得 更 为 安 全 、 低 耗 、 高 效 。 我 们 综 合 运 用 资 源 共 享 、 算 法 集 成 等 手 段 , 旨 在 实 现 一 款 低 功<br />

耗 、 高 效 的 AES 硬 件 加 密 芯 片 。<br />

关 键 词 AES; 低 功 耗 ; 资 源 共 享 ; 流 水<br />

1 引 言<br />

高 级 加 密 标 准 ( A d v a n c e d E n c r y p t i o n<br />

Standard,AES), 又 称 Rijndael 加 密 法 , 是 美 国 联<br />

邦 政 府 采 用 的 一 种 区 块 加 密 标 准 。 这 个 标 准 用 来 替<br />

代 原 先 的 DES, 已 经 被 多 方 分 析 且 广 为 全 世 界 所 使<br />

用 。 经 过 五 年 的 甄 选 流 程 , 高 级 加 密 标 准 由 美 国 国<br />

家 标 准 与 技 术 研 究 院 (NIST) 于 2001 年 11 月 26 日 发 布<br />

于 FIPS PUB 197, 并 在 2002 年 5 月 26 日 确 立 为 有 效 的<br />

标 准 。2006 年 , 高 级 加 密 标 准 已 然 成 为 对 称 密 钥 加<br />

密 中 最 流 行 的 算 法 之 一 。<br />

AES 的 安 全 性 能 是 良 好 的 。 经 过 多 年 来 的 分 析 和<br />

测 试 , 至 今 没 有 发 现 AES 的 明 显 缺 点 , 也 没 有 找 到 明<br />

显 的 安 全 漏 洞 。AES 能 够 抵 抗 目 前 已 知 的 各 种 攻 击 方<br />

法 的 攻 击 。 因 此 , 普 遍 应 用 在 网 络 通 讯 和 工 业 界 ,<br />

银 行 业 和 行 政 部 门 等 场 合 。 而 AES 的 功 耗 已 成 为 日 渐<br />

突 出 的 问 题 , 必 须 进 行 低 功 耗 的 设 计 。 本 文 主 要 介<br />

绍 AES 加 密 算 法 的 原 理 及 几 种 关 于 AES 低 功 耗 的 处 理<br />

方 法 。<br />

2 AES 的 加 密 算 法 简 介<br />

AES 是 一 个 迭 代 的 、 对 称 密 钥 分 组 的 密 码 , 它<br />

可 以 使 用 128、192 和 256 位 密 钥 , 并 且 用 128 位<br />

(16 字 节 ) 分 组 加 密 和 解 密 数 据 。 与 公 共 密 钥 密 码 使<br />

用 密 钥 对 不 同 , 对 称 密 钥 密 码 使 用 相 同 的 密 钥 加 密<br />

和 解 密 数 据 。 通 过 分 组 密 码 返 回 的 加 密 数 据 的 位 数<br />

与 输 入 数 据 位 数 相 同 。 迭 代 加 密 使 用 一 个 循 环 结<br />

构 , 在 该 循 环 中 重 复 置 换 (permutations) 和 替 换<br />

(substitutions) 输 入 数 据 。<br />

AES 加 密 过 程 是 在 一 个 4×4 的 字 节 矩 阵 上 运<br />

作 , 这 个 矩 阵 又 称 为 “ 体 (state)”, 其 初 值 就 是<br />

一 个 明 文 区 块 ( 矩 阵 中 一 个 元 素 大 小 就 是 明 文 区<br />

块 中 的 一 个 Byte)。 首 先 , 对 128 位 输 入 明 文 进 行<br />

AddRoundKey( 轮 密 钥 加 ) 操 作 。 接 着 ,AES 算 法 主<br />

体 部 分 进 行 Nr-1 次 循 环 。Nr 取 值 10 或 12 或 14, 这 取<br />

决 于 输 入 密 钥 的 长 度 是 128 位 、192 位 还 是 256 位 。<br />

最 常 用 的 是 128 位 长 度 , 本 文 讨 论 128 位 的 情 况 。 各<br />

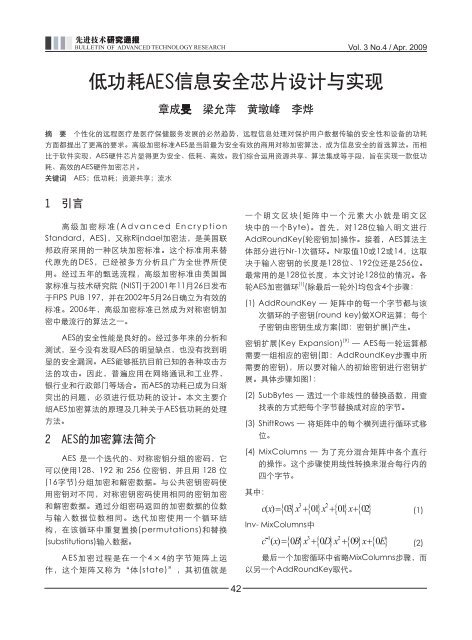

轮 AES 加 密 循 环 [1] ( 除 最 后 一 轮 外 ) 均 包 含 4 个 步 骤 :<br />

(1) AddRoundKey — 矩 阵 中 的 每 一 个 字 节 都 与 该<br />

次 循 环 的 子 密 钥 (round key) 做 XOR 运 算 ; 每 个<br />

子 密 钥 由 密 钥 生 成 方 案 ( 即 : 密 钥 扩 展 ) 产 生 。<br />

密 钥 扩 展 (Key Expansion) [9] — AES 每 一 轮 运 算 都<br />

需 要 一 组 相 应 的 密 钥 ( 即 :AddRoundKey 步 骤 中 所<br />

需 要 的 密 钥 ), 所 以 要 对 输 入 的 初 始 密 钥 进 行 密 钥 扩<br />

展 。 具 体 步 骤 如 图 1:<br />

(2) SubBytes — 透 过 一 个 非 线 性 的 替 换 函 数 , 用 查<br />

找 表 的 方 式 把 每 个 字 节 替 换 成 对 应 的 字 节 。<br />

(3) ShiftRows — 将 矩 阵 中 的 每 个 横 列 进 行 循 环 式 移<br />

位 。<br />

(4) MixColumns — 为 了 充 分 混 合 矩 阵 中 各 个 直 行<br />

的 操 作 。 这 个 步 骤 使 用 线 性 转 换 来 混 合 每 行 内 的<br />

四 个 字 节 。<br />

其 中 :<br />

(1)<br />

Inv- MixColumns 中<br />

(2)<br />

最 后 一 个 加 密 循 环 中 省 略 MixColumns 步 骤 , 而<br />

以 另 一 个 AddRoundKey 取 代 。<br />

42

低 功 耗 AES 信 息 安 全 芯 片 设 计 与 实 现<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

b 0,0 b 0,1 b 0,2 b 0,3<br />

No<br />

change<br />

No<br />

change Shift 1<br />

<br />

Shift 1<br />

Shift 2<br />

<br />

<br />

Shift 2<br />

Shift<br />

<br />

3<br />

<br />

Shift 3<br />

<br />

b 0,1<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

a a a a<br />

a 0,0 a 0,1 a 0,2 a<br />

a 0,3<br />

1,0 a 1,1 a 1,2 a 1,3<br />

SubBytes<br />

b 0,0 b 0,1 b 0,2 b<br />

b 0,3<br />

1,0 b 1,1 b 1,2 b 1,3<br />

a 1,0 a 1,1 a 1,2 a<br />

a 1,3<br />

2,0 a 2,1 a 2,2 a 2,3<br />

SubBytes b 1,0 b 1,1 b 1,2 b<br />

b 1,3<br />

2,0 b 2,1 b 2,2 b 2,3<br />

a 2,0 a 2,1 a a<br />

a 2,2 2,3<br />

3,0 a 3,1 a 3,2 a 3,3<br />

b 2,0 b 2,1 b b<br />

b 2,2 2,3<br />

3,0 b 3,1 b 3,2 b 3,3<br />

a 3,0 a 3,1 a 3,2 a 3,3<br />

b 3,0 b 3,1 b 3,2 b 3,3<br />

S-box<br />

a 0,1<br />

a 0,0<br />

a<br />

a 0,2 a 0,3 S-box<br />

0,1<br />

b 0,0 b 0,2 b 0,3<br />

a 2,0 a 2,1 a 2,2 a 2,3<br />

b 2,0 b 2,1 b 2,2 b<br />

a 2,3<br />

3,0 a 3,2 a b 3,0 b 3,2 b<br />

a 3,3<br />

3,3<br />

3,1 b 3,1<br />

a 3,0 a 3,2 a 3,3<br />

b 3,0 b 3,2 b<br />

a 3,3<br />

3,1 × C(x) b 3,1<br />

b 0,1<br />

a 0,0 a 0,2 a 0,3<br />

b 0,0 b 0,2 b<br />

a<br />

a 1,1<br />

b 0,3<br />

1,0 a 1,2 a<br />

b<br />

1,3 MixColumns<br />

1,1 1,0 b 1,2 b 1,3<br />

a<br />

a 1,1 1,0 a 1,2 a 1,3<br />

b<br />

b<br />

MixColumns<br />

1,1 1,0 b 1,2 b<br />

a b 1,3<br />

2,0 a 2,1 a 2,2 a 2,3<br />

2,0 b 2,1 b 2,2 b 2,3<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

× C(x)<br />

a 1,0 a 1,1 a 1,2 a<br />

a 1,3<br />

2,0 a 2,1 a 2,2 a 2,3<br />

ShiftRows a 1,1 a 1,2 a 1,3 a<br />

a 1,0<br />

2,2 a 2,3 a 2,0 a 2,1<br />

a 0,0 a 0,1 a 0,2 a<br />

a 0,3<br />

1,0 a 1,1 a 1,2 a 1,3<br />

ShiftRows 0,0<br />

a 1,1<br />

0,1<br />

a 1,2<br />

0,2<br />

a 1,3<br />

0,3<br />

a 1,0<br />

a 2,0 a 2,1 a 2,2 a<br />

a 2,3<br />

3,0 a 3,1 a 3,2 a 3,3<br />

a 2,2 a 2,3 a 2,0 a<br />

a a 2,1<br />

3,3 3,0 a 3,1 a 3,2<br />

a 3,0 a 3,1 a 3,2 a 3,3<br />

a 3,3 a 3,0 a 3,1 a 3,2<br />

图 1 AES 系 统 流 程<br />

图 2 AES 加 解 密 系 统<br />

AES 解 密 过 程 [2] : 基 本 上 以 加 密 过 程 的 反 向 顺 序 还<br />

原 每 个 操 作 。 不 过 逆 向 的 操 作 ( 例 如 Inv-SubBytes)<br />

的 顺 序 并 不 是 与 加 密 过 程 中 相 应 的 操 作 的 逆 顺<br />

序 正 好 相 同 。 其 中 值 得 注 意 的 是 加 解 密 过 程 用<br />

的 是 同 一 个 A d d R o u n d K e y 操 作 步 骤 而 不 存 在<br />

InvAddRoundKey 操 作 步 骤 。 另 外 , 解 密 时 每 次 循<br />

环 所 使 用 的 密 钥 正 好 和 加 密 过 程 正 好 相 反 , 从 密 钥<br />

表 的 最 后 一 组 开 始 调 用 。<br />

以 下 为 在 解 密 过 程 中 值 得 主 要 的 两 条 原 则 :<br />

(1) 先 做 I n v M i x C o l u m n s ( 列 混 合 逆 变 换 ) 再 做<br />

A d d R o u n d K e y ( 轮 密 钥 加 ) 时 , 用 来 和 输<br />

入 的 1 2 8 位 的 密 文 做 异 或 的 密 钥 必 须 先 做<br />

InvMixColumns 变 换 。 这 样 得 出 的 结 果 跟 先 做<br />

AddRoundKey 再 做 InvMixColumns 是 一 样 的 。<br />

其 中 这 两 种 操 作 所 用 到 的 密 钥 前 后 保 持 不 变 。<br />

(2) 先 做 InvSubBytes( 字 节 反 变 换 ) 再 做 InvShiftRows( 行<br />

位 移 逆 变 换 ) 和 先 做 I n v M i x C o l u m n s 再 做<br />

InvSubBytes 得 到 的 结 果 是 一 样 的 。<br />

正 因 为 依 据 这 两 点 原 则 ,AES 解 密 过 程 的 步 骤<br />

可 以 调 整 为 跟 加 密 过 程 的 步 骤 顺 序 一 样 , 不 影 响 输<br />

出 的 结 果 。<br />

解 密 的 次 序 调 整 后 , 可 以 发 现 加 密 跟 解 密 的 过 程<br />

中 某 些 的 操 作 步 骤 是 一 样 的 , 可 以 合 并 , 从 而 简 化 电<br />

路 , 减 少 一 些 不 必 要 的 功 耗 , 具 体 示 意 图 如 图 2。<br />

3 CMOS 电 路 功 耗 的 来 源<br />

CMOS 电 路 中 有 两 种 主 要 的 功 耗 来 源 : 静 态 功<br />

耗 和 动 态 功 耗 。 其 中 , 动 态 功 耗 包 括 短 路 电 流 引 起 的<br />

功 耗 ( 称 为 直 流 开 关 功 耗 或 短 路 功 耗 , 发 生 在 跃 变 过<br />

程 中 双 管 同 时 导 通 引 起 的 瞬 态 电 流 而 形 成 的 功 耗 。 对<br />

于 信 号 上 升 ( 下 降 ) 快 的 电 路 , 短 路 电 流 功 耗 很 小 , 但<br />

对 信 号 上 升 ( 下 降 ) 较 慢 的 电 路 , 短 路 电 流 功 耗 可 能 要<br />

占 总 功 耗 的 30% 以 上 ) 和 负 载 电 容 的 功 耗 ( 称 为 交 流 开<br />

关 功 耗 , 由 对 负 载 电 容 充 放 电 电 流 引 起 的 功 耗 ) ; 静<br />

态 功 耗 主 要 是 由 漏 电 流 引 起 的 功 耗 。 一 般 来 说 , 泄 漏<br />

电 流 功 耗 在 总 功 耗 中 所 占 的 比 重 不 到 1%。<br />

43

1,0 1,1 1,2 1,3<br />

1,0 1,1 1,2 1,3<br />

a 2,0 a 2,1 a 2,2 a 2,3<br />

b 2,0 b 2,1 b 2,2 b 2,3<br />

a 3,0 a 3,1 a 3,2 a 3,3<br />

b 3,0 b 3,1 b 3,2 b 3,3<br />

4 低 功 耗 设 计<br />

SubBytes<br />

4.1 动 态 资 源 管 理<br />

b 3,1<br />

a 2,0 a 2,1 a 2,2 a 2,3<br />

b 2,0 b 2,1 b 2,2 b 2,3<br />

× C(x)<br />

a3,0 a3,1 a3,2 a3,3<br />

b3,0 b3,1 b3,2 b3,3<br />

动 No态 功 耗 管 理 是 一 种 系 统 级 低 功 耗 设 计 方 法 ,<br />

a 0,1 a 0,2 a 0,3<br />

S-box<br />

a 0,0<br />

a0,0 a0,2 a0,3<br />

a 1,0 a 1,1 a 1,2 a 1,3<br />

b0,0ShiftRows<br />

b0,2 b0,3<br />

a 1,1 a 1,2 a 1,3 a 1,0<br />

a0,1<br />

b0,1<br />

降 低 功 耗 的 主 要 思 路 是 根 据 芯 片 工 作 状 态 改 变 功 耗 管<br />

a1,1<br />

b1,1<br />

a1,0 a1,2 a1,3 MixColumns b1,0 b1,2 b1,3<br />

理 模 式<br />

Shift<br />

,<br />

2<br />

从 而 在 保 证 性 能 的 基 础 上 降 低 功 耗 。 在 不 同<br />

a<br />

a2,0 2,0 a<br />

a2,2 2,1 a<br />

a2,3 2,3<br />

a<br />

b2,0 b2,2 b2,3 2,2 a 2,3 a 2,0 a 2,1<br />

a2,1<br />

b2,1<br />

模 式 下 , 时 钟 的 频 率 可 以 进 行 调 整 , 一 些 空 闲 模 块<br />

Shift a3,0<br />

3 a3,2 a3,3<br />

b3,0 b3,2 b3,3<br />

a3,1 a 3,0 a 3,1 a 3,2 a 3,3 b3,1 a 3,3 a 3,0 a 3,1 a 3,2<br />

<br />

甚 至 整 个 芯 片 的 时 × 钟 C(x) 也 可 能 会 被 停 止 。 还 可 以 通 过 调<br />

No<br />

a<br />

整 芯 片 的<br />

0,0 a<br />

电<br />

0,1 a<br />

压<br />

0,2 a change<br />

,<br />

0,3<br />

进 一 步 降 低 功 耗 。 由 于 工 作 库 的 限<br />

Shift 1 a 1,0 a 1,1 a 1,2 a 1,3<br />

ShiftRows a 1,1 a 1,2 a 1,3 a 1,0<br />

<br />

制 , Shift 本 2 文 没 有 对 动 态 电 压 管 理 作 进 一 步 的 研 究 。<br />

<br />

Shift 3<br />

a 0,1<br />

b 0,1<br />

a 1,0 a 1,1 3,0<br />

a 1,2 a 1,3<br />

a 3,1<br />

a 3,2 a 3,3<br />

b 1,0 b 1,1 b 1,2 b 1,3<br />

a 0,0 a 0,2 a 0,3<br />

a 1,0<br />

a 1,1<br />

a 1,2 a 1,3 MixColumns<br />

b 1,1<br />

a 2,0 a a 2,3<br />

a 0,0 0,1 a 2,1 0,2 a 0,3<br />

b 0,0 b 0,1 b 0,2 b 0,3<br />

b 2,1<br />

change<br />

Shift 1<br />

<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

a 2,0 a 2,1 a 2,2 a 2,3<br />

a 2,2 a 2,3 a 2,0 a 2,1<br />

a3,0 a3,1 a3,2 a3,3<br />

<br />

4.2 门 控 时 钟<br />

a3,0 a3,1 a3,2<br />

使 能 信 号 EN 有 关 闭 和 打 开 ASIC 内 部 模 块 的 作<br />

用 , 但 EN 只 是 关 闭 了 内 部 模 块 的 功 能 操 作 , 而 并 没<br />

有 把 模 块 内 的 时 钟 网 络 关 闭 , 也 就 是 说 时 钟 网 络 依<br />

然 处 于 激 活 状 态 , 而 时 钟 网 络 造 成 的 功 耗 占 总 功 耗<br />

的 很 大 部 分 , 只 有 关 闭 时 钟 网 络 才 能 同 时 达 到 关 闭<br />

[3]<br />

模 块 功 能 和 降 低 功 耗 的 目 的 。 采 用 时 钟 门 控 技 术<br />

就 可 以 达 到 关 闭 时 钟 网 络 的 目 的 。 图 3 就 是 采 用 了<br />

门 控 时 钟 ,EN 为 时 钟 的 使 能 信 号 , 只 有 当 该 信 号<br />

有 效 时 , 实 际 的 时 钟 输 入 端 才 会 产 生 脉 冲 , 将 数 据<br />

data_in 更 新 到 寄 存 器 中 。<br />

图 3 门 控 时 钟<br />

在 本 设 计 中 , 初 期 采 用 在 语 言 中 加 以 描 述 。 另<br />

外 , 也 可 以 通 过 综 合 工 具 power compiler 自 动 加 入<br />

门 控 时 钟 , 这 部 分 将 在 以 后 的 工 作 中 进 行 。<br />

当 加 入 门 控 时 钟 (clock gate) 有 以 下 作 用 :<br />

a3,3<br />

S-box<br />

b 0,0 b 0,2 b 0,3<br />

b 1,0 b 1,2 b 1,3<br />

a 2,2 b 2,0 b 2,2 b 2,3<br />

b 3,0 b 3,2 b 3,3<br />

(1) 有 效 地 降 低 时 钟 网 络 的 电 容<br />

Vol. 3 No.4 / Apr. 2009<br />

(2) 时 钟 等 效 翻 转 频 率 的 降 低 大 大 降 低 了 寄 存 器 内 部<br />

的 短 路 电 流 功 耗 和 传 输 网 络 的 翻 转 功 耗<br />

(3) D 触 发 器 的 时 钟 输 入 端 口 对 毛 刺 敏 感 , 门 控 单 元<br />

能 有 效 地 滤 除 信 号 EN 的 毛 刺 , 避 免 因 竞 争 而 导<br />

致 触 发 器 发 生 错 误 的 状 态 变 化 。<br />

4.3 流 水 线 (pipeline)<br />

[4]<br />

流 水 线 结 构 把 指 令 划 分 为 多 个 步 骤 , 充 分 利 用<br />

每 个 时 钟 周 期 由<br />

可 知 : 若 整 个 系 统 的 吞<br />

吐 量 不 变 , 则 工 作 电 压 可 以 降 低 N 倍 , 从 而 使 功 耗 降<br />

低 约 N 2 倍 。 但 是 流 水 线 结 构 设 计 的 复 杂 性 高 , 在 设 计<br />

中 插 入 的 寄 存 器 不 但 增 大 了 面 积 , 而 且 增 加 了 时 钟 负<br />

载 电 容 , 导 致 额 外 的 功 耗 浪 费 , 但 总 的 功 耗 降 低 了 。<br />

基 于 以 上 理 论 , 本 文 采 用 5 级 流 水 线 , 具 体 框 架 图 见<br />

图 5。<br />

由 于 本 设 计 刚 刚 完 成 前 端 的 设 计 工 作 , 未 对 其<br />

进 行 后 端 的 设 计 , 无 法 得 到 有 关 于 功 耗 方 面 的 具 体<br />

数 据 。 为 了 证 明 该 方 法 的 可 行 性 , 本 文 对 该 电 路 进<br />

行 如 下 的 估 算 : 假 定 该 电 路 在 5V 电 压 下 可 以 工 作<br />

在 50MHz, 如 果 采 用 如 图 4 流 水 线 使 得 电 路 可 以 工<br />

作 在 80MHz, 那 么 电 路 就 可 以 采 用 较 低 的 工 作 电 压<br />

比 如 3.3V 而 使 得 电 路 依 然 工 作 在 50MHz。 采 用 这 样<br />

的 策 略 , 主 要 目 的 是 将 电 路 的 工 作 频 率 保 持 不 变 ,<br />

使 得 电 路 的 工 作 电 压 降 低 。 假 定 电 路 原 来 的 功 耗 为<br />

, 在 使 用 了 流 水 线 策 略 后 , 因 为 增 加 了<br />

寄 存 器 , 电 路 的 有 效 电 容 增 加 为 1.22C, 此 时 :<br />

由 以 上 估 算 可<br />

见 , 通 过 改 变 电 路 的 体 系 结 构 降 低 电 路 的 工 作 电 压 ,<br />

可 以 极 大 地 降 低 该 电 路 的 功 耗 , 在 此 基 础 上 降 低 电 路<br />

的 工 作 电 压 , 同 样 可 以 提 高 电 路 的 工 作 速 度 。<br />

4.4 资 源 共 享<br />

<br />

图 4 AES 流 水 线 框 架 图<br />

<br />

44

No<br />

change<br />

Shift 1<br />

<br />

Shift 2<br />

<br />

S-box<br />

a 3,0<br />

a 3,1<br />

a 3,2 a 3,3<br />

b 3,0<br />

b 3,1<br />

b 3,2 b 3,3<br />

a 0,0<br />

a 0,1<br />

a 0,2 a 0,3<br />

b 0,0<br />

b 0,1<br />

b 0,2 b 0,3<br />

a 1,0<br />

a 1,1<br />

a 1,2 a 1,3 MixColumns b 1,0<br />

b 1,1<br />

b 1,2 b 1,3<br />

a 2,0 a 2,1 a 2,2 a 2,3<br />

b 2,0 b 2,1 b 2,2 b 2,3<br />

× C(x)<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

a 0,0 a 0,1 a 0,2 a 0,3<br />

a 2,0 a 2,1 a 2,2 a 2,3<br />

a 2,2 a 2,3 a 2,0 a 2,1<br />

a 1,0 a 1,1 a 1,2 a 1,3<br />

ShiftRows a 1,1 a 1,2 a 1,3 a 1,0<br />

基 于 加 解 密 合 并 原 则 , 加 密 跟 解 密 的 过 程 中 的 某<br />

些 操 作 步 骤 ( 如 :subbytes 和 MixColumns) 是 一 样 的<br />

Shift 3<br />

a 3,0 a 3,1 a 3,2 a 3,3<br />

a 3,3 a 3,0 a 3,1 a<br />

可 以 合 并 , 从 而 简 化 电 路 , 减 少 一 些 不 必<br />

3,2<br />

要 的 功 耗 。<br />

<br />

4.4.1 SubBytes 和 Inv-SubBytes<br />

字 节 替 换 (SubBytes) 是 AES 加 解 密 过 程 中 比 较 重<br />

要 的 部 分 , 存 在 有 比 较 大 的 组 合 逻 辑 延 迟 。 传 统 的<br />

设 计 中 , 大 多 数 运 用 有 较 大 延 迟 的 查 找 表 的 方 式 。<br />

在 文 献 [5] 中 采 用 了 二 叉 判 决 图 (BDD), 很 好 地 优 化<br />

了 subbytes 和 invSubbytes 的 设 计 , 从 而 减 少 了 功<br />

耗 及 AES 的 高 速 实 现 。 为 了 更 好 的 使 用 流 水 线 , 采 用<br />

复 合 域 来 实 现 。<br />

低 功 耗 AES 信 息 安 全 芯 片 设 计 与 实 现<br />

时 InvMixColumns 运 算 的 矩 阵 可 以 表 示 为 图 7 的 形<br />

式 , 其 中 MixColumns (Encryption) 是 加 密 时 的 运<br />

算 , 所 以 MixColumns 模 块 的 加 密 硬 件 和 解 密 的 部<br />

分 硬 件 可 以 实 现 复 用 , 从 而 减 小 计 算 复 杂 度 。 图 6<br />

是 本 文 的 MixColumns 模 块 结 构 , 加 密 时 数 据 直 接<br />

通 过 MixColumns (Encryption) 部 分 得 到 结 果 , 而<br />

在 解 密 时 数 据 先 通 过 PreProessing 部 分 , 然 后 再 通<br />

过 MixColumns (Encryption) 部 分 , 完 成 InvMix-<br />

Colums(Decryption) 运 算 。 使 用 上 述 所 描 述 的 特<br />

性 ,InvMixColumns 的 实 现 可 以 与 MixColumns 的<br />

结 构 共 享 。<br />

SubBytes 进 行 的 运 算 包 括 :<br />

(1) 在 不 可 约 多 项 式 为 有 限 域 GF(2 8 ) [5-8] 上 求 乘 逆 ;<br />

(2) 进 行 如 图 5 的 仿 射 变 换<br />

首 先 , 使 用 映 射 函 数 δ 将 域 A 的 所 有 元 素 映 射 到<br />

域 B( 该 步 骤 相 当 于 加 密 过 程 中 的 SubBytes); 其 次 ,<br />

在 域 A 上 计 算 乘 逆 最 后 , 使 用 映 射 函 数 δ -1 将 元 素 映 射<br />

回 域 A( 该 步 骤 相 当 于 解 密 过 程 中 的 Inv-SubBytes 经<br />

对 subbytes 和 inv-subbytes 过 程 )。 进 行 以 上 优 化 ,<br />

总 的 系 统 图 如 图 5。<br />

4.4.2 MixColumns 和 InvMixColumns<br />

和 S u b B y t e s 模 块 对 单 个 字 节 运 算 不 同 ,<br />

MixColumns [10] 模 块 同 时 计 算 32 位 数 据 。 本 文 的<br />

MixColumns 模 块 能 实 现 加 解 和 解 密 操 作 , 还 可<br />

以 实 现 部 分 硬 件 的 复 用 ( 即 资 源 共 享 )。 因 为 在 解 密<br />

5 结 束 语<br />

图 6 MixColumns 模 块 结 构<br />

<br />

图 5 利 用 复 合 域 实 现 subbytes 结 构 框 图<br />

图 7 InvMixColumns 运 算 的 矩 阵<br />

45

Vol. 3 No.4 / Apr. 2009<br />

本 文 采 用 以 上 所 述 方 法 ,AES 前 端 设 计 已 基 本<br />

完 成 。 并 用 Synplify Pro8.2 综 合 ,Xilinx ISE 布 局 布<br />

线 。 目 标 器 件 为 xc4vx40-12ff688, 布 局 布 线 后 的 时<br />

序 报 告 显 示 最 高 工 作 频 率 (Maximum Frequency)<br />

为 135.699MHZ, 资 源 消 耗 1839 Slices,2156 个 4<br />

输 入 LUTs, 最 大 吞 吐 率 (Maximum Throughput) 为<br />

1466.3Mbps。<br />

为 专 用 集 成 电 路 与 系 统 。<br />

李 烨 作 者 简 介 见 本 期 封 2 页 。<br />

在 后 期 工 作 中 , 根 据 DC 综 合 及 时 序 报 告 等 进 行<br />

对 前 端 的 改 进 与 优 化 , 并 采 用 数 字 IC 后 端 设 计 过 程<br />

中 的 一 些 有 关 降 低 功 耗 方 面 的 方 法 , 使 AES 芯 片 在 功<br />

耗 方 面 有 所 降 低 , 真 正 实 现 一 款 低 功 耗 、 高 效 的 AES<br />

硬 件 加 密 芯 片 。<br />

参 考 文 献<br />

[1] Advanced Encryption Standard (AES) [S]. Nov. 26, 2001.<br />

[2] A lireza Hodjat, Ingrid V erbauwhede Speed-area trade-off for 10<br />

to 100 Gbits/s throughput AES processor [C].2003,2147_2150<br />

[3] 董 策 , 杨 志 家 . AES 加 密 算 法 的 高 速 低 功 耗 ASIC 设 计 . 微 计 算<br />

机 信 息 ,2005.21.(9.3)<br />

[4] A nantha P. Chandrakasan, Samuel Sheng and Robert<br />

W.Brodersen. Low power CMOS digital design(R). EECS<br />

Department Technical Report, University of CaliforniaatBerkeley,<br />

1994.<br />

[5] Morioka S, SatohA. An optimized s-box circuit architecture for<br />

low power AES design [C].2003, 1722186.<br />

[6] Paar C. Fast arithmetic architecture for public-key algorithms<br />

over galois fields GF ( (2n)m) [C]. 1997,3632378.<br />

[7] Rudra A, etal. Efficient implementation of rijndael encryption<br />

with composite field arithmetic [C]. 2001, 1752188.<br />

[8] S Morioka, ASatoh A 10 Gbps Fu11-AES Crypto Design with a<br />

Twisted-BDD S-Box Architecture.very large scale integration<br />

system ,july 2004,12(7).<br />

[9] LuCC, Tseng S Y. Integrated design of AES (advanced encryption<br />

standard)encrypter and decrypter[C].2002, 2772285.<br />

[10] KGaj and P Chodowiec. comparison of the hardware performance<br />

of the aes candidates using reconfigurable hardware. Third<br />

Advanced Encryption Standard(AES)Candidate Conf.Apr.2000.<br />

作 者 简 介<br />

章 成 旻 男 , 西 安 电 子 科 技 大 学 研 究 生 , 现 为 深 圳 先<br />

进 技 术 研 究 院 客 座 学 生 , 研 究 方 向 为 数 字 IC<br />

低 功 耗 设 计 。<br />

梁 允 萍 女 , 硕 士 , 毕 业 于 北 京 大 学 , 现 为 深 圳 先 进<br />

技 术 研 究 院 研 究 助 理 , 研 究 方 向 为 数 字 IC 低<br />

功 耗 设 计 。<br />

黄 敦 锋 男 , 电 子 科 技 大 学 硕 士 在 读 , 现 为 中 国 科 学<br />

院 深 圳 先 进 技 术 研 究 院 客 座 学 生 , 研 究 方 向<br />

46