039 Processor Bd Schematic.pdf

039 Processor Bd Schematic.pdf

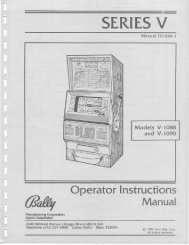

039 Processor Bd Schematic.pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

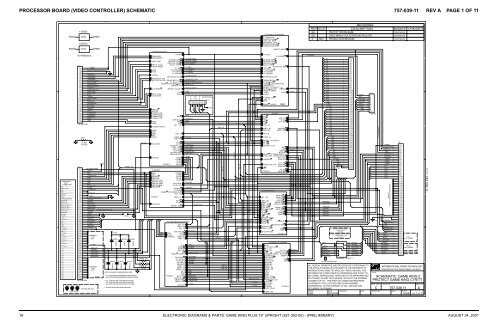

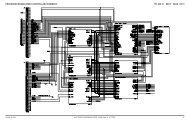

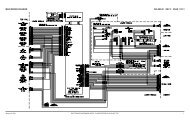

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-<strong>039</strong>-11 REV A PAGE 6 OF 11D(1)(1,2)DOT CLK2BITBLITZ CLKOPTIONALU17VCC 7VPPTP6CEOXC1765D4VCCDINDATA12 CCLKCLK4 DONECERESET/OE31 2U18B474HC14R4810K123C30.1uFR2181 2R2211 20OHM10KR41 210KR1514VCC OUT81 2Y10OHM7GND EN126.667MHz STUFFIFPLLNOTUSED32SC-2E81DOT CLKSC-1(1,7)(1,7)DCBD[0..15](1,2,3,7,10)A[1..31](1,2,3,4,5,7,10)FID4 FID5FORPCB USE ONLYFIDUCIAL+13VDC LOW\(1,8,9)BBSTB(1,2)BLT CLK(1,2)BITBLITZ SEL\(1,2)LPSTB\(1)WR0\(1,2,3,10)WR1\(1,2,3,10)RD\(1,2,3,7,10)RESET\ VIDEO(1,7,9)BLTRDY\(1,2)H SYNC(1)R471 20OHMR141 20OHMNORMALLY NOT STUFFED1 3CR71N914VCCR219R49201 2REF U910K84 pin PLCC Socket (SMT) U111D0 44D1 46D2 41D3 45D4 40D5 42D6 48D7 49D8 50D9 51D10 52D11 53A1 24A2 21A3 27A4 61A5 66A6 16A7 71A8 14A9 73A10 25A11 23A12 28A13 26A14 20A15 19A16 18A17 17A18 1539A20 34A21 355410131175795483E3CR51N91443 22GND VCC164GNDVCCU9XC3142, BitBlitzD0SC-18D1SC-27D2SC-36D3OE-182D4OE-281D5WE-13D6WE-22D7WE-384D8DSF-180D9CAS-178D10CAS-276D11RAS77A1VA062A2VA163A3VA259A4VA360A5VA465A6VA567A7VA668A8VA769A9VA870A10BLANK33A11A12 PWRDN12A13M031A14M132A15A16 BLTRDY9A17 FLATCH130A18 FLATCH229BLANK2 BA047A20BA158A21 BLOCKRW56DOTCLK36RESET HORZ38ADRSTB VERT57BITCLKBLTSEL OSC37LPSTBDSF-2WR0 DIN/256COLOR72WR1CCLK74RDDONE55SC-1SC-2SC-3VA0VA1VA2VA3VA4VA5VA6VA7VA8R421 2220VCCE7JUMPERFORENGINEERING TESTING9874HC32 10U59CVCCR127321K1BB DOT CLK1 21 2VA[0..8]R534.7K1 2VA0VA1VA2VA3VA4VA5VA6VA7VA8TPR2910K1VCC8VCC18VCC32VCC47VCC57VCCVCC64SC I/O 005I/O 017I/O 02102DT/OEI/O 0312I/O 041524WBL/WEL I/O 051725WBU/WEU I/O 0620I/O 0722I/O 084339CASI/O 0945I/O 104826RASI/O 1150I/O 125337A0I/O 135536A1I/O 145835A2I/O 156034A331A4SI/O 00430A5SI/O 01629A6SI/O 02928A7SI/O 031127A8SI/O 0414SI/O 0516SI/O 0619SI/O 072163SESI/O 0844SI/O 0946SI/O 1049SI/O 115140NCSI/O 1254SI/O 1356SI/O 145941DSFSI/O 1561D0D1D2D3D4D5D6D7D8D9D10D11D12D13D14D15VS0VS1VS2VS3VS4VS5VS6VS7VS8VS9VS10VS11VS12VS13VS14VS1538256X16 VDRAMQSF60nS3VSS13VSS23VSS33VSS42VSS52VSS62VSSE6VS[0..15]1 2SC-3VA0VA1VA2VA3VA4VA5VA6VA7VA8TPR110KU11VCC8VCC18VCC32VCC47VCC57VCCVCC64 D0SC I/O 005D1I/O 017D2I/O 02102D3DT/OEI/O 0312D4I/O 041524D5WBL/WEL I/O 051725D6WBU/WEU I/O 0620D7I/O 0722D8I/O 084339D9CASI/O 0945D10I/O 104826D11RASI/O 1150D12I/O 125337D13A0I/O 13553658 D14A1I/O 143560 D15A2I/O 1534A3314 FD0A4SI/O 00306 FD1A5SI/O 01299 FD2A6SI/O 022811 FD3A7SI/O 032714 FD4A8SI/O 0416 FD5SI/O 0519 FD6SI/O 0621 FD7SI/O 076344 FD8SESI/O 0846 FD9SI/O 0949 FD10SI/O 1051 FD11SI/O 114054 FD12NCSI/O 1256 FD13SI/O 1359 FD14SI/O 144161 FD15DSFSI/O 1538QSF256X16 VDRAM60nSE5VSSVSSVSSVSSVSSVSSVSS3132333425262VS0VS1VS2VS3VS4VS5VS6VS7VS8VS9VS10VS11VS12VS13VS14VS15SC-12 1U85DD0DCLK DD0186DD1VS0DD1197DD2VS1DD2208DD3VS2DD3229DD4VS3DD42411DD5VS4DD52512DD6VS5DD62613DD7VS6DD72714VS740VS8 BLOCK2842VS9CA<strong>039</strong>43VS1044VS11NC351VS12NC292VS13NC333VS14NC364VS15NC3734 15 ISP4SC1TDI16 ISP2TMS3817 ISP3C256TCK30 ISP5TDOXC9536, DD CONTROLLERR2710KU48FD0 2D1 Q1FD1 3D2 Q2FD2 4D3 Q3FD3 5D4 Q4FD4 6D5 Q5FD5 7D6 Q6FD6 8D7 Q7FD7 9D8 Q811CLK1 2 1OCR102 10K 74HC574U27FD8 2D1 Q1FD9 3D2 Q2FD10 4D3 Q3FD11 5D4 Q4FD12 6D5 Q5FD13 7D6 Q6FD14 8D7 Q7FD15 9D8 Q811CLK1 2 1OCR67 10K 74HC5742 1111R32 R33 R37 R4110K 10K 10K 10K222ISP[1..6]FD[0..15]19 BD018 BD117 BD216 BD315 BD414 BD513 BD612 BD7BD[0..15]19 BD818 BD917 BD1016 BD1115 BD1214 BD1313 BD1412 BD15note:BD12, BD13, BD14 and BD15are NOT USED or connectedBD12 TPBD13 TPBD14 TPBD15 TPDD[0..7]BLOCKCA0(1,7)(1,7)(1,7)(1,2,7)(1,7)(1,7)CBDWG NO.757 <strong>039</strong> 11(1)(1,4)V SYNCVERTOUT1 3CR41N91413CR61N914374HC32U59A12R1081K12BLANK1FLATCH1FLATCH2BA0BA1BLOCKRW\(1,7)(1,7)(1,7)(1,7)(1,7)(1,7)VBLANK2(1,7)A4VCCU13 U55 U12 U7 U14 U28 U502 1C230.1uF2 1C740.1uF2 1C140.1uF2 1C10.1uF2 1C130.1uF2 1C350.1uF32 1C560.1uF12C360.1uF2 1VSS+ C222uF2ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TOTHE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.TDWSCHEMATIC, GAME KING 2PROTECT GAME KING CTR/TTC1757 <strong>039</strong> 11APPROVEDDATE SCALE01NOV99 NONE SHT__OF__ 6 11DRAWN DATE CHECKEDDATETITLEINTERNATIONAL GAME TECHNOLOGY9295 PROTOTYPE DRIVE RENO, NV 89511DWG. SIZE DWG. NO. REV LTRAAAUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19” UPRIGHT (821-352-00) - (PRELIMINARY) 21

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-<strong>039</strong>-11 REV A PAGE 7 OF 114321(1,2,3,4,5,11)(1,2,3,4,5)(1,2,4,5,11)(1,3)(1,6)(1,6)(1,6)(1,3,10)(1,2,4,11)IO WR\IO RD\PD[0..7]COLORSEL\FLATCH1SC-1BLANK1FWR0B\IA[1..3]D(1,3)(1,6)(1,6)(1,2,3,6,10)(1,2,3,6,10)(1,2,3,4,5,6,10)VBLK1 SEL\BLOCKRW\DD[0..7]D[0..15]RD\A[1..31]VBLK0 SEL\5474HC326U59B13121274HC3274HC0811U59D3U44AD0D1D2D3D4D5D6D7D8D9D10D11D12D13D14D151199876543211998765432U22DIRGA8A7A6A5A4A3A2A1U23DIRGA8A7A6A5A4A3A2A1B8B7B6B5B4B3B2B1B8B7B6B5B4B3B2B111121314151617181112131415161718BK0BK1BK2BK3BK4BK5BK6BK774HC245BK8BK9BK10BK11BK12BK13BK14BK1574HC245FLATCH2BK[0..15]BK0 2BK1 3BK2 4BK3 5BK4 6BK5 7BK6 8BK7 9111U33BL0D1 Q119BL1D2 Q218BL2D3 Q31716 BL3D4 Q415 BL4D5 Q514 BL5D6 Q613 BL6D7 Q712 BL7D8 Q8CLK74HC574OCR742 110KBL[0..15]BL0BL1BL2BL3BL4BL5BL6BL7ENBLK1SC0BL4BL5BL6BL7BL12BL13BL14BL15251114361013151251114361013U341A2A3A4A1B2B3B4BGA/BU491A2A3A4A1B2B3B4B1Y2Y3Y4Y1Y2Y3Y4Y4791274HC25747912PX4PX5PX6PX7PX0PX1PX2PX3PX0PX1PX2PX3PX4PX5PX6PX7PD0PD1PD2PD3PD4PD5PD6PD7IA1IA23233343536373839891011121314151718166U82P0P1P2P3P4P5P6P7D0D1D2D3D4D5D6D7RS0RS1WRRD4202122VCCVCCVCCVCCN/CREDGREENBLUEIREFCOMPVREFOPABLANKPCLKGNDGNDGNDGNDGNDGNDGNDGNDGNDGND23519232441424344125262728293130740TP12VC1201 2VDAC (PLCC)0.1uFC1190.1uFREDGREENBLUEJ1,24BJ1,25BJ1,24ADCB(1,6)VCC(1,6)(1,6)(1,6)(1,6)R751 21KCA0BA0BA1BD[0..15]FD[0..15]FLATCH2FLATCH2BD0BD1BD2BD3BD4BD5BD6BD71 2R105 10KR90BD8BD9BD10BD11FD0FD1FD2FD31 210KFD4FD5FD6FD7FD8FD9FD10FD11FLATCH21 2R68 10K1 2R76234567891112345678911110KFLATCH223456789111U47D1D2D3D4D5D6D7D8CLKOCQ1Q2Q3Q4Q5Q6Q7Q874HC574U43D1D2D3D4D5D6D7D8CLKOC74HC574U28D1D2D3D4D5D6D7D8CLKOCQ1Q2Q3Q4Q5Q6Q7Q8Q1Q2Q3Q4Q5Q6Q7Q874HC57434611131491U35D1D2D3D4D5D6CLKCLR74AC174191817161514131219181716151413121918171615141312PL CA4PL CA3PL CA2PL CA1PL CA0Q1Q2Q3Q4Q5Q6257101215BA2BA3BA4BA5BA6BA7BA8BA9BA10BA11BA12BA13BA14BA15BA16BA17BA18BA19BA20BA21BA22BA23BA24BA25CA0CA1CA2CA3CA4TP1212BA2BA3BA4BA5BA6BA7BA8BA9BA10BA11BA12BA13BA14BA15BA16BA17BA18BA19R7710KBA2BA3BA4BA5BA6BA7BA8BA9BA10BA11BA12BA13BA14BA15BA16BA17BA18BA191R11510K21212111098765272623254282932303112224R7310K12111098765272623254282932303112224R11410KU30BA[2..24]A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)A17(2M)PRG(A18)VPP(A19)CEOEBLOCK LOOKUPU53A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)A17(2M)PRG(A18)VPP(A19)CEOE512KX8 EPROM100nSCA[0..4]D0D1D2D3D4D5D6D7512KX8 EPROM100nSD0D1D2D3D4D5D6D713141517181920211314151718192021BK0BK1BK2BK3BK4BK5BK6BK7REF U3032 pin DIP SocketBK8BK9BK10BK11BK12BK13BK14BK15REF U5332 pin DIP SocketVBLK1 SEL\BLKRW\+VBLK1FWR0B\BL0BL1BL2BL3BA20BA19BA18BA17BA16BA15BA14BA13BA12BA11BA10BA9BA8BA7BA6BA5BA4BA3BA2BA1BA0GNDVBLK0 SEL\BL13FWR1B\256C GNDFLATCH1RESET\BK8BK9BK10BK11BK12BK13BK14BK15FLATCH2VCCJ31 23 4 A15 6 A27 8 A39 10 BL411 12 BL513 14 BL615 16 BL717 18 BL819 20 BK721 22 BK623 24 BK525 26 BK427 28 BK329 30 BK231 32 BK133 34 BK035 36 RD\37 38 BL939 40 BK1541 42 BK1443 44 BK1345 46 BK1247 48 BK1149 50 BK1051 52 BK953 54 BK855 56 BL1057 58 BL1159 60 GND61 62 BL1263 64 BL1465 66 BL1567 68 FLATCH269 70 FLATCH171 72 BLOCKRW\72 Pin SIMMU57219 BL8D1 Q1318 BL9D2 Q2417 BL10D3 Q3516 BL11D4 Q4615 BL12D5 Q5714 BL13D6 Q6813 BL14D7 Q7912 BL15D8 Q811CLK174HC574OCR1232 110K256 EN\SC1ENBLK1 5256 EN\ 40DD0 2DD1 42DD2 4DD3 7DD4 18DD5 19DD6 20DD7 28FLATCH1 13BLANK1 43BLOCK 3CA1 8CA2 9CA3 14CA4 1ENBLK2 12VDAC R\ 22SC0 6E10VCC12R9510KBL8BL9BL10BL11BL12BL13BL14BL15ENBLK2SCO151U24ENBLK1 COLORSELB256 IO_RDDD0 VDAC_WRDD1 IO_WRDD2C256DD3PX0DD4PX1DD5PX2DD6PX3DD7PX4F1PX5BLANK1 PX6BLOCK PX7CA1CA2CA3SC1CA4ENBLK2 TDIVDAC_RD TMSTCKSCOTDO242526271139333435363738294415161730XC9536, PIXEL CONTROLLER251114361013151GA/BU581A2A3A4A1B2B3B4BGA/BR461 210K1Y2Y3Y4Y74HC25747912PX0PX1PX2PX374HC257COLOR SEL\IO RD\VDAC W\IO WR\256COLOR\PX0PX1PX2PX3PX4PX5PX6PX7SC-1ISP5ISP2ISP3ISP6ISP3IA1IA2PD0PD1PD2PD3PD4PD5PD6PD7PX0PX1PX2PX3PX4PX5PX6PX7REF U73OPTIONALIF PLCC PART NOT AVAILABLE5678910111217181920212223242627251528 pin DIP Socket12P0P1P2P3P4P5P6P7DQ0DQ1DQ2DQ3DQ4DQ5DQ6DQ7RS0RS1WRR14715028VCCVSS14R1481 2151%VIDEO VCCVVC820.1uFU73RED1GREEN2BLUE3IREFPCLKBLANKVDAC (DIP)E20241 3131316+-12VV1R17310KQ3LM334CR31N91412+ C8110uF2C1141.0uF1212C12710pF50VDOT CLKR1761 2 BLANK20OHM1212C1080.1uFR1860OHM3AmpsL11 212VCCFERRITE BEAD(1,6)(1,6)R1900OHM3AmpsCBDWG NO.757 <strong>039</strong> 11(1,6)FLATCH2VABA121R10310K2(1,6,9)(1,2,6)(1,3)(1,3,10)(1,6)54R9110K74HC08RESET\ VIDEOISP[1..6]VBLK0 SEL\FWR1B\BLOCK6U44BTP4109131274HC0874HC088U44C11U44DTPTPVCC12+ C5122uF12C320.1uF12C500.1uF12C420.1uF12C290.1uF12C300.1uF12C550.1uF32 1C430.1uF2 1C570.1uFVSS2 1C1230.1uF2 1C520.1uF2 1C450.1uF12C330.1uF12C440.1uF12C730.1uF122C710.1uF12C720.1uFALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TOTHE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.TDWSCHEMATIC, GAME KING 2PROTECT GAME KING CTR/TTC1757 <strong>039</strong> 11APPROVEDDATE SCALE01NOV99 NONE SHT__OF__ 7 11DRAWN DATE CHECKEDDATETITLEPX[0..7]INTERNATIONAL GAME TECHNOLOGY9295 PROTOTYPE DRIVE RENO, NV 89511DWG. SIZE DWG. NO. REV LTR(1)AA22 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19” UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

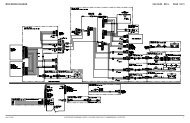

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-<strong>039</strong>-11 REV A PAGE 8 OF 114321VDDDDR203470K(1,9)211R210470KR213470K2211R204470KCARDCAGE DET\2R2091 2100K12U66A407133U75A408112CC-OPENMD-OPENCCAGE OPEN\DDOOROPEN\(1,4,9)(1,4,9)(1,9)(1,9)DROPDOOR DET\MAINDOORDET\R2021 2100KR2011 25689U66B4071U66C40714104U75BVDD1 2R152 1K40814512139156U71D0D1D2D3CLKCLR40175Q0Q0Q1Q1Q2Q2Q3Q32376101115141 2R125 1KU652I14I26I310I412I514I61DA15DB4503O1O2O3O4O5O6357911131413121191071215U70D0D1D2D3DDADDBCLKODAODBRSTQ0Q1Q2Q334564076MDOOROPEN\BVAL OPEN\(1,4,9)(1,4,9)C(1,9)(1,4,9)(1,4,9)(1,4,9)(1,4,9)(1,6,9)BILLVAL DET\TT-CNTR1TT-CNTR2TT-DISABLE\INTERROGATE+13VDC LOW\RP14470KVDD1 82 73 64 512R107470K100KR2141 2100K1213U66D40711110U75C11U75D4081408189121312U83A400131 2R133 1KU67A2A3B1E4556U67B14A13B15E4556Q0Q1Q2Q3Q0Q1Q2Q345671211109TPTPTPTPCC-OPENMD-OPENR1541 20OHMR1531 20OHMVDD2 1R18310KSTUFF R154 FOR CARD CAGE ALARM (DEFAULT)STUFF R153 FOR MAIN DOOR ALARMR1841 2TT-DET\(1,4,9)CDWG NO.757 <strong>039</strong> 11100KB(9)TT-BACKUP2 1C860.1uFVDDU36 U41U92 U60 U25 U61 U50 U3512C870.1uF12+ C6210uF12C910.1uF12C780.1uF12C1160.1uF12C980.1uF12C990.1uF12C1000.1uF1 2R15710K1 2R15810KR1371 2390KC1021000pF1122 1U83B540016R155200K489U83C400110R1821 2100132Q6MOSFET NDOORVAL OUT(1,9)BU37VSSC921R14247K2191011126715143ABCD8_BYCINHSMONOOINHIN1RO1O2DO4513U68R1712 11K1213U83D4001111000pF21 2R1611K1 2R1591K1 2R1361K1 2R1561K1 2R1451K24536A432ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TOTHE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.TDWSCHEMATIC, GAME KING 2PROTECT GAME KING CTR/TTC1757 <strong>039</strong> 11APPROVEDDATE SCALE01NOV99 NONE SHT__OF__ 8 11DRAWN DATE CHECKEDDATETITLEINTERNATIONAL GAME TECHNOLOGY9295 PROTOTYPE DRIVE RENO, NV 89511DWG. SIZE DWG. NO. REV LTRAAAUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19” UPRIGHT (821-352-00) - (PRELIMINARY) 23

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-<strong>039</strong>-11 REV A PAGE 9 OF 114321REF U84B1HEAT SINKVDDVCCE21REF U84AREF U84B3HEATSINK COUMPOUND112FOREXTERNALPOWERSUPPLYVCCR121 2D(1)J2,1A/1B+13VDC1HEAT SINKREF U84B2U841+VINGNDOFFCLIPFDBOUT42VCC OUT2VCC OUT12REMOVE E27 WHEN USING ANEXTERNAL POWER SUPPLYL212R1720OHM3AmpsU64A24010614U64B40106313.3K1C11TP1234FO1+D2R21512+ C93100uF25V2 1C118.01uF35LM2576T-5.0D41N58232 1100uH2 1+ C1071000uF25V2 1C122.01uF2 1D31N63731N6373R21 51.25W1 2C102.01uF12HFBR-2522FO2C+13VDC(1,4)(1,4)OPTIONALVCCR1201 210K1ARxDdTxDd32Q12N3904U721VIN NC82VOUT VOUT73VOUT VOUT64ADJ NC5LM317TPTPTPTPTPR1221 251012345687TPTPU690OHM3AmpsCHGDCHGPFNMMNCMNSEL0SEL1VSSICS1722NR1431 239R1261 2430VDDN/CVINOPRFAUX1AUX0RCMRN161514131211109CR21 3VCCTPTPTPTP1N914132Q22N3904OPTIONALR1462 151K VCCR1632 1C106 15K100pF121 2R112391 21 2R110680KR111330K12D21 3SchottkyBT23.6VNiCadVCC13D1SchottkyR1211 21M1%R521 2100K1%VCC2 1 2 1R3510KR441 222MR431M1%U121OUT1 V+82HYS1 OUT273SET1 SET264GND HYS25ICL7665VCCR451 222MVCC2 1 2 1R4010KR391 21M1%R381M1%R361 2100K1%U63124675754532 1R341 21KC180.1uF2TP1000pF2 1BT13.0VLithiumHFBR-1522OPTIONALTT BAT LOW\SRAM BAT LOW\OPTIONAL COMPONENTS TO BE USED ONLYWHEN BT1 IS NOT INSTALLED.CR1R221 2 1 22 1100 1N5818R1310K(1,4)(1,4)VCCCB(1,8)(1,3)TT-BACKUPWCHDOG SEL\R1191 20OHM+13VDC2 1 2 1R14047KR1396.04K1%2 1C8847pF11R1091KR1411 2330KVCC U63311391178R1341KVCC BATT/NVBATT VOUTCE OUTCE INLOW LNPFIRESETWDIRESETOSC IN WDOOSC SL4GNDPFO5212615161410TPTPSupervisory (691)VCC2 1R13810KU64C5 6U56A401061 240106U64DU64E9 811 104010640106U56F13 1240106U56B3 4VBATTRESET QUARTRESET MEZZRESET CPLD/F/OVOUTCE\OUTRESET\ CPU/SEN/AUDINT2RESET\ SIMM(1,3)(1,4)(1)(1,2)(1,3,10)(1,3)(1,2,4,5,11)(1,2)(3,10)BDWG NO.757 <strong>039</strong> 112240106U56C(1,4,8)(1,4,8)TT-DISABLE\INTERROGATE8) TellTaleTT-DISABLEINTERROGATETT-BACKUPTT-DETU56D9 8401065 640106RESET\ I/ORESET\ VIDEO(1,4)(1,6,7)TT-CNTR1(1,8)DROPDOOR DET\DROPDOOR DETTT-CNTR2PA RESET\(1)(1,8)(1,8)(1,8)MAINDOORDET\BILLVAL DET\DOORVAL OUTMAINDOORDETBILLVAL DETDOORVAL OUT+13VDC LOWBVAL OPENMDOOROPENDDOOROPENCCAGE OPEN+13VDC LOW\BVAL OPEN\MDOOROPEN\DDOOROPEN\CCAGE OPEN\TT-DET\(1,6,8)(1,4,8)(1,4,8)(1,4,8)(1,4,8)(1,4,8)(1,8)CARDCAGE DET\CARDCAGE DETTT-CNTR1(1,4,8)PAGE 8TT-CNTR2(1,4,8)AVCC4U222 1C680.1uFU692 1VSSC770.1uF12C220.1uF12C800.1uF12C790.1uF3TP2 1U56E11 1040106R11610KTP2ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TOTHE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO ORAPPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.TDWSCHEMATIC, GAME KING 2PROTECT GAME KING CTR/TTC1757 <strong>039</strong> 11APPROVEDDATE SCALE01NOV99 NONE SHT__OF__ 9 11DRAWN DATE CHECKEDDATETITLEINTERNATIONAL GAME TECHNOLOGY9295 PROTOTYPE DRIVE RENO, NV 89511DWG. SIZE DWG. NO. REV LTRAA24 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19” UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-<strong>039</strong>-11 REV A PAGE 10 OF 114321(1,2,3,6,7)D[0..15](1,2,3,4,5,6,7)A[1..31](3)(3)(1,3,9)(3)(3)(1,2,3,6,7)SRAM WE0\SRAM WE1\VOUTSRAM CE\SRAM OE\RD\GAMEU13A18SRAMU15U14BITDA1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A18A19121110987652726232542829323031A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)A17(2M)PRG(A18)D0D1D2D3D4D5D6D71314151718192021D0D1D2D3D4D5D6D7REF U1332 pin DIP SocketA1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A19121110987652726232542833121A0 D0A1 D1A2 D2A3 D3A4 D4A5 D5A6 D6A7 D7A8A9A10A11A12 VCCA13A14 CE2/A17A15A16NC/A1813141517181920213230D0D1D2D3D4D5D6D7VOUTA18REF U1532 pin DIP Socket2 1C160.1uFA1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A18A19121110987652726232542829323031A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)A17(2M)PRG(A18)D0D1D2D3D4D5D6D71314151718192021D0D1D2D3D4D5D6D7REF U1432 pin DIP SocketDA201VPP(A19)A201VPP(A19)2224CEOE292224WECE1/CSOE2224CEOE(1,3)GAME SEL\1MX8 EPROMU36512KX8 SRAMU381MX8 EPROMU37CA1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A18A19121110987652726232542829323031A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)A17(2M)PRG(A18)D0D1D2D3D4D5D6D71314151718192021D8D9D10D11D12D13D14D15REF U3632 pin DIP SocketA1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A19121110987652726232542833121A0 D0A1 D1A2 D2A3 D3A4 D4A5 D5A6 D6A7 D7A8A9A10A11A12 VCCA13A14 CE2/A17A15A16NC/A1813141517181920213230D8D9D10D11D12D13D14D15VOUTA18REF U3832 pin DIP Socket2 1C390.1uFA1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16A17A18A19121110987652726232542829323031A0A1A2A3A4A5A6A7A8A9A10A11A12A13A14A15A16(1M)A17(2M)PRG(A18)D0D1D2D3D4D5D6D71314151718192021D8D9D10D11D12D13D14D15REF U3732 pin DIP SocketCA201VPP(A19)A201VPP(A19)2224CEOE292224WECE1/CSOE2224CEOE1MX8 EPROM512KX8 SRAM1MX8 EPROM(1,3)VBIT SEL\B(3)(3)(3)(1,3)(1,3)(3,9)XM1 SEL\XM2 SEL\XM3 SEL\FWR0A\FWR1A\RESET\ SIMMFWR0A\SRAM WE0\FWR0B\FWR1A\SRAM WE1\FWR1B\VCCVCCVCCJ6J7J81 21 21 23 4 XM1 SEL\FWR0A\ 3 4 XM1 SEL\FWR0A\ 3 4 XM1 SEL\5 6 XM2 SEL\SRAM WE0\ 5 6 XM2 SEL\SRAM WE0\ 5 6 XM2 SEL\7 8 GAME SEL\FWR0B\ 7 8 GAME SEL\FWR0B\ 7 8 GAME SEL\A25 9 10 SRAM CE\A25 9 10 SRAM CE\A25 9 10 SRAM CE\A24 11 12 VBIT SEL\A24 11 12 VBIT SEL\A24 11 12 VBIT SEL\A23 13 14 WR0\A23 13 14 WR0\A23 13 14 WR0\A22 15 16 WR1\A22 15 16 WR1\A22 15 16 WR1\A21 17 18 XM3 SEL\A21 17 18 XM3 SEL\A21 17 18 XM3 SEL\A20 19 20 D7A20 19 20 D7A20 19 20 D7A19 21 22 D6A19 21 22 D6A19 21 22 D6A18 23 24 D5A18 23 24 D5A18 23 24 D5A17 25 26 D4A17 25 26 D4A17 25 26 D4A16 27 28 D3A16 27 28 D3A16 27 28 D3A15 29 30 D2A15 29 30 D2A15 29 30 D2A14 31 32 D1A14 31 32 D1A14 31 32 D1A13 33 34 D0A13 33 34 D0A13 33 34 D0A12 35 36 RD\A12 35 36 RD\A12 35 36 RD\A11 37 38 SRAM OE\A11 37 38 SRAM OE\A11 37 38 SRAM OE\A10 39 40 D15A10 39 40 D15A10 39 40 D15A9 41 42 D14A9 41 42 D14A9 41 42 D14A8 43 44 D13A8 43 44 D13A8 43 44 D13A7 45 46 D12A7 45 46 D12A7 45 46 D12A6 47 48 D11A6 47 48 D11A6 47 48 D11A5 49 50 D10A5 49 50 D10A5 49 50 D10A4 51 52 D9A4 51 52 D9A4 51 52 D9A3 53 54 D8A3 53 54 D8A3 53 54 D8A2 55 56 XM4 SEL\A2 55 56 XM4 SEL\A2 55 56 XM4 SEL\A1 57 58 SIMMRDY\A1 57 58 SIMMRDY\A1 57 58 SIMMRDY\GND 59 60 GND GND 59 60 GND GND 59 60 GND61 62 A31FWR1A\ 61 62 A31FWR1A\ 61 62 A3163 64 VOUT63 64 VOUTSRAM WE1\ 63 64 VOUT65 66 A30FWR1B\ 65 66 A30FWR1B\ 65 66 A30A26 67 68 A29A26 67 68 A29A26 67 68 A29A27 69 70 A28A27 69 70 A28A27 69 70 A2871 72 XMB SEL\RESET\ 71 72 XMB SEL\RESET\ 71 72 XMB SEL\72 Pin SIMM72 Pin SIMM72 Pin SIMMSRAM WE1\BDWG NO.757 <strong>039</strong> 11(1,3,7)(1,3,7)FWR0B\FWR1B\A(3)(1,2,3,6)(1,2,3,6)(2)(3)XMB SEL\WR0\WR1\SIMMRDY\XM4 SEL\4VCC12C370.1uF12C170.1uF12C380.1uF12C150.1uF32ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TOTHE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.TDWSCHEMATIC, GAME KING 2PROTECT GAME KING CTR/TTC1757 <strong>039</strong> 11APPROVEDDATE SCALE01NOV99 NONE SHT__OF__ 10 11DRAWN DATE CHECKEDDATETITLEINTERNATIONAL GAME TECHNOLOGY9295 PROTOTYPE DRIVE RENO, NV 89511DWG. SIZE DWG. NO. REV LTRAAAUGUST 24, 2001 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19” UPRIGHT (821-352-00) - (PRELIMINARY) 25

PROCESSOR BOARD (VIDEO CONTROLLER) SCHEMATIC 757-<strong>039</strong>-11 REV A PAGE 11 OF 114321(4)(1,3,4)OUT CLKOUT SEL\28070000h4574AC326U19BPD0PD1PD2PD3451213U51D1D2D3D4Q1Q1Q2Q2Q3Q3Q4Q4237610111514TPTPTPTPE23E24E25E16PADPADPADPADRESET\91CLKCLR74HC1751111DR10610KR22210KR22310KR22410KD(1,2,4,7)J4,27C(1,2,4,5,7)(1,2,3,4,5,7)(1,2,4,5,9)(1,3,4)Audio Pre-Amp PowerC(1)(1,4)J2,1A\1BAJ5,21CBAUDIOAUDIOAUDIOYM2413E18YM2413 XOUTAUDIOC6615pFCDWG NO.(1)J1,18A/18B1R16722KAUDIO757 <strong>039</strong> 11AUDIO222C94+2.2uF10V12R14410K112+ C694.7uFC651 20.1uFC841 2 1+2.2uF10VC831 2 1+2.2uF10VR1322.2K1R1312.2K2R1661 222KC961 2+10uF35VC892.001uF1B(1,4)SPEAKERA+J2,4AREF U79A3C1212 1+1000uF25V15LM1875+4-3AUDIOAUDIOR1641 2150KU79121C951 21.0uFAUDIO2R135110K+AUDIOBR1621OHMAUDIO1C1100.22uF(1,4)J2,3A222222IA1PD[0..7]IO WR\RESET\ CPU/SEN/AUDSOUND SEL\12R2160OHM3Amps+13VDC12MM AUDIO112R2070OHM3Amps+ C594.7uF3U50VIGND2VO1LM340LAZ-5.0R13022.2KR12922.2K121U551GND VCC1615PD0RO D01714PD1MO D11813PD2IC D2212PD3CS D33114 PD4WE D45 PD5YM2413 XIND586 PD6XIN D67 PD7D7910 IA1XOUT A0Y41 23.579 MHzC6715pF1222 1C850.1uF+25VDC2 1C1150.1uF2 1+ C97100uF25VR1511 222KE1978-6LM358 54U54B18-2LM358+ 3U54A42 1+ C902.2uF10V1 2 1R12410KR12810KHEATSINK COUMPOUNDR16510K21+ C11110uFR1801 20OHMAUDIO2REF U79A1REF U79A2HEAT SINKCLIPSPEAKER-VCCA412C600.1uF2 13C750.1uF2ALL DESIGN, OPERATIVE AND PROCESS DATA PERTAINING TOTHE ARTICLE SHOWN ON THIS SHEET IS THE PROPERTY OFINTERNATIONAL GAME TECHNOLOGY, RENO, NEVADA, THISINFORMATION IS DISCLOSED IN CONFIDENCE AND IS NOT TOBE COPIED, REPRODUCED, REVEALED TO OR APPROPRIATEDBY OTHERS, IN PART OR IN WHOLE, WITHOUT THE EXPRESSCONSENT OF IGT. THIS PRINT IS LOANED AND RECIPIENTCOVENANTS IT WILL NOT BE USED IN ANY MANNERDETRIMENTAL TO THE INTEREST OF IGT, AND MUST BERETURNED ON DEMAND.TDWSCHEMATIC, GAME KING 2PROTECT GAME KING CTR/TTC1757 <strong>039</strong> 11APPROVEDDATE SCALE01NOV99 NONE SHT__OF__ 11 11DRAWN DATE CHECKEDDATETITLEINTERNATIONAL GAME TECHNOLOGY9295 PROTOTYPE DRIVE RENO, NV 89511DWG. SIZE DWG. NO. REV LTRAA26 ELECTRONIC DIAGRAMS & PARTS: GAME KING PLUS 19” UPRIGHT (821-352-00) - (PRELIMINARY) AUGUST 24, 2001