Two Weeks Certified Summer Internship Program - VIT University

Two Weeks Certified Summer Internship Program - VIT University

Two Weeks Certified Summer Internship Program - VIT University

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

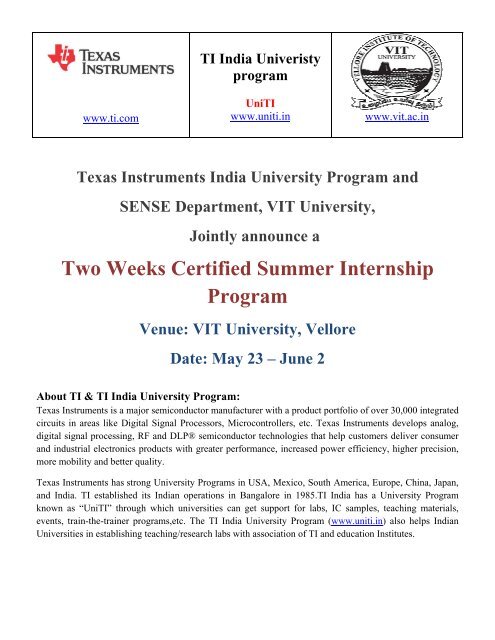

www.ti.com<br />

TI India Univeristy<br />

program<br />

UniTI<br />

www.uniti.in<br />

www.vit.ac.in<br />

Texas Instruments India <strong>University</strong> <strong>Program</strong> and<br />

SENSE Department, <strong>VIT</strong> <strong>University</strong>,<br />

Jointly announce a<br />

<strong>Two</strong> <strong>Weeks</strong> <strong>Certified</strong> <strong>Summer</strong> <strong>Internship</strong><br />

<strong>Program</strong><br />

Venue: <strong>VIT</strong> <strong>University</strong>, Vellore<br />

Date: May 23 – June 2<br />

About TI & TI India <strong>University</strong> <strong>Program</strong>:<br />

Texas Instruments is a major semiconductor manufacturer with a product portfolio of over 30,000 integrated<br />

circuits in areas like Digital Signal Processors, Microcontrollers, etc. Texas Instruments develops analog,<br />

digital signal processing, RF and DLP® semiconductor technologies that help customers deliver consumer<br />

and industrial electronics products with greater performance, increased power efficiency, higher precision,<br />

more mobility and better quality.<br />

Texas Instruments has strong <strong>University</strong> <strong>Program</strong>s in USA, Mexico, South America, Europe, China, Japan,<br />

and India. TI established its Indian operations in Bangalore in 1985.TI India has a <strong>University</strong> <strong>Program</strong><br />

known as “UniTI” through which universities can get support for labs, IC samples, teaching materials,<br />

events, train-the-trainer programs,etc. The TI India <strong>University</strong> <strong>Program</strong> (www.uniti.in) also helps Indian<br />

Universities in establishing teaching/research labs with association of TI and education Institutes.

About <strong>VIT</strong> <strong>University</strong>:<br />

Founded in 1984 as Vellore Engineering College, the institute was declared a <strong>University</strong> in recognition of<br />

its academic excellence by the Ministry of Human Resources Development, Government of India in 2001.<br />

The <strong>University</strong> has since grown by leaps and bounds – establishing excellent infrastructure spread over an<br />

impeccacably clean and green 300 acre campus - on way to fulfill the vision of the founder and Chancellor<br />

Dr. G. Viswanathan to make it truly world class. <strong>VIT</strong> today comprises of six constituent Schools and<br />

interdisciplinary Centers offering undergraduate, post graduate and research programs upto Ph.D level. <strong>VIT</strong><br />

holds the ISO 9002 certified by the DNV of the Netherlands. It is again accredited from IEE (UK). Further<br />

it has also been accredited by NBA (AICTE) and NAAC (UGC). In the Last seven years, <strong>VIT</strong> had more<br />

than 100 visiting professors, some of them staying 6 to 12 weeks for offering accelerated courses as well as<br />

participating in Workshops and Seminars for the benefit of students of <strong>VIT</strong> and also the industry around.<br />

About the School of Electronics Engineering<br />

The School offers B.Tech [ECE] and five M.Tech programs. Facilities for research leading to Ph.D. are<br />

available in many emerging areas. A major emphasis in both the undergraduate and post graduate program<br />

is teaching and learning process. School is actively involved in R&D activities and has sponsored projects<br />

from various agencies like DST, ISRO (RESPOND), and BRNS etc. It has MOU’s with industries and other<br />

reputed institution and R&D organization of our country and other parts of the world.<br />

About VLSI design Lab<br />

The VLSI Design Laboratory is equipped with<br />

• ASIC DESIGN LAB supported by CADENCE (Cadence Tools with 60 User License)<br />

• FPGA/SOPC Lab supported by ALTERA<br />

• MENTOR GRAPHICS Tools with 60 User License<br />

• ANALOG SYSTEM DESIGN LAB supported by TEXAS INSTRUMENTS<br />

This lab is being utilized by Engineers from VLSI, Embedded, Sensors and Mechatronics divisions for<br />

innovations in their Academic as well as Research projects<br />

About Workshop:<br />

Designing Analog Systems Using ASLK kit<br />

Analog System Design has become important in the design of embedded systems. The goal of this training<br />

is to provide Students/ Faculty an exposure to the fascinating world of analog and mixed-signal signal<br />

processing. As part of the training the participants can build analog<br />

systems using analog ICs and study their macro models,<br />

characteristics and limitations. This workshop focuses on system<br />

design along with basic circuit design. In this workshop, the intention<br />

is to expose the participants to the concepts of Analog System Design.<br />

The workshop will include<br />

a. Lectures from TI’ers/faculty from <strong>VIT</strong> <strong>University</strong>.<br />

b. Hands-on experiments on TINA simulation software and the<br />

Analog System Lab Kit.<br />

c. Design Challenge for the participants.<br />

d. Certificates will be awarded on successful completion of the<br />

internship.

The workshop will be suitable for students & faculty members of Electronics/ Telecommunication/<br />

Electrical/ Instrumentation/ Biomedical engineering who have taken a course on Linear Integrated Circuits.<br />

It is expected that the participants will be exposed to the concepts of Operational Amplifiers and Linear ICs.<br />

The participants must have used at least one device-level simulation tool.<br />

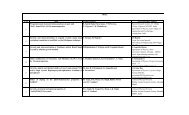

<strong>Internship</strong> Details:<br />

This is an excellent opportunity to understand the industrial trends in Analog System Design and get handson<br />

experience in the design, simulation and hardware implementation of analog subsystems. The following<br />

topics will be covered.<br />

Registration:<br />

� Exposure to TINA Simulation Software<br />

� Exposure to Macromodels<br />

� Exposure to Analog System Lab Kit<br />

� Design, Simulation, and Implementation of analog<br />

subsystems such as<br />

o Second-order filters<br />

o Self-tuned filters<br />

o Voltage-controlled oscillators (VCO)<br />

o Function generators<br />

o Phase-locked loop (PLL)<br />

o Automatic gain control (AGC)<br />

o DC-DC converter<br />

o Low Drop Out (LDO) regulator<br />

The workshop is open to<br />

� Faculty from Institutions teaching Analog System Design.<br />

� Engineering Students (both UG & PG level)<br />

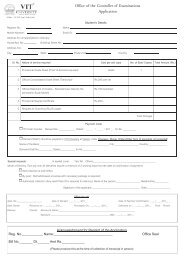

Registration form can be downloaded from the following link:<br />

https://docs.google.com/document/d/1o1TTgbQ9X9dLL4LkkLWCB5qUlgIvRRMx06_rlyT_59c/edit<br />

Please fill out the registration form and send a scanned copy of the registration form and a scanned copy of<br />

the DD to Vaibhav Ostwal (ostwalvaibhav@ti.com) with the subject line “TI-<strong>VIT</strong> <strong>Summer</strong> <strong>Internship</strong>-<br />

Analog” and mark a copy to Prof. Sakthivel (rsakthivel@vit.ac.in). The payment (DD) must be made in the<br />

name of <strong>VIT</strong> <strong>University</strong>, payable at Vellore.<br />

Last day for registration is May 19, 2012. Registrations will be confirmed through e-mail by May 21,<br />

2012.

Registration Fee:<br />

With Accommodation Without Accommodation<br />

Students Rs.5000 Rs.2500<br />

Faculty Members Rs.6000 Rs.3000<br />

Contact details:<br />

Please contact Mr. R.Sakthivel, Assistant Professor, <strong>VIT</strong> <strong>University</strong>, 09994627570 for queries regarding<br />

hostel/hotel accommodation during the days of the workshop. For any queries regarding the workshop<br />

please write to Vaibhav Ostwal ostwalvaibhav@ti.com or call 080-25048335

![[26th â 30th Oct 2009] - Result - VIT University](https://img.yumpu.com/48486076/1/184x260/26th-a-30th-oct-2009-result-vit-university.jpg?quality=85)