VR4100 Series 64-/32-bit Microprocessor Architecture UM - PDAdb

VR4100 Series 64-/32-bit Microprocessor Architecture UM - PDAdb

VR4100 Series 64-/32-bit Microprocessor Architecture UM - PDAdb

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

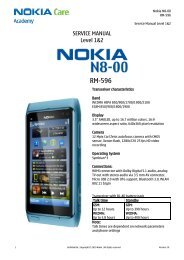

User’s Manual<strong>VR4100</strong> <strong>Series</strong><strong>64</strong>-/<strong>32</strong>-<strong>bit</strong> <strong>Microprocessor</strong><strong>Architecture</strong>Target DeviceµPD30121 (VR4121 TM )µPD30122 (VR4122 TM )µPD30131 (VR4131 TM )µPD30181 (VR4181 TM )µPD30181A, 30181AY (VR4181A TM )Document No. U15509EJ2V0<strong>UM</strong>00 (2nd edition)Date Published June 2002 NS CP(K)© NEC Corporation 2002© MIPS Technologies, Inc. 1997, 2001Printed in Japan

[MEMO]2User’s Manual U15509EJ2V0<strong>UM</strong>

NOTES FOR CMOS DEVICES1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORSNote:Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide andultimately degrade the device operation. Steps must be taken to stop generation of static electricityas much as possible, and quickly dissipate it once, when it has occurred. Environmental controlmust be adequate. When it is dry, humidifier should be used. It is recommended to avoid usinginsulators that easily build static electricity. Semiconductor devices must be stored and transportedin an anti-static container, static shielding bag or conductive material. All test and measurementtools including work bench and floor should be grounded. The operator should be grounded usingwrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions needto be taken for PW boards with semiconductor devices on it.2 HANDLING OF UNUSED INPUT PINS FOR CMOSNote:No connection for CMOS device inputs can be cause of malfunction. If no connection is providedto the input pins, it is possible that an internal input level may be generated due to noise, etc., hencecausing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levelsof CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unusedpin should be connected to VDD or GND with a resistor, if it is considered to have a possibility ofbeing an output pin. All handling related to the unused pins must be judged device by device andrelated specifications governing the devices.3 STATUS BEFORE INITIALIZATION OF MOS DEVICESNote:Power-on does not necessarily define initial status of MOS device. Production process of MOSdoes not define the initial operation status of the device. Immediately after the power source isturned ON, the devices with reset function have not yet been initialized. Hence, power-on doesnot guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until thereset signal is received. Reset operation must be executed immediately after power-on for deviceshaving reset function.VR10000, VR12000, VR4000, VR4000 <strong>Series</strong>, <strong>VR4100</strong>, <strong>VR4100</strong> <strong>Series</strong>, VR4110, VR4120, VR4121, VR4122,VR4130, VR4131, VR4181, VR4181A, VR4300, VR4305, VR4310, VR4400, VR5000, VR5000A, VR54<strong>32</strong>, VR5500,and VR <strong>Series</strong> are trademarks of NEC Corporation.MIPS is a registered trademark of MIPS Technologies, Inc. in the United States.MC68000 is a trademark of Motorola Inc.IBM370 is a trademark of IBM Corp.Pentium is a trademark of Intel Corp.DEC VAX is a trademark of Digital Equipment Corp.UNIX is a registered trademark in the United States and other countries, licensed exclusively throughX/Open Company, Ltd.User’s Manual U15509EJ2V0<strong>UM</strong> 3

Purchase of NEC I 2 C components conveys a license under the Philips I 2 C Patent Rights to use thesecomponents in an I 2 C system, provided that the system conforms to the I 2 C Standard Specification as definedby Philips.Exporting this product or equipment that includes this product may require a governmental license from the U.S.A. for somecountries because this product utilizes technologies limited by the export control regulations of the U.S.A.• The information in this document is current as of April, 2002. The information is subject to changewithout notice. For actual design-in, refer to the latest publications of NEC's data sheets or databooks, etc., for the most up-to-date specifications of NEC semiconductor products. Not all productsand/or types are available in every country. Please check with an NEC sales representative foravailability and additional information.• No part of this document may be copied or reproduced in any form or by any means without priorwritten consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.• NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights ofthird parties by or arising from the use of NEC semiconductor products listed in this document or any otherliability arising from the use of such products. No license, express, implied or otherwise, is granted under anypatents, copyrights or other intellectual property rights of NEC or others.• Descriptions of circuits, software and other related information in this document are provided for illustrativepurposes in semiconductor product operation and application examples. The incorporation of thesecircuits, software and information in the design of customer's equipment shall be done under the fullresponsibility of customer. NEC assumes no responsibility for any losses incurred by customers or thirdparties arising from the use of these circuits, software and information.• While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customersagree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimizerisks of damage to property or injury (including death) to persons arising from defects in NECsemiconductor products, customers must incorporate sufficient safety measures in their design, such asredundancy, fire-containment, and anti-failure features.• NEC semiconductor products are classified into the following three quality grades:"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor productsdeveloped based on a customer-designated "quality assurance program" for a specific application. Therecommended applications of a semiconductor product depend on its quality grade, as indicated below.Customers must check the quality grade of each semiconductor product before using it in a particularapplication."Standard": Computers, office equipment, communications equipment, test and measurement equipment, audioand visual equipment, home electronic appliances, machine tools, personal electronic equipmentand industrial robots"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designedfor life support)"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems and medical equipment for life support, etc.The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC'sdata sheets or data books, etc. If customers wish to use NEC semiconductor products in applications notintended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingnessto support a given application.(Note)(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or forNEC (as defined above).M8E 00. 44User’s Manual U15509EJ2V0<strong>UM</strong>

Regional InformationSome information contained in this document may vary from country to country. Before using any NECproduct in your application, pIease contact the NEC office in your country to obtain a list of authorizedrepresentatives and distributors. They will verify:• Device availability• Ordering information• Product release schedule• Availability of related technical literature• Development environment specifications (for example, specifications for third-party tools andcomponents, host computers, power plugs, AC supply voltages, and so forth)• Network requirementsIn addition, trademarks, registered trademarks, export restrictions, and other legal issues may also varyfrom country to country.NEC Electronics Inc. (U.S.)Santa Clara, CaliforniaTel: 408-588-6000800-366-9782Fax: 408-588-6130800-729-9288NEC do Brasil S.A.Electron Devices DivisionGuarulhos-SP, BrasilTel: 11-<strong>64</strong>62-6810Fax: 11-<strong>64</strong>62-6829NEC Electronics (Europe) GmbHDuesseldorf, GermanyTel: 0211-65 03 01Fax: 0211-65 03 <strong>32</strong>7• Sucursal en EspañaMadrid, SpainTel: 091-504 27 87Fax: 091-504 28 60• Succursale FrançaiseVélizy-Villacoublay, FranceTel: 01-30-67 58 00Fax: 01-30-67 58 99• Filiale ItalianaMilano, ItalyTel: 02-66 75 41Fax: 02-66 75 42 99• Branch The NetherlandsEindhoven, The NetherlandsTel: 040-244 58 45Fax: 040-244 45 80• Branch SwedenTaeby, SwedenTel: 08-63 80 820Fax: 08-63 80 388• United Kingdom BranchMilton Keynes, UKTel: 01908-691-133Fax: 01908-670-290NEC Electronics Hong Kong Ltd.Hong KongTel: 2886-9318Fax: 2886-9022/9044NEC Electronics Hong Kong Ltd.Seoul BranchSeoul, KoreaTel: 02-528-0303Fax: 02-528-4411NEC Electronics Shanghai, Ltd.Shanghai, P.R. ChinaTel: 021-6841-1138Fax: 021-6841-1137NEC Electronics Taiwan Ltd.Taipei, TaiwanTel: 02-2719-2377Fax: 02-2719-5951NEC Electronics Singapore Pte. Ltd.Novena Square, SingaporeTel: 253-8311Fax: 250-3583J02.4User’s Manual U15509EJ2V0<strong>UM</strong> 5

PREFACEReadersThis manual targets users who intend to understand the functions of the <strong>VR4100</strong><strong>Series</strong>, the RISC microprocessors, and to design application systems using them.PurposeThis manual introduces the architecture of the <strong>VR4100</strong> <strong>Series</strong> to users, following theorganization described below.OrganizationTwo manuals are available for the <strong>VR4100</strong> <strong>Series</strong>: <strong>Architecture</strong> User’s Manual (thismanual) and Hardware User’s Manual of each product.<strong>Architecture</strong>User's Manual• Pipeline operation• Cache organization and memorymanagement system• Exception processing• Interrupts• Instruction setHardwareUser's Manual• Pin functions• Physical address space• Function of Coprocessor 0• Initialization interface• Peripheral unitsHow to read this manualIt is assumed that the reader of this manual has general knowledge in the fields ofelectric engineering, logic circuits, and microcomputers.In this manual, the following products are referred to as the <strong>VR4100</strong> <strong>Series</strong>.Descriptions that differ between these products are explained individually, andcommon parts are explained as for the <strong>VR4100</strong> <strong>Series</strong>.VR4121 (µPD30121)VR4122 (µPD30122)VR4131 (µPD30131)VR4181 (µPD30181)VR4181A (µPD30181A, 30181AY)To learn in detail about the function of a specific instruction,→ Read CHAPTER 2 CPU INSTRUCTION SET S<strong>UM</strong>MARY, CHAPTER 3MIPS16 INSTRUCTION SET, CHAPTER 9 CPU INSTRUCTION SETDETAILS, and CHAPTER 10 MIPS16 INSTRUCTION SET FORMAT.To learn about the overall functions of the <strong>VR4100</strong> <strong>Series</strong>,→ Read this manual in sequential order.To learn about hardware functions,→ Refer to Hardware User's Manual which is separately available.To learn about electrical specifications,→ Refer to Data Sheet which is separately available.6User’s Manual U15509EJ2V0<strong>UM</strong>

Conventions Data significance: Higher on left and lower on rightActive low:XXX# (trailing # after pin and signal names)Note:Description of item marked with Note in the textCaution:Information requiring particular attentionRemark:Supplementary informationNumeric representation: binary/decimal ... XXXXhexadecimal ... 0xXXXXPrefixes representing an exponent of 2 (for address space or memory capacity):K (kilo) ... 2 10 = 1024M (mega) ...2 20 = 1024 2G (giga) ... 2 30 = 1024 3T (tera) ... 2 40 = 1024 4P (peta) ... 2 50 = 1024 5E (exa) ... 2 60 = 1024 6Related DocumentsThe related documents indicated here may include preliminary version. However,preliminary versions are not marked as such.Document name<strong>VR4100</strong> <strong>Series</strong> <strong>Architecture</strong> User’s ManualVR4121 User’s ManualµPD30121 (VR4121) Data SheetVR4122 User’s ManualµPD30122 (VR4122) Data SheetVR4131 Hardware User’s ManualµPD30131 (VR4131) Data SheetVR4181 Hardware User’s ManualµPD30181 (VR4181) Data SheetVR4181A Hardware User’s ManualµPD30181A, 30181AY (VR4181A) Data SheetDocument numberThis manualU13569EU14691EU14<strong>32</strong>7EU16219EU15350ETo be preparedU14272EU14273ETo be preparedTo be preparedVR <strong>Series</strong> TM Programming Guide Application Note U10710EUser’s Manual U15509EJ2V0<strong>UM</strong> 7

CONTENTSCHAPTER 1 INTRODUCTION .............................................................................................................. 171.1 Features .................................................................................................................................... 171.2 CPU Core .................................................................................................................................. 191.2.1 CPU registers .............................................................................................................................. 201.2.2 Coprocessors .............................................................................................................................. 211.2.3 System control coprocessor (CP0) .............................................................................................. 211.2.4 Floating-point unit (FPU) ............................................................................................................. 231.2.5 Cache memory ............................................................................................................................ 231.3 CPU Instruction Set Overview ................................................................................................ 231.4 Data Formats and Addressing ................................................................................................ 261.5 Memory Management System ................................................................................................ 301.5.1 Translation lookaside buffer (TLB) .............................................................................................. 301.5.2 Processor modes ......................................................................................................................... 301.6 Instruction Pipeline .................................................................................................................. 311.6.1 Branch prediction ......................................................................................................................... 311.7 Code Compatibility .................................................................................................................. <strong>32</strong>CHAPTER 2 CPU INSTRUCTION SET S<strong>UM</strong>MARY ......................................................................... 3<strong>32</strong>.1 Instruction Set <strong>Architecture</strong> .................................................................................................... 3<strong>32</strong>.2 CPU Instruction Formats ......................................................................................................... 342.3 Instructions Added in the <strong>VR4100</strong> <strong>Series</strong> ............................................................................... 352.3.1 Product-sum operation instructions ............................................................................................. 352.3.2 Power mode instructions ............................................................................................................. 352.4 Instruction Overview ............................................................................................................... 362.4.1 Load and store instructions ......................................................................................................... 362.4.2 Computational instructions .......................................................................................................... 402.4.3 Jump and branch instructions ...................................................................................................... 472.4.4 Special instructions ...................................................................................................................... 512.4.5 System control coprocessor (CP0) instructions ........................................................................... 52CHAPTER 3 MIPS16 INSTRUCTION SET ......................................................................................... 543.1 Outline ....................................................................................................................................... 543.2 Features .................................................................................................................................... 543.3 Register Set .............................................................................................................................. 553.4 ISA Mode ................................................................................................................................... 563.4.1 Changing ISA mode <strong>bit</strong> by software ............................................................................................ 563.4.2 Changing ISA mode <strong>bit</strong> by exception ........................................................................................... 563.4.3 Enabling change ISA mode <strong>bit</strong> .................................................................................................... 573.5 Types of Instructions ............................................................................................................... 573.6 Instruction Format ................................................................................................................... 593.7 MIPS16 Operation Code Bit Encoding ................................................................................... <strong>64</strong>3.8 Outline of Instructions ............................................................................................................. 678User’s Manual U15509EJ2V0<strong>UM</strong>

3.8.1 PC-relative instructions ............................................................................................................... 673.8.2 Extend instruction ........................................................................................................................ 683.8.3 Delay slots ................................................................................................................................... 703.8.4 Instruction details ........................................................................................................................ 71CHAPTER 4 PIPELINE ......................................................................................................................... 844.1 Pipeline Stages ........................................................................................................................ 844.1.1 VR4121, VR4122, VR4181A ......................................................................................................... 844.1.2 VR4131 ........................................................................................................................................ 874.1.3 VR4181 ........................................................................................................................................ 894.2 Branch Delay ............................................................................................................................ 904.2.1 VR4121, VR4122, VR4181A ......................................................................................................... 904.2.2 VR4131 ........................................................................................................................................ 914.2.3 VR4181 ........................................................................................................................................ 934.3 Branch Prediction .................................................................................................................... 944.3.1 VR4122, VR4181A ....................................................................................................................... 954.3.2 VR4131 ........................................................................................................................................ 974.4 Load Delay ................................................................................................................................ 1014.5 Instruction Streaming .............................................................................................................. 1014.6 Pipeline Activities .................................................................................................................... 1024.7 Interlock and Exception .......................................................................................................... 11<strong>64</strong>.7.1 Exception conditions ................................................................................................................... 1194.7.2 Stall conditions ............................................................................................................................ 1204.7.3 Slip conditions ............................................................................................................................. 1214.7.4 Bypassing .................................................................................................................................... 123CHAPTER 5 MEMORY MANAGEMENT SYSTEM ............................................................................ 1245.1 Processor Modes ..................................................................................................................... 1245.1.1 Operating mode ........................................................................................................................... 1245.1.2 Addressing mode ........................................................................................................................ 1245.2 Translation Lookaside Buffer (TLB) ...................................................................................... 1255.2.1 Format of a TLB entry ................................................................................................................. 1255.2.2 Manipulation of TLB .................................................................................................................... 1265.2.3 TLB instructions ........................................................................................................................... 1275.2.4 TLB exceptions ............................................................................................................................ 1275.3 Virtual-to-Physical Address Translation ............................................................................... 1285.3.1 <strong>32</strong>-<strong>bit</strong> mode address translation .................................................................................................. 1315.3.2 <strong>64</strong>-<strong>bit</strong> mode address translation .................................................................................................. 1<strong>32</strong>5.4 Address Space ........................................................................................................................ 1335.4.1 User mode virtual address space ................................................................................................ 1335.4.2 Supervisor mode virtual address space ...................................................................................... 1355.4.3 Kernel mode virtual address space ............................................................................................. 1385.5 Memory Management Registers ............................................................................................ 1465.5.1 Index register (0) ......................................................................................................................... 1475.5.2 Random register (1) .................................................................................................................... 1475.5.3 EntryLo0 (2) and EntryLo1 (3) registers ...................................................................................... 148User’s Manual U15509EJ2V0<strong>UM</strong> 9

CHAPTER 7 CACHE MEMORY .......................................................................................................... 1987.1 Memory Organization .............................................................................................................. 1987.1.1 On-chip caches ........................................................................................................................... 1997.2 Cache Organization ................................................................................................................. 2007.2.1 Instruction cache line .................................................................................................................. 2007.2.2 Data cache line ............................................................................................................................ 2017.2.3 Placement of cache data ............................................................................................................. 2027.3 Cache Operations .................................................................................................................... 2027.3.1 Cache data coherency ................................................................................................................ 2037.3.2 Replacement of cache line .......................................................................................................... 2037.3.3 Accessing the caches ................................................................................................................. 2047.4 Cache States ............................................................................................................................ 2057.4.1 Cache state transition diagrams .................................................................................................. 2067.5 Cache Access Flow ................................................................................................................. 2077.6 Manipulation of the Caches by an External Agent ............................................................... 2207.7 Initialization of the Caches ..................................................................................................... 220CHAPTER 8 CPU CORE INTERRUPTS ............................................................................................ 2218.1 Types of Interrupt Request ..................................................................................................... 2218.1.1 Non-maskable interrupt (NMI) ..................................................................................................... 2218.1.2 Ordinary interrupts ....................................................................................................................... 2218.1.3 Software interrupts generated in CPU core ................................................................................. 2228.1.4 Timer interrupt ............................................................................................................................. 2228.2 Acknowledging Interrupts ...................................................................................................... 2228.2.1 Detecting hardware interrupts ..................................................................................................... 2228.2.2 Masking interrupt signals ............................................................................................................. 223CHAPTER 9 CPU INSTRUCTION SET DETAILS ............................................................................ 2249.1 Instruction Notation Conventions .......................................................................................... 2249.2 Notes on Using CPU Instructions .......................................................................................... 2269.2.1 Load and Store instructions ......................................................................................................... 2269.2.2 Jump and Branch instructions ..................................................................................................... 2279.2.3 System control coprocessor (CP0) instructions .......................................................................... 2289.3 CPU Instructions ...................................................................................................................... 2289.4 CPU Instruction Opcode Bit Encoding .................................................................................. 383CHAPTER 10 MIPS16 INSTRUCTION SET FORMAT ..................................................................... 386CHAPTER 11 COPROCESSOR 0 HAZARDS ................................................................................... 421APPENDIX INDEX ................................................................................................................................. 427User’s Manual U15509EJ2V0<strong>UM</strong> 11

LIST OF FIGURES (1/3)Fig. No. Title Page1-1. CPU Core Internal Block Diagram ........................................................................................................ 191-2. CPU Registers ...................................................................................................................................... 211-3. CPU Instruction Formats (<strong>32</strong>-<strong>bit</strong> Length Instruction) ............................................................................. 231-4. CPU Instruction Formats (16-<strong>bit</strong> Length Instruction) ............................................................................. 251-5. Byte Address in Big-Endian Byte Order ................................................................................................ 271-6. Byte Address in Little-Endian Byte Order .............................................................................................. 281-7. Misaligned Word Accessing (Little-Endian) .......................................................................................... 292-1. CPU Instruction Formats ....................................................................................................................... 342-2. Byte Specification Related to Load and Store Instructions ................................................................... 374-1. Pipeline Stages (VR4121, VR4122, VR4181A) ....................................................................................... 854-2. Instruction Execution in the Pipeline (VR4121, VR4122, VR4181A) ....................................................... 8<strong>64</strong>-3. Pipeline Stages (VR4131) ...................................................................................................................... 874-4. Instruction Execution in the Pipeline (VR4131) ...................................................................................... 884-5. Pipeline Stages (VR4181) ...................................................................................................................... 894-6. Instruction Execution in the Pipeline (VR4181) ...................................................................................... 894-7. Branch Delay (VR4121, VR4122, VR4181A) ........................................................................................... 904-8. Branch Delay (VR4131, MIPS III Instruction Mode) ............................................................................... 914-9. Branch Delay (VR4131, MIPS16 Instruction Mode) ............................................................................... 924-10. Branch Delay (VR4181) ......................................................................................................................... 934-11. Pipeline on Branch Prediction (VR4122, VR4181A) ............................................................................... 954-12. Pipeline on Branch Prediction (VR4131, When the Branch Is in the Lower Address) ........................... 974-13. Pipeline on Branch Prediction (VR4131, When the Branch Is in the Higher Address) .......................... 994-14. Pipeline Activities .................................................................................................................................. 1024-15. ADD Instruction Pipeline Activities (VR4121, VR4122, VR4181A) .......................................................... 1044-16. ADD Instruction Pipeline Activities (VR4131) ........................................................................................ 1054-17. ADD Instruction Pipeline Activities (VR4181) ........................................................................................ 1054-18. JALR Instruction Pipeline Activities (VR4121, VR4122, VR4181A) ......................................................... 10<strong>64</strong>-19. JALR Instruction Pipeline Activities (VR4131) ....................................................................................... 1074-20. JALR Instruction Pipeline Activities (VR4181) ....................................................................................... 1074-21. BEQ Instruction Pipeline Activities (VR4121, VR4122, VR4181A) .......................................................... 1084-22. BEQ Instruction Pipeline Activities (VR4131) ........................................................................................ 1094-23. BEQ Instruction Pipeline Activities (VR4181) ........................................................................................ 1094-24. TLT Instruction Pipeline Activities (VR4121, VR4122, VR4181A) ........................................................... 1104-25. TLT Instruction Pipeline Activities (VR4131) .......................................................................................... 1114-26. TLT Instruction Pipeline Activities (VR4181) .......................................................................................... 1114-27. LW Instruction Pipeline Activities (VR4121, VR4122, VR4181A) ............................................................ 1124-28. LW Instruction Pipeline Activities (VR4131) .......................................................................................... 1134-29. LW Instruction Pipeline Activities (VR4181) .......................................................................................... 1134-30. SW Instruction Pipeline Activities (VR4121, VR4122, VR4181A) ........................................................... 1144-31. SW Instruction Pipeline Activities (VR4131) .......................................................................................... 1154-<strong>32</strong>. SW Instruction Pipeline Activities (VR4181) .......................................................................................... 1154-33. Interlocks, Exceptions, and Faults ........................................................................................................ 11612User’s Manual U15509EJ2V0<strong>UM</strong>

LIST OF FIGURES (2/3)Fig. No. Title Page4-34. Exception Detection ............................................................................................................................... 1194-35. Data Cache Miss Stall ............................................................................................................................ 1204-36. CACHE Instruction Stall ......................................................................................................................... 1204-37. Load Data Interlock ................................................................................................................................ 1214-38. MD Busy Interlock .................................................................................................................................. 1225-1. Format of a TLB Entry ............................................................................................................................ 1265-2. TLB Manipulation Overview ................................................................................................................... 1275-3. Virtual-to-Physical Address Translation ................................................................................................. 1295-4. Address Translation in TLB .................................................................................................................... 1305-5. <strong>32</strong>-<strong>bit</strong> Mode Virtual Address Translation ................................................................................................ 1315-6. <strong>64</strong>-<strong>bit</strong> Mode Virtual Address Translation ................................................................................................ 1<strong>32</strong>5-7. User Mode Address Space .................................................................................................................... 1345-8. Supervisor Mode Address Space .......................................................................................................... 1365-9. Kernel Mode Address Space ................................................................................................................. 1395-10. xkphys Area Address Space .................................................................................................................. 1405-11. Index Register ........................................................................................................................................ 1475-12. Random Register ................................................................................................................................... 1475-13. EntryLo0 and EntryLo1 Registers .......................................................................................................... 1485-14. PageMask Register ................................................................................................................................ 1495-15. Positions Indicated by the Wired Register ............................................................................................. 1505-16. Wired Register ....................................................................................................................................... 1505-17. EntryHi Register ..................................................................................................................................... 1515-18. PRId Register ......................................................................................................................................... 1525-19. Config Register ...................................................................................................................................... 1535-20. LLAddr Register ..................................................................................................................................... 1555-21. TagLo Register ...................................................................................................................................... 1565-22. TagHi Register ....................................................................................................................................... 1566-1. Context Register ..................................................................................................................................... 1596-2. BadVAddr Register ................................................................................................................................. 1606-3. Count Register........................................................................................................................................ 1606-4. Compare Register................................................................................................................................... 1616-5. Status Register ....................................................................................................................................... 1616-6. Status Register Diagnostic Status Field ................................................................................................ 1636-7. Cause Register ....................................................................................................................................... 1656-8. EPC Register (When MIPS16 ISA Is Disabled) ..................................................................................... 1676-9. EPC Register (When MIPS16 ISA Is Enabled) ...................................................................................... 1686-10. WatchLo Register ................................................................................................................................... 1686-11. WatchHi Register.................................................................................................................................... 1686-12. XContext Register................................................................................................................................... 1696-13. Parity Error Register ............................................................................................................................... 1706-14. Cache Error Register .............................................................................................................................. 1706-15. ErrorEPC Register (When MIPS16 ISA Is Disabled) ............................................................................. 172User’s Manual U15509EJ2V0<strong>UM</strong> 13

LIST OF FIGURES (3/3)Fig. No. Title Page6-16. ErrorEPC Register (When MIPS16 ISA Is Enabled) ............................................................................. 1726-17. Common Exception Handling ................................................................................................................ 1926-18. TLB/XTLB Refill Exception Handling ..................................................................................................... 1946-19. Cold Reset Exception Handling ............................................................................................................ 1966-20. Soft Reset and NMI Exception Handling ............................................................................................... 1977-1. Logical Hierarchy of Memory ................................................................................................................ 1987-2. On-chip Caches and Main Memory ....................................................................................................... 1997-3. Instruction Cache Line Format .............................................................................................................. 2007-4. Data Cache Line Format ....................................................................................................................... 2017-5. Cache Index and Data Output ............................................................................................................... 2047-6. Instruction Cache State Diagram .......................................................................................................... 2067-7. Data Cache State Diagram ................................................................................................................... 2067-8. Flow on Instruction Fetch ...................................................................................................................... 2077-9. Flow on Load Operations ...................................................................................................................... 2087-10. Flow on Store Operations ..................................................................................................................... 2097-11. Flow on Index_Invalidate Operations .................................................................................................... 2107-12. Flow on Index_Writeback_Invalidate Operations .................................................................................. 2117-13. Flow on Index_Load_Tag Operations ................................................................................................... 2117-14. Flow on Index_Store_Tag Operations ................................................................................................... 2127-15. Flow on Create_Dirty Operations .......................................................................................................... 2127-16. Flow on Hit_Invalidate Operations ........................................................................................................ 2137-17. Flow on Hit_Writeback_Invalidate Operations ...................................................................................... 2147-18. Flow on Fill Operations ......................................................................................................................... 2157-19. Flow on Hit_Writeback Operations ....................................................................................................... 2167-20. Flow on Fetch_and_Lock Operations (VR4131 only) ............................................................................ 2177-21. Writeback Flow ..................................................................................................................................... 2187-22. Refill Flow .............................................................................................................................................. 2187-23. Writeback & Refill Flow ......................................................................................................................... 2198-1. Non-maskable Interrupt Signal .............................................................................................................. 2218-2. Hardware Interrupt Signals ................................................................................................................... 2228-3. Masking of the Interrupt Request Signals ............................................................................................. 2239-1. CPU Instruction Opcode Bit Encoding .................................................................................................. 38314User’s Manual U15509EJ2V0<strong>UM</strong>

LIST OF TABLES (1/2)Table No. Title Page1-1. Comparison of Functions of <strong>VR4100</strong> <strong>Series</strong> ........................................................................................... 181-2. CP0 Registers ........................................................................................................................................ 221-3. List of Instructions Supported by VR <strong>Series</strong> Processors ........................................................................ <strong>32</strong>2-1. MACC Instructions (for VR4121, VR4122, VR4131, and VR4181A) ......................................................... 352-2. Product-Sum Operation Instructions (for VR4181) ................................................................................. 352-3. Power Mode Instructions ....................................................................................................................... 352-4. Number of Delay Slot Cycles Necessary for Load and Store Instructions ............................................. 362-5. Load/Store Instruction ............................................................................................................................ 382-6. Load/Store Instruction (Extended ISA) .................................................................................................. 392-7. ALU Immediate Instruction .................................................................................................................... 402-8. ALU Immediate Instruction (Extended ISA) ........................................................................................... 412-9. Three-Operand Type Instruction ............................................................................................................ 412-10. Three-Operand Type Instruction (Extended ISA) ................................................................................... 422-11. Shift Instruction ...................................................................................................................................... 422-12. Shift Instruction (Extended ISA) ............................................................................................................. 4<strong>32</strong>-13. Multiply/Divide Instructions .................................................................................................................... 442-14. Multiply/Divide Instructions (Extended ISA) ........................................................................................... 442-15. Product-Sum Operation Instructions (for VR4121, VR4122, VR4131, and VR4181A) ............................. 452-16. Product-Sum Operation Instructions (for VR4181) ................................................................................. 452-17. Number of Stall Cycles in Multiply and Divide Instructions .................................................................... 462-18. Jump Instructions ................................................................................................................................... 472-19. Branch Instructions ................................................................................................................................ 482-20. Branch Instructions (Extended ISA) ....................................................................................................... 492-21. Special Instructions ................................................................................................................................ 512-22. Special Instructions (Extended ISA) ...................................................................................................... 512-23. System Control Coprocessor (CP0) Instructions ................................................................................... 523-1. General-purpose Registers .................................................................................................................... 553-2. Special Registers ................................................................................................................................... 563-3. MIPS16 Instruction Set Outline .............................................................................................................. 573-4. Field Definition ....................................................................................................................................... 593-5. Bit Encoding of Major Operation Code (op) ........................................................................................... <strong>64</strong>3-6. RR Minor Operation Code (RR-Type Instruction) .................................................................................. <strong>64</strong>3-7. RRR Minor Operation Code (RRR-Type Instruction) ............................................................................. 653-8. RRI-A Minor Operation Code (RRI-Type ADD Instruction) .................................................................... 653-9. SHIFT Minor Operation Code (SHIFT-Type Instruction) ........................................................................ 653-10. I8 Minor Operation Code (I8-Type Instruction) ....................................................................................... 653-11. I<strong>64</strong> Minor Operation Code (<strong>64</strong>-<strong>bit</strong> Only, I<strong>64</strong>-Type Instruction) ............................................................... 663-12. Base PC Address Setting ...................................................................................................................... 673-13. Extendable MIPS16 Instructions ............................................................................................................ 693-14. Load and Store Instructions ................................................................................................................... 713-15. ALU Immediate Instructions ................................................................................................................... 743-16. Two-/Three-Operand Register Type ...................................................................................................... 763-17. Shift Instructions .................................................................................................................................... 78User’s Manual U15509EJ2V0<strong>UM</strong> 15

LIST OF TABLES (2/2)Table No. Title Page3-18. Multiply/Divide Instructions .................................................................................................................... 803-19. Jump and Branch Instructions .............................................................................................................. 823-20. Special Instructions ............................................................................................................................... 834-1. Description of Pipeline Activities during Each Stage ............................................................................. 1034-2. Correspondence of Pipeline Stage to Interlock and Exception Conditions ........................................... 1174-3. Pipeline Interlock ................................................................................................................................... 1184-4. Description of Pipeline Exception .......................................................................................................... 1185-1. User Mode Segments ........................................................................................................................... 1345-2. <strong>32</strong>-<strong>bit</strong> and <strong>64</strong>-<strong>bit</strong> Supervisor Mode Segments ....................................................................................... 1375-3. <strong>32</strong>-<strong>bit</strong> Kernel Mode Segments ............................................................................................................... 1415-4. <strong>64</strong>-<strong>bit</strong> Kernel Mode Segments ............................................................................................................... 1435-5. Cacheability and the xkphys Address Space ........................................................................................ 1445-6. CP0 Registers ....................................................................................................................................... 1465-7. Cache Algorithm .................................................................................................................................... 1495-8. Mask Values and Page Sizes ............................................................................................................... 1495-9. System Interface Clock Ratio (to PClock) ............................................................................................. 1545-10. Instruction Cache Sizes ........................................................................................................................ 1555-11. Data Cache Sizes ................................................................................................................................. 1556-1. CP0 Registers ....................................................................................................................................... 1586-2. Cause Register Exception Code Field .................................................................................................. 1666-3. <strong>32</strong>-Bit Mode Exception Vector Base Addresses .................................................................................... 1746-4. <strong>64</strong>-Bit Mode Exception Vector Base Addresses .................................................................................... 1746-5. Exception Priority Order ........................................................................................................................ 1757-1. Cache Size, Line Size, and Index ......................................................................................................... 2049-1. CPU Instruction Operation Notations .................................................................................................... 2259-2. Load and Store Common Functions ..................................................................................................... 2269-3. Access Type Specifications for Loads/Stores ....................................................................................... 22711-1. Coprocessor 0 Hazards ........................................................................................................................ 42211-2. Calculation Example of CP0 Hazard and Number of Instructions Inserted ........................................... 42616User’s Manual U15509EJ2V0<strong>UM</strong>

CHAPTER 1 INTRODUCTIONThis chapter gives an outline of the VR4121 (µPD30121), the VR4122 (µPD30122), the VR4131 (µPD30131), theVR4181 (µPD30181), and the VR4181A (µPD30181A, 30181AY), which are <strong>64</strong>-/<strong>32</strong>-<strong>bit</strong> RISC microprocessors. In thismanual, these products are referred to as the <strong>VR4100</strong> <strong>Series</strong>.1.1 FeaturesThe <strong>VR4100</strong> <strong>Series</strong>, which is a part of the RISC microprocessor VR <strong>Series</strong>, is a group of products developed for PDAs.The VR <strong>Series</strong> is high-performance <strong>64</strong>-/<strong>32</strong>-<strong>bit</strong> microprocessors employing the RISC (reduced instruction set computer)architecture developed by MIPS TM manufactured by NEC.The <strong>VR4100</strong> <strong>Series</strong> accommodates the ultra low power consumption CPU core provided with cache memory, ahigh-speed product-sum operation unit, and an address management unit. The <strong>VR4100</strong> <strong>Series</strong> also has interfaceunits for the peripheral circuits required for battery-driven portable information equipment (refer to Hardware User'sManual of each product for details about on-chip peripheral functions).The features of the <strong>VR4100</strong> <strong>Series</strong> are described below.◦ Employs <strong>64</strong>-<strong>bit</strong> RISC core as a CPUPossible to operate in <strong>32</strong>-<strong>bit</strong> mode◦ Optimized instruction pipeline◦ On-chip cache memory◦ Employs write-back cacheReduces store operations using system bus◦ Physical address space: <strong>32</strong> <strong>bit</strong>sVirtual address space: 40 <strong>bit</strong>s◦ Translation lookaside buffer (TLB) with <strong>32</strong>-double entries◦ Instruction set: MIPS III (however, the FPU, LL, LLD, SC, and SCD instructions are removed), MIPS16◦ Supports high-speed product-sum operation instructions◦ Effective power management features, which include the four modes of Fullspeed, Standby, Suspend, andHibernate◦ On-chip PLL and clock generator◦ Variable on-chip peripheral functions ideal for potable information equipmentThe functions of the <strong>VR4100</strong> <strong>Series</strong> are listed as follows.User’s Manual U15509EJ2V0<strong>UM</strong> 17

CHAPTER 1 INTRODUCTIONTable 1-1. Comparison of Functions of <strong>VR4100</strong> <strong>Series</strong>Item VR4121 VR4122 VR4131 VR4181 VR4181APart number µPD30121 µPD30122 µPD30131 µPD30181 µPD30181A,30181AYCPU core VR4120 TM core VR4130 TM core VR4110 TM core VR4120 coreInstruction setMIPS I, II, IIIMIPS I, II, IIIMIPS I, II, III+ high-speed product-sum (<strong>32</strong>-<strong>bit</strong>)+ high-speed product-+ high-speed product-+ MIPS16sum (16-<strong>bit</strong>)sum (<strong>32</strong>-<strong>bit</strong>)+ MIPS16+ MIPS16Pipeline 5-/6-stage pipeline 2-way superscalar6-/7-stage pipeline5-stage pipeline5-/6-stage pipelineOn-chip cache• Instruction: 16KB• Instruction: <strong>32</strong>KB• Instruction: 16KB• Instruction: 4KB• Instruction: 8KBmemory• Data: 8KB• Data: 16KB• Data: 16KB• Data: 4KB• Data: 8KB• Direct map• Direct map• 2-way set-• Direct map• Direct mapassociative• With line lockfunctionOn-chip peripheral• Memory controller• Memory controller• Memory controller• Memory controllerfunctions• Extension bus• Extension bus interface (ISA, PCI)• Extension bus• Extension businterface (ISA)• Communication interface (UART, CSI, IrDAinterface (ISA)interface (ISA)• LCD interface(SIR, MIR, FIR))• LCD interface• LCD interface• Touch panel• LED controller• Touch panel• Touch panelinterface• Timer, counterinterfaceinterface• Keyboard interface• General-purpose port• Keyboard interface• Keyboard interface• Communicationinterface (UART,CSI, IrDA (SIR,• Clock generator• Power management unit• Communicationinterface (UART,CSI, IrDA (SIR))• Communicationinterface (UART,CSI, I 2 C, IrDA (SIR))MIR, FIR))• CompactFlash• CompactFlash• Modem interfaceinterfaceinterface• Audio interface• Audio interface• AC97/I 2 S audio• LED controller• LED controllerinterface• DMA controller• DMA controller• DMA controller• Timer, counter• Watchdog timer• General-purposeport• Timer, counter• Watchdog timer• General-purposeport• USB host/functioncontroller• PWM generator• Timer, counter• Clock generator• Clock generator• Watchdog timer• Power managementunit• Power managementunit• General-purposeport• A/D converter• A/D converter• Clock generator• D/A converter• D/A converter• Power managementunit• A/D converter• D/A converterOther functions − • On-chip branch prediction function• On-chip hardware debug function−• On-chip branchprediction function• On-chip hardwaredebug function18User’s Manual U15509EJ2V0<strong>UM</strong>

CHAPTER 1 INTRODUCTION1.2 CPU CoreFigure 1-1 shows the internal block diagram of the CPU core.In addition to the conventional high-performance integer operation units, this CPU core has a full-associativeformat translation lookaside buffer (TLB), which has <strong>32</strong> entries that provide mapping to 2-page pairs for one entry.Moreover, it also has instruction and data caches, and a bus interface.Figure 1-1. CPU Core Internal Block DiagramVirtual address busInternal data busControl (o)Control (i)BusinterfaceData cacheInstructioncacheCP0CPUAddress/data (o)Address/data (i)TLBClockgeneratorInternal clock(1) CPUCPU is a block that performs integer calculations. This block includes a <strong>64</strong>-<strong>bit</strong> integer data path, and productsumoperator.(2) Coprocessor 0 (CP0)CP0 incorporates a memory management unit (MMU) and exception handling function. The MMU checkswhether there is an access between different memory segments (user, supervisor, and kernel) by executingaddress conversion. The translation lookaside buffer (TLB) converts virtual addresses to physical addresses.(3) Instruction cacheThe instruction cache employs virtual index and physical tag formats. It is managed with direct mapping formatin the VR4121, VR4122, VR4181, and VR4181A, or with 2-way set-associative format in the VR4131.(4) Data cacheThe data cache employs virtual index, physical tag, and writeback formats. It is managed with direct mappingformat in the VR4121, VR4122, VR4181, and VR4181A, or with 2-way set-associative format in the VR4131.User’s Manual U15509EJ2V0<strong>UM</strong> 19

CHAPTER 1 INTRODUCTION(5) CPU bus interfaceThe bus interface controls data transmission/reception between the CPU core and peripheral units. The businterface consists of two <strong>32</strong>-<strong>bit</strong> multiplexed address/data buses (one for input, and the other for output), clocksignals, interrupt request signals, and various other control signals.(6) Clock generatorThe clock generator processes clock inputs and supplies them to internal units.1.2.1 CPU registersThe CPU core has thirty-two <strong>64</strong>-<strong>bit</strong> general-purpose registers (GPR).In addition, it provides the following special registers:• PC: Program counter (<strong>64</strong> <strong>bit</strong>s)• HI register: Contains the integer multiply and divide higher doubleword result (<strong>64</strong> <strong>bit</strong>s)• LO register: Contains the integer multiply and divide lower doubleword result (<strong>64</strong> <strong>bit</strong>s)Two of the general-purpose registers are assigned the following functions:• r0 is fixed to 0, and can be used as the target register for any instruction whose result is to be discarded. r0can also be used as a source register when a zero value is needed.• r31 is the link register used by link instructions such as JAL (jump and link) instructions. This register can beused for other instructions. However, be careful that use of the register by a link instruction will not coincidewith use of the register for other operations.The register group is provided within the CP0 (system control coprocessor), to process exceptions and to manageaddresses.CPU registers can operate as either <strong>32</strong>-<strong>bit</strong> or <strong>64</strong>-<strong>bit</strong> registers, depending on the processor operation mode.The operation of the CPU register differs depending on what instructions are executed: <strong>32</strong>-<strong>bit</strong> instructions orMIPS16 instructions. For details, refer to CHAPTER 3 MIPS16 INSTRUCTION SET.The <strong>VR4100</strong> <strong>Series</strong> processors have no program status word (PSW) register as such; this is covered by theStatus and Cause registers incorporated within the system control coprocessor (CP0). For details of CP0 registers,refer to Table 1-2 CP0 Registers.Figure 1-2 shows the CPU registers.20User’s Manual U15509EJ2V0<strong>UM</strong>

CHAPTER 1 INTRODUCTIONFigure 1-2. CPU RegistersGeneral-purpose registers63r0 = 0r1r206363Multiply and divide registersHILO00r29r30r31 = Link address63Program counterPC01.2.2 CoprocessorsMIPS ISA defines 4 types of coprocessors (CP0 to CP3).• CP0 translates virtual addresses to physical addresses, switches the operating mode (Kernel, Supervisor, orUser mode), and manages exceptions. It also controls the cache subsystem to analyze a cause and to returnfrom the error state.• CP1 is reserved for floating-point instructions.• CP2 is reserved for future definition by MIPS.• CP3 is no longer defined. CP3 instructions are reserved for future extensions.The <strong>VR4100</strong> <strong>Series</strong> implements the CP0 only.1.2.3 System control coprocessor (CP0)CP0 translates virtual addresses to physical addresses, switches the operating mode, controls the cachememory, and manages exceptions. For detailed descriptions of these functions, refer to CHAPTER 5 MEMORYMANAGEMENT SYSTEM and CHAPTER 6 EXCEPTION PROCESSING.CP0 has thirty-two registers that have corresponding register number. The register number is used as anoperand of instructions to specify a CP0 register to be accessed. Table 1-2 shows simple descriptions of eachregister.User’s Manual U15509EJ2V0<strong>UM</strong> 21

CHAPTER 1 INTRODUCTIONTable 1-2. CP0 RegistersRegisterRegister Name Usage DescriptionNumber0 Index Memory management Programmable pointer to TLB array1 Random Memory management Pseudo-random pointer to TLB array (read only)2 EntryLo0 Memory management Lower half of TLB entry for even VPN3 EntryLo1 Memory management Lower half of TLB entry for odd VPN4 Context Exception processing Pointer to virtual PTE table in <strong>32</strong>-<strong>bit</strong> mode5 PageMask Memory management Page size specification6 Wired Memory management Number of wired TLB entries7 − − Reserved for future use8 BadVAddr Exception processing Virtual address where the most recent error occurred9 Count Exception processing Timer count10 EntryHi Memory management Upper half of TLB entry (including ASID)11 Compare Exception processing Timer compare value12 Status Exception processing Operation status13 Cause Exception processing Cause of last exception14 EPC Exception processing Exception program counter15 PRId Memory management Processor revision identifier16 Config Memory management Memory mode system specification17 LLAddr Note1 Memory management Physical address for diagnostic purpose18 WatchLo Exception processing Memory reference trap address lower <strong>bit</strong>s19 WatchHi Exception processing Memory reference trap address higher <strong>bit</strong>s20 Xcontext Exception processing Pointer to virtual PTE table in <strong>64</strong>-<strong>bit</strong> mode21 to 25 − − Reserved for future use26 Parity Error Note2 Exception processing Cache parity <strong>bit</strong>s27 Cache Error Note2 Exception processing Index and status of cache error28 TagLo Memory management Cache tag register (low)29 TagHi Memory management Cache tag register (high)30 ErrorEPC Exception processing Error exception program counter31 − − Reserved for future useNotes 1. This register is defined to maintain compatibility with the VR4000 TM and VR4400 TM . The contents of thisregister are meaningless in the normal operation.2. This register is defined to maintain compatibility with the <strong>VR4100</strong> TM . This register is not used in the normaloperation.Caution When accessing the CP0 registers, some instructions require consideration of the interval timeuntil the next instruction is executed, because there is a delay from when the contents of the CP0register change to when this change is reflected in the CPU operation. This time lag is called a CP0hazard. For details, refer to CHAPTER 11 COPROCESSOR 0 HAZARDS.22User’s Manual U15509EJ2V0<strong>UM</strong>

CHAPTER 1 INTRODUCTION1.2.4 Floating-point unit (FPU)The <strong>VR4100</strong> <strong>Series</strong> does not support the floating-point unit (FPU). A coprocessor unusable exception will occur ifany FPU instructions are executed. If necessary, FPU instructions should be emulated by software in an exceptionhandler.1.2.5 Cache memoryThe <strong>VR4100</strong> <strong>Series</strong> incorporates instruction and data caches, which are independent of each other. Thisconfiguration enables high-performance pipeline operations. Both caches have a <strong>64</strong>-<strong>bit</strong> data bus, enabling a oneclockaccess. These buses can be accessed in parallel.The caches are managed with direct mapping format in the VR4121, VR4122, VR4181, and VR4181A, or with 2-way set-associative format in the VR4131. The data cache of the VR4131 has also the line lock function.A detailed description of caches is given in CHAPETER 7 CACHE MEMORY.1.3 CPU Instruction Set OverviewThere are two types of CPU instructions: <strong>32</strong>-<strong>bit</strong> length instructions (MIPS III) and 16-<strong>bit</strong> length instructions(MIPS16). Use of the MIPS16 instructions is enabled or disabled by setting MIPS16EN pin during a reset.(1) MIPS III instructionsAll the CPU instructions are <strong>32</strong>-<strong>bit</strong> length when executing MIPS III instructions, and they are classified into threeinstruction formats as shown in Figure 1-3: immediate (I type), jump (J type), and register (R type). The fields ofeach instruction format are described in CHAPTER 2 CPU INSTRUCTION SET S<strong>UM</strong>MARY.Figure 1-3. CPU Instruction Formats (<strong>32</strong>-<strong>bit</strong> Length Instruction)I - type (Immediate)31 26 25 21 20 16 15 0op rs rt immediateJ - type (Jump)31 26 25 0optargetR - type (Register)31 26 25 21 20 16 15 11 10 6 5 0op rs rt rd sa functUser’s Manual U15509EJ2V0<strong>UM</strong> 23

CHAPTER 1 INTRODUCTIONThe instruction set can be further divided into the following five groupings:(a) Load and store instructions move data between the memory and the general-purpose registers. They are allimmediate (I-type) instructions, since the only addressing mode supported is base register plus 16-<strong>bit</strong>,signed immediate offset.(b) Computational instructions perform arithmetic, logical, shift, and multiply and divide operations on values inregisters. They include R-type (in which both the operands and the result are stored in registers) and I-type(in which one operand is a 16-<strong>bit</strong> signed immediate value) formats.(c) Jump and branch instructions change the control flow of a program. Jumps are made either to an absoluteaddress formed by combining a 26-<strong>bit</strong> target address with the higher <strong>bit</strong>s of the program counter (J-typeformat) or register-specified address (R-type format). The format of the branch instructions is I type.Branches have 16-<strong>bit</strong> offsets relative to the program counter. JAL instructions save their return address inregister 31.(d) System control coprocessor (CP0) instructions perform operations on CP0 registers to control the memorymanagementand exception-handling facilities of the processor.(e) Special instructions perform system calls and breakpoint exceptions, or cause a branch to the generalexception-handling vector based upon the result of a comparison. These instructions occur in both R-typeand I-type formats.For the operation of each instruction, refer to CHAPTER 2 CPU INSTRUCTION SET S<strong>UM</strong>MARY and CHAPTER9 CPU INSTRUCTION SET DETAILS.(2) Additional instructionsAll the sum-of-products instructions and power mode instructions are <strong>32</strong>-<strong>bit</strong> length.(3) MIPS16 instructionsAll the CPU instructions except for JAL and JALX are 16-<strong>bit</strong> length when executing MIPS16 instructions, and theyare classified into thirteen instruction formats as shown in Figure 1-4.The fields of each instruction format are described in CHAPTER 3 MIPS 16 INSTRUCTION SET.24User’s Manual U15509EJ2V0<strong>UM</strong>

CHAPTER 1 INTRODUCTIONFigure 1-4. CPU Instruction Formats (16-<strong>bit</strong> Length Instruction)1511 100I-typeopimmediate1511 10 8 70RI-typeoprximmediate1511 10 8 75 40RR-typeoprxryfunct1511 10 8 75 40RRI-typeRRIrxryimmediate1511 10 8 75 42 10RRR-typeRRRrxryrzF1511 10 8 75 430RRI-A-typeRRI-ArxryFimmediate1511 10 8 75 42 10Shift-typeSHIFTrxryShamtF1511 10 8 70I8-typeI8functimmediate1511 10 8 75 40I8_MOVR<strong>32</strong>-typeI8functryr<strong>32</strong>(4:0)15 11 10 8 7 5 4 3 20I8_MOV<strong>32</strong>R-typeI8functr<strong>32</strong>(2:0)r<strong>32</strong>(4:3)rz1511 10 8 70I<strong>64</strong>-typeI<strong>64</strong>functimmediate1511 10 8 75 40RI<strong>64</strong>-typeI<strong>64</strong>functryimmediateJAL/JALX-type3116 1511 10 9 5 40Immediate(15:0)JALXImmediate(20:16)Immediate(25:21)User’s Manual U15509EJ2V0<strong>UM</strong> 25

CHAPTER 1 INTRODUCTIONThe instruction set can be further divided into the following four groupings:(a) Load and store instructions move data between memory and general-purpose registers. They include RRI,RI, I8, and RI<strong>64</strong> types.(b) Computational instructions perform arithmetic, logical, shift, and multiply and divide operations on values inregisters. They include RI-, RRIA, I8, RI<strong>64</strong>, I<strong>64</strong>, RR, RRR, I8_MOVR<strong>32</strong>, and I8_MOV<strong>32</strong>R types.(c) Jump and branch instructions change the control flow of a program. They include JAL/JALX, RR, RI, I8, and Itypes.(d) Special instructions are SYSCALL, BREAK, and Extend instructions. The SYSCALL and BREAK instructionstransfer control to an exception handler. The Extend instruction extends the immediate field of the nextinstruction. They are RR and I types. When extending the immediate field of the next instruction by using theExtend instruction, one cycle is needed for executing the Extend instruction, and another cycle is needed forexecuting the next instruction.For more details of each instruction’s operation, refer to CHAPTER 3 MIPS16 INSTRUCTION SET andCHAPTER 10 MIPS16 INSTRUCTION SET FORMAT.1.4 Data Formats and AddressingThe <strong>VR4100</strong> <strong>Series</strong> uses the following four data formats:• Doubleword (<strong>64</strong> <strong>bit</strong>s)• Word (<strong>32</strong> <strong>bit</strong>s)• Halfword (16 <strong>bit</strong>s)• Byte (8 <strong>bit</strong>s)In the CPU core, if the data format is any one of halfword, word, or doubleword, the byte ordering can be set aseither big endian or little endian. In the VR4131, the setting of BIGENDIAN pin during a reset decides which byteorder is used. The VR4121, VR4122, VR4181, and VR4181A only support the little-endian order.Endianness refers to the location of byte 0 within the multi-byte data structure. Figures 1-5 and 1-6 show theconfiguration.When configured as a big-endian system, byte 0 is always the most-significant (leftmost) byte, which iscompatible with MC68000 TM and IBM370 TM conventions.When configured as a little-endian system, byte 0 is always the least-significant (rightmost) byte, which iscompatible with Pentium TM and DEC VAX TM conventions.In this manual, <strong>bit</strong> designations are always little endian.26User’s Manual U15509EJ2V0<strong>UM</strong>

CHAPTER 1 INTRODUCTIONFigure 1-5. Byte Address in Big-Endian Byte Order(a) Word dataHigh-orderaddress31 24 23 16 15 8 7 012131415Wordaddress12891011845674Low-orderaddress01230(b) Doubleword dataHigh-orderaddressWord Halfword Byte63 <strong>32</strong> 31 16 15 8 7 016 17 18 19 20 21 22 23Doublewordaddress16891011121314158Low-orderaddress012345670Remarks 1. The highest byte is the lowest address.2. The address of word data is specified by the highest byte’s address.User’s Manual U15509EJ2V0<strong>UM</strong> 27