Synthesis and simulate 4 bit Ripple carry adder

Synthesis and simulate 4 bit Ripple carry adder

Synthesis and simulate 4 bit Ripple carry adder

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

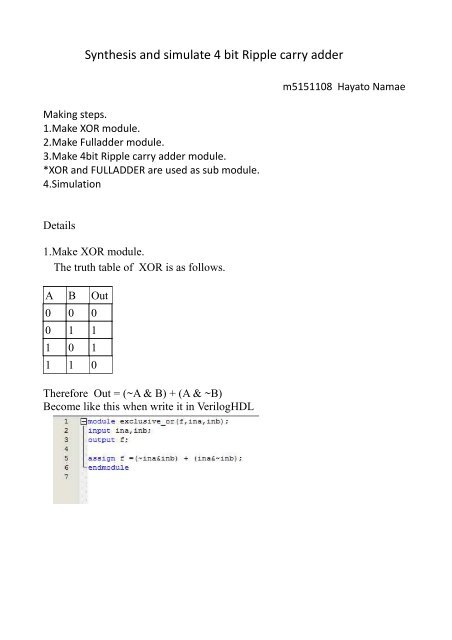

<strong>Synthesis</strong> <strong>and</strong> <strong>simulate</strong> 4 <strong>bit</strong> <strong>Ripple</strong> <strong>carry</strong> <strong>adder</strong>Making steps.1.Make XOR module.2.Make Full<strong>adder</strong> module.3.Make 4<strong>bit</strong> <strong>Ripple</strong> <strong>carry</strong> <strong>adder</strong> module.*XOR <strong>and</strong> FULLADDER are used as sub module.4.Simulationm5151108 Hayato NamaeDetails1.Make XOR module.The truth table of XOR is as follows.A B Out0 0 00 1 11 0 11 1 0Therefore Out = (~A & B) + (A & ~B)Become like this when write it in VerilogHDL

2.Make Full<strong>adder</strong>.The truth table of Full<strong>adder</strong> is as follows.A B Ci S Co0 0 0 0 00 0 1 0 10 1 0 0 10 1 1 1 01 0 0 0 11 0 1 1 01 1 0 1 01 1 1 1 1Therefore S = (A^B)^CiCo = (A&B) || (Ci & (A^B))I used XOR which I made with step 1 as a submodule.Become like this when write it in VerilogHDL3.Make 4<strong>bit</strong> <strong>Ripple</strong> <strong>carry</strong> <strong>adder</strong>4<strong>bit</strong> <strong>Ripple</strong> <strong>carry</strong> <strong>adder</strong> is constructed by 4 Full<strong>adder</strong>.Carry-out-signal of Full<strong>adder</strong> of each <strong>bit</strong> is connected to Carry-in of the next<strong>bit</strong>.Become like this when write it in VerilogHDL

4.SimulationIn this simulation, I tried eight following combinations.A[3:0] B[3:0] S[3:0] Co4'b0000 4'b0000 4'b0000 04'b1111 4'b0000 4'b1111 04'b1010 4'b0101 4'b1111 04'b1111 4'b0001 4'b0000 14'b1111 4'b1111 4'b1110 14'b0111 4'b0001 4'b1000 04'b1001 4'b0001 4'b1010 04'b0100 4'b0100 4'b1000 0Result of simulation

Test benchAs a result of simulation, it was shown that a circuit worked definitely becausethe output same as expectation was provided.