Vector quantization processor for mobile video communication ...

Vector quantization processor for mobile video communication ...

Vector quantization processor for mobile video communication ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

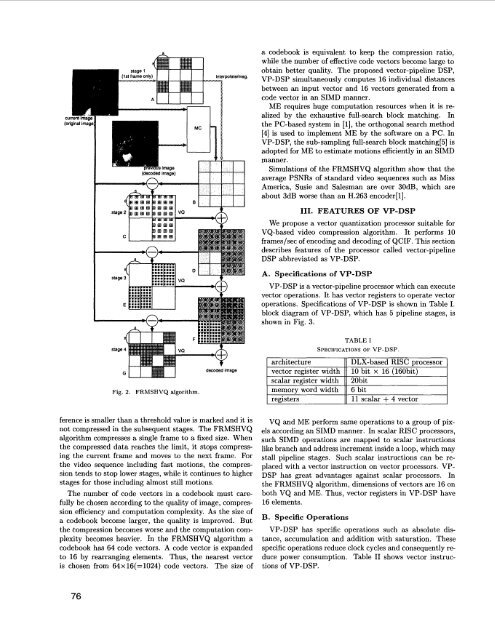

interpolatelmags imageI(decoded image)cI Istagea codebook is equivalent to keep the compression ratio,while the number of effective code vectors become large toobtain better quality. The proposed vector-pipeline DSP,VP-DSP simultaneously computes 16 individual distancesbetween an input vector and 16 vectors generated from acode vector in an SIMD manner.ME requires huge computation resources when it is realizedby the exhaustive full-search block matching. Inthe PC-based system in [I], the orthogonal search method[4] is used to implement ME by the software on a PC. InVP-DSP, the sub-sampling full-search block matching[5] isadopted <strong>for</strong> ME to estimate motions efficiently in an SIMDmanner.Simulations of the FRMSHVQ algorithm show that theaverage PSNRs of standard <strong>video</strong> sequences such as MissAmerica, Susie and Salesman are over 30dB, which areabout 3dB worse than an H.263 encoder[l].111. FEATURES OF VP-DSPWe propose a vector <strong>quantization</strong> <strong>processor</strong> suitable <strong>for</strong>VQ-based <strong>video</strong> compression algorithm. It per<strong>for</strong>ms 10frames/sec of encoding and decoding of QCIF. This sectiondescribes features of the <strong>processor</strong> called vector-pipelineDSP abbreviated as VP-DSP.A. Specifications of VP-DSPVP-DSP is a vector-pipeline <strong>processor</strong> which can executevector operations. It has vector registers to operate vectoroperations. Specifications of VP-DSP is shown in Table I.block diagram of VP-DSP, which has 5 pipeline stages, isshown in Fig. 3.Fig. 2. FRMSHVQ algorithm.ference is smaller than a threshold value is marked and it isnot compressed in the subsequent stages. The FRMSHVQalgorithm compresses a single frame to a fixed size. Whenthe compressed data reaches the limit, it stops compressingthe current frame and moves to the next frame. Forthe <strong>video</strong> sequence including fast motions, the compressiontends to stop lower stages, while it continues to higherstages <strong>for</strong> those including almost still motions.The number of code vectors in a codebook must carefullybe chosen according to the quality of image, compressionefficiency and computation complexity. As the size ofa codebook become larger, the quality is improved. Butthe Compression becomes worse and the computation complexitybecomes heavier. In the FRMSHVQ algorithm acodebook has 64 code vectors. A code vector is expandedto 16 by rearranging elements. Thus, the nearest vectoris chosen from 64x16(=1024) code vectors. The size ofvector register width 11scalar register widthmemory word widthregistersTABLE ISPECIFICATIONS OF VP-DSParchitecture 1) DLX-based RISC <strong>processor</strong>10 bit x 16 (160bit)20bit6 bit11 scalar + 4 vectorVQ and ME per<strong>for</strong>m same operations to a group of pixelsaccording an SIMD manner. In scalar RISC <strong>processor</strong>s,such SIMD operations are mapped to scalar instructionslike branch and address increment inside a loop, which maystall pipeline stages. Such scalar instructions can be replacedwith a vector instruction on vector <strong>processor</strong>s. VP-DSP has great advantages against scalar <strong>processor</strong>s. Inthe FRMSHVQ algorithm, dimensions of vectors are 16 onboth VQ and ME. Thus, vector registers in VP-DSP have16 elements.B. Specific OperationsVP-DSP has specific operations such as absolute distance,accumulation and addition with saturation. Thesespecific operations reduce clock cycles and consequently reducepower consumption. Table I1 shows vector instructionsof VP-DSP.76