10. Sequential Logic Synthesis What are Combinational Circuits?

10. Sequential Logic Synthesis What are Combinational Circuits?

10. Sequential Logic Synthesis What are Combinational Circuits?

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

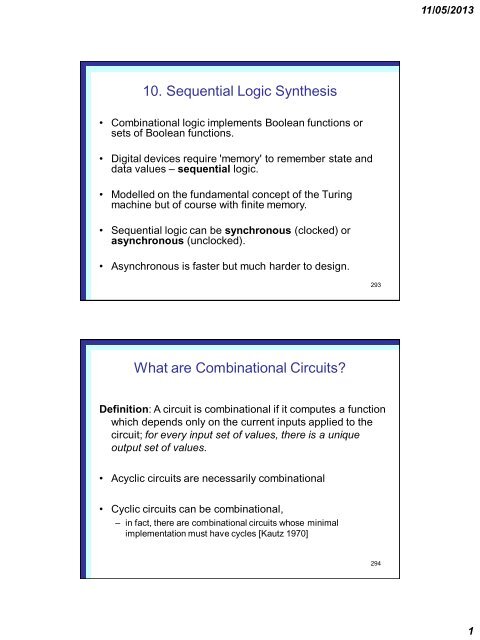

11/05/2013<strong>10.</strong> <strong>Sequential</strong> <strong>Logic</strong> <strong>Synthesis</strong>• <strong>Combinational</strong> logic implements Boolean functions orsets of Boolean functions.• Digital devices require 'memory' to remember state anddata values – sequential logic.• Modelled on the fundamental concept of the Turingmachine but of course with finite memory.• <strong>Sequential</strong> logic can be synchronous (clocked) orasynchronous (unclocked).• Asynchronous is faster but much harder to design.293<strong>What</strong> <strong>are</strong> <strong>Combinational</strong> <strong>Circuits</strong>?Definition: A circuit is combinational if it computes a functionwhich depends only on the current inputs applied to thecircuit; for every input set of values, there is a uniqueoutput set of values.• Acyclic circuits <strong>are</strong> necessarily combinational• Cyclic circuits can be combinational,– in fact, there <strong>are</strong> combinational circuits whose minimalimplementation must have cycles [Kautz 1970]2941

11/05/2013<strong>What</strong> <strong>are</strong> <strong>Sequential</strong> <strong>Circuits</strong>?Some sequential circuits have memory elements.– Synchronous circuits have clocked latches.– Asynchronous circuits may or may not have latches but these <strong>are</strong> notclocked.Feedback (cyclic) is a necessary, but not sufficient condition for a circuitto be sequential.<strong>Synthesis</strong> of sequential circuits is not as well developed ascombinational. (only small circuits)<strong>Sequential</strong> synthesis techniques <strong>are</strong> not really used in commercialsoftw<strong>are</strong> (except maybe retiming).<strong>Sequential</strong> circuit verification is a difficult problem.295Finite State MachinesFinite State Machines in STG or transition relation form <strong>are</strong>a behavioral view of sequential circuits.– They describe their transitional behavior.– They can distinguish among a finite number of classes of inputsequence histories:– These classes <strong>are</strong> the internal states of the machine.Moore Machine: is a quintuple: M(S, I, O, , )– S: finite non-empty set of states– I: finite non-empty set of inputs– O: finite non-empty set of outputs– : S x I S transition (or next state) function– : S O output function (note: output only a function ofpresent state)2962

11/05/2013Moore FSMinput<strong>Combinational</strong>Next State <strong>Logic</strong>State<strong>Combinational</strong>output logicoutput297FSM’s (continued)Mealy Machine: M(S, I, O, , ) but– : S x I O (i.e. output depends on both present state andpresent input)– for digital circuits, typically I = {0,1} m and O = {0,1} nIn addition, (for both Moore and Mealy machines) certainstates <strong>are</strong> classified as reset or initial statesFinite automata <strong>are</strong> similar to FSM’s, but– they do not produce any outputs,– they just accept input sequences (an accepting set of states isgiven).2983

11/05/2013Mealy FSMinput<strong>Combinational</strong>Next State <strong>Logic</strong>State<strong>Combinational</strong>output logicoutput299TRAFFIC LIGHT Control ExampleSource: notes.ump.edu.my/fkee/BEE2243/AMRAN/Notes/TRAFFIC%20LIGHT%20FSM.ppt3004

11/05/2013TRAFFIC LIFHT301TRAFFIC LIGHT3025

11/05/2013TRAFFIC LIGHT303STATE DIAGRAM3046

11/05/2013STATE ENCODING305CODED STATE DIAGRAM3067

11/05/2013FSM REALIZATION307STATE EQUATION3088

11/05/2013FSM IMPLEMENTATION309Incompletely Specified Machines• Next state and output functions have don’t c<strong>are</strong>s.• However, for an implementation, and <strong>are</strong> functions,– thus they <strong>are</strong> uniquely defined for each input and statecombination.• Don’t c<strong>are</strong>s arise when some combinations <strong>are</strong> of no interest:– they will not occur or– their outputs will not be observed• For these, the next state or output may not be specified.– (In this case, and <strong>are</strong> relations, but of special type. Weshould make sure we want these as don’t c<strong>are</strong>s.)• Such machines <strong>are</strong> called incompletely specified.3109