The Midterm Solution - Suraj @ LUMS - Lahore University of ...

The Midterm Solution - Suraj @ LUMS - Lahore University of ...

The Midterm Solution - Suraj @ LUMS - Lahore University of ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

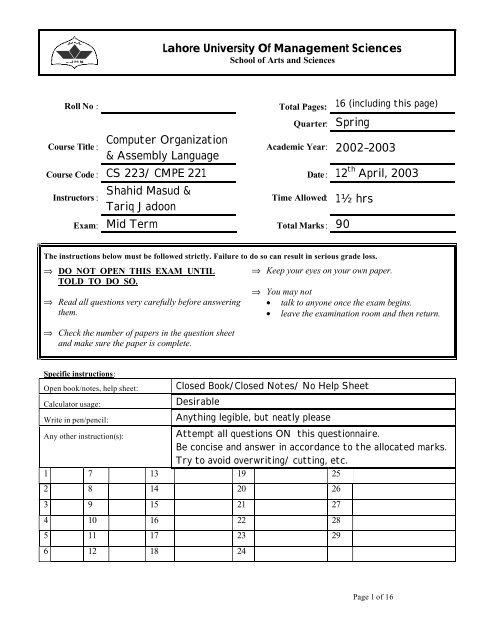

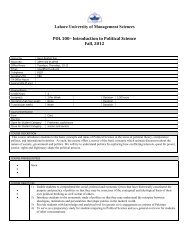

<strong>Lahore</strong> <strong>University</strong> Of Management SciencesSchool <strong>of</strong> Arts and SciencesRoll No :Course Title :Computer Organization& Assembly LanguageTotal Pages: 16 (including this page)Quarter: SpringAcademic Year: 2002–2003Course Code : CS 223/ CMPE 221 Date: 12 th April, 2003Instructors :Shahid Masud &Tariq JadoonTime Allowed: 1½ hrsExam: Mid Term Total Marks: 90<strong>The</strong> instructions below must be followed strictly. Failure to do so can result in serious grade loss.⇒ DO NOT OPEN THIS EXAM UNTILTOLD TO DO SO.⇒ Read all questions very carefully before answeringthem.⇒ Check the number <strong>of</strong> papers in the question sheetand make sure the paper is complete.⇒ Keep your eyes on your own paper.⇒ You may not• talk to anyone once the exam begins.• leave the examination room and then return.Specific instructions:Open book/notes, help sheet:Calculator usage:Write in pen/pencil:Closed Book/Closed Notes/ No Help SheetDesirableAnything legible, but neatly pleaseAny other instruction(s): Attempt all questions ON this questionnaire.Be concise and answer in accordance to the allocated marks.Try to avoid overwriting/ cutting, etc.1 7 13 19 252 8 14 20 263 9 15 21 274 10 16 22 285 11 17 23 296 12 18 24Page 1 <strong>of</strong> 16

<strong>The</strong> solution shows the marking scheme for section III only)Part A [20 marks]Please encircle the correct answers. Each question carries 1 mark1. Which <strong>of</strong> the following is a memory that can only hold its charge for a short time andmust be refreshed periodically?a. DRAMb. SRAMc. SDRAMd. EPROMe. EEROM2. Which <strong>of</strong> the following non-volatile memory is electrically erasable and programmableat the block level (multiple bytes at a time)?a. EPROMb. SRAMc. SDRAMd. Flashe. EEPROM3. Which <strong>of</strong> the following ranks highest (smallest, most expensive, fastest access, mostfrequently accessed) in the memory hierarchy?a. hard driveb. cachec. CD-ROMd. RAMe. registers4. Which <strong>of</strong> the following ranks second in the memory hierarchy?a. hard driveb. cachec. CD-ROMd. RAMe. registers5. Which <strong>of</strong> the following ranks third in the memory hierarchy?a. hard driveb. cachec. CD-ROMd. RAMe. registers6. Which <strong>of</strong> the following ranks the lowest (largest, least expensive, slowest access, leastfrequently accessed) in the memory hierarchy?a. hard driveb. L1-cachec. L2-cached. RAMe. registersPage 2 <strong>of</strong> 16

S. Masud & T. Jadoon Computer Organization & Assembly Language (Mid Term Exam) 12 th April 20037. <strong>The</strong> concentric set <strong>of</strong> rings on a disk platter are called:a. gapsb. headsc. sectorsd. trackse. worms8. <strong>The</strong> conducting coils that read and write data on a disk platter are called:a. gapsb. headsc. sectorsd. trackse. worms9. <strong>The</strong> block-size regions that typically hold about 512 bytes <strong>of</strong> data on a disk platter called:a. gapsb. headsc. sectorsd. trackse. worms10. <strong>The</strong> areas <strong>of</strong> separation on a disk platter that break up the areas <strong>of</strong> physical data storageare called:a. gapsb. headsc. sectorsd. trackse. worms11. Which member <strong>of</strong> the memory hierarchy is regarded as the lowest-cost, slowest speedmedia?a. magnetic diskb. CD-ROMc. DVDd. magnetic tapee. Zip Drive12. This technology, popular for storing digitized video information, has a capacity <strong>of</strong> over 5gigabytes:a. magnetic diskb. CD-ROMc. DVDd. magnetic tapee. Zip Drive13. <strong>The</strong> time that it takes the read/write head <strong>of</strong> a disk drive to position under the desiredsector once it is positioned on the right track is called the:a. access timePage 3 <strong>of</strong> 16Page 3 <strong>of</strong> 17

<strong>The</strong> initial state <strong>of</strong> the memory (in hexadecimal notation) is detailed on page 6.Suppose the program counter is initialized so that the instruction at location 100h isexecuted first.Step through the program, updating the appropriate registers and memory locations,until the Halt instruction is reached.Answer the questions using the table provided on the next page detailing the initial contents <strong>of</strong>memory. You may also use the reverse side for rough work if necessary.a) What is the value <strong>of</strong> memory location 11Ah?_________0003 h_________b) What is the value <strong>of</strong> memory location 11Ch?_________0008 h or 0005 h______c) What is the value <strong>of</strong> memory location 11Eh?_________0003 h_______________d) What is the value <strong>of</strong> memory location 120h?_________000A h_______________e) What is the value <strong>of</strong> memory location 122h?_________0002 h_________________________f) What is the value <strong>of</strong> memory location 124h?_________0004 h_________________________PTOPage 6 <strong>of</strong> 16

Initial Contents <strong>of</strong> Memory in hex:Rough WorkLocation Contents100 011C102 3122104 1120106 011A108 211E10A 111A10C 411210E 1120110 1124112 011C114 211A116 111C118 700011A 0000Step No:1. AC= 00052. AC= 000A3. location 120: 000A4. AC= 00005. AC= 00036. location 11A: 00037. PC = 1128. AC= 00059. AC= 000810. location 11C = 0008OR Alternatively7. PC = 11C8. Can not continue, as we don’tknow the contents <strong>of</strong> location00511C 000511E 0003120 0000122 0002124 0004Page 7 <strong>of</strong> 16

Q22. [10 marks] An 8-bit microprocessor has a total addressable space <strong>of</strong> 64 kBytes.Organize the memory space so that the first 16 kBytes is ROM. <strong>The</strong> next 8 kBytes isempty for future expansion. This is followed by 16 kBytes RAM. <strong>The</strong> remaining spaceis once again empty for future expansion.(a) Label the starting and ending addresses <strong>of</strong> each region in hexadecimal. [4]16 k Bytes (ROM)8 k Bytes (free)16 k Bytes (RAM)0000 h3FF F h4000 h5FFF h6000 h9FFF hA000 hfreeFFFF hRough WorkIf the available ROM chips are (16k x 8) and RAM chips are (16k x 8). Draw ablock diagram <strong>of</strong> a suitable memory design implementing the memory mapdescribed in part (a) on the reverse side <strong>of</strong> this sheet. Label the address,data, and control lines on the microprocessor and memory chips. You mayuse additional logic chips if required. [6]Page 8 <strong>of</strong> 16

OR GateA15A14OR GateA133X8 DecoderA0-A12ReadCSRead/ WriteCS16 K x 8 16 K x 8ROMRAMD0-D7MicroprocessorPage 9 <strong>of</strong> 16

Q 23. [15 marks] A microprocessor has an on-chip 2-way set associative cache with a totalcapacity <strong>of</strong> 8 kByte. Each line in cache can store sixteen 8-bit words. It has a totaladdressable space <strong>of</strong> 16 MBytes.Consider the following CPU instruction:Load AB1234ha) Which set number will this request be stored in cache? [2]Number <strong>of</strong> lines in a set (k) = 2Total capacity <strong>of</strong> the cache = 8 k ByteBlock size = 2 w = line size = sixteen 8 bit words = 16 bytesNumber <strong>of</strong> sets (v) = 2 d = Total capacity /( k x line size) = 256Total addressable space = = 2 s+w = 16 M bytesAddress length = (s + w) bits = 24 bitsThus, in the main memory address:Size <strong>of</strong> set = d = 8 bitsSize <strong>of</strong> a word = w = 4 bitsSize <strong>of</strong> a tag = (s-d) bits = 12 bits<strong>The</strong>refore, Load AB1234h will store the result in set number:23 hb) What will be its corresponding tag number? [2]<strong>The</strong> corresponding tag number will be : AB1 hIf the microprocessor had a direct mapped cache with half the capacity <strong>of</strong> the setassociative cache. <strong>The</strong>n,c) Which line number would the request be saved in? [2]If a microprocessor had a direct mapped cache with half the capacity <strong>of</strong> the set <strong>of</strong>the two –way set associative cache, then it would have a capacity <strong>of</strong> 4 kbytes andeffectively the same number <strong>of</strong> lines as the number <strong>of</strong> sets in the set associativecache, i.e.Number <strong>of</strong> lines in cache = m = 2 r = 256Thus, in the main memory address:Size <strong>of</strong> a line = r = 8 bitsSize <strong>of</strong> a word = w = 4 bitsSize <strong>of</strong> a tag = (s- r) bits = 12 bits<strong>The</strong>refore, Load AB1234h will store the result inline number:23 hPage 10 <strong>of</strong> 16

d) What will be the corresponding tag number [2]<strong>The</strong> corresponding tag number will once again be : AB1 hNow consider the case if the microprocessor had an associative cache with four times thecapacity <strong>of</strong> the direct mapped cache.e) Which line number would the request be saved in? [1]In associative mapping any block can be stored in any line depending upon the currentoccupancy and replacement algorithms. Thus, we cannot say for sure which linenumber the request will be saved in.f) What will be the corresponding tag number? [2]Address length = (s + w) bits = 24 bitsThus, in the main memory address:Size <strong>of</strong> a word = w = 4 bitsSize <strong>of</strong> a tag = s bits = 20 bits<strong>The</strong>refore, Load AB1234h will store the result with a tag number: AB123 hg) Which <strong>of</strong> the above caches will have the fastest access time.Justify your answer. [2]<strong>The</strong> direct cache will have the fastest access time, given a hit, i.e. the presence <strong>of</strong> therequested block in cache as only one comparison <strong>of</strong> the tag will determine whether therequisite block is present or absent. Whereas, in associative memory one would haveto compare the required tag with all tags in cache and in a set associative cache onewould have to compare the required tag with all tags in the set.h) Which <strong>of</strong> the above caches has the best overall performance consideringreplacement. [2]Of the three schemes under consideration, the set-associative cache will have the bestoverall performance considering replacement. Access time from main memory istypical much larger than the access time from cache. Thus, if a situation where morethan one block was alternatively required that mapped to the same line number.Direct mapping would require us to overwrite the blocks alternatively and this wouldbe highly inefficient (thrashing). Associative mapping overcomes this but one has togo through the entire cache comparing tags to search for a block. Set-associativecache requires a relatively short time to access a block because one only checks for arequired block by comparing tags within a set usually <strong>of</strong> size 2 or 4 whilst avoidingthrashingPage 11 <strong>of</strong> 16

24. [15 marks]a) Convert the binary number 1001011.101 to decimal [2]1001011.101 = 1×2−3+ 1×2+ 1×2+ 1×2+ 1×2= 0.125 + 0.5 + 1 + 2 + 8 + 64= 75.625b) Convert the hexadecimal number AC to decimal: [1]−1013+ 1×26AC = 12 × 16= 1720+ 10 × 161What are the smallest and largest numbers that you can represent in a 10-bit register using:c) Unsigned notation [2]smallest number = 0largest number = 210−1= 1024 −1=1023d) Two’s complement notation (using the left-most bit as the sign-bit) [2]9smallest number = - 29largest number = + 2= −512−1= + 511e) Consider the following data definitions in a program: [2].datalist WORD 13, 11o, 42h, 00101011bFill out the corresponding values in HEX in the following table. <strong>The</strong> <strong>of</strong>fsets arefrom the data segment.OffsetValue0000 00 h0001 0D hPage 12 <strong>of</strong> 16

0002 00 h0003 09 h0004 00 h0005 42 h0006 00 h0007 2B hUsing the Little Endian formatf) Under what conditions are the following flags set:i) overflow flag [1]Two positive operands were added and their sum is negativeTwo negative operands were added and their sum is positiveii) carry flag [1]If the result <strong>of</strong> an unsigned addition is too large (or too small) for the destinationoperand the carry flag is set.g) Would the following instruction set the zero flag? Explain. [1]MOV AX, 0000h;clear the AX registerThis MOV instruction does not affect the zero flag. Flags are affected by ALUoperationsh) Is it possible for a NEG instruction to set the Overflow flag? [1]<strong>The</strong> NEG instruction can set the overflow flag if we try to negate the smallest signedinteger in a register. <strong>The</strong> NEG instruction results in a positive integer, whichcannot fit into the same register. For example moving –128 to AL and trying tonegate it results in +128, which cannot fit in AL and consequently causes theoverflow, flag to be set.Page 13 <strong>of</strong> 16

i) Consider the following code:mov ax, 0hmov cx, 0AhdoLoop:dec axloop doLoopWhat is the value <strong>of</strong> the ax register after the completion <strong>of</strong> the doLoop? [2]<strong>The</strong> value <strong>of</strong> the ax register after completion <strong>of</strong> the loop is:FFF6 hRough WorkPage 14 <strong>of</strong> 16

Part C [15 marks]26. Which technique frees up the CPU by transferring data directly between the I/O deviceand memory: [1]a. Programmed I/Ob. Interruptsc. I/O Channeld. I/O Registerse. I/O Processorf. DMA27. In which technique, does the CPU issue an I/O command, continues to executesubsequent instructions, and is interrupted by the I/O module when the latter hascompleted its work: [1]a. Programmed I/Ob. Interruptsc. I/O Channeld. I/O Registerse. I/O Processorf. DMA28. When an interrupt occurs, arrange the following operations in their order <strong>of</strong> occurrence?[3]a) interrupt service routine executedb) the registers are restored by popping their values <strong>of</strong>f <strong>of</strong> the stackc) the processor identifies the source <strong>of</strong> the interruptd) the program counter and other registers' values are pushed onto the stacke) the address <strong>of</strong> the interrupt service routine is placed in the program counterOrder <strong>of</strong> Occurrence:1. ____c_____2. ____d____3. ____e____4. ____a____5. ____b____PTOPage 15 <strong>of</strong> 16

29.[10 marks]SP(StackPointer)Consider that an interrupt takes place when themicroprocessor is executing an instruction stored atlocation N. <strong>The</strong> status flags at this instant contain thevalue ABCDh. <strong>The</strong> corresponding interrupt serviceroutine (ISR) is stored in memory starting from location Xand X + C (both inclusive)a) What is the address <strong>of</strong> the instruction that will beexecuted after the interrupt occurs. [2]XXstartb) Where will the program branch to after the completion<strong>of</strong> the interrupt? [2]N + 1c) How will the microprocessor know where to branchafter the completion <strong>of</strong> the interrupt? [3]X+C endPrior to branching to the ISR the microprocessorstores the address <strong>of</strong> the current value <strong>of</strong> theInstruction pointer onto the stack. On completion <strong>of</strong>the subroutine it pops this address <strong>of</strong>f the stack andloads this into the instruction pointer and thusbranches back to the correct location.UserProgramNMAINMEMORYd) What will happen if a second interrupt takes placewhile the first one is being serviced? [3]If a second interrupt took place, then if it were <strong>of</strong>higher priority and the interrupt process was enabledthe microprocessor would once again push the currentcontext onto the stack and branch to the new ISR andon completing it branch back and complete the firstISR by popping <strong>of</strong>f the context from the stack. If theinterrupt process was disabled or if the new interruptwas <strong>of</strong> a lower or the same priority as the currentinterrupt it would remain pending.Page 16 <strong>of</strong> 16