Computer Organization & Assembly Language Exam 2 (2012)

Computer Organization & Assembly Language Exam 2 (2012)

Computer Organization & Assembly Language Exam 2 (2012)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

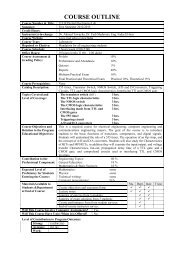

Princess Sumaya University For Technology<strong>Computer</strong> Engineering Dept.22342<strong>Computer</strong> <strong>Organization</strong> & <strong>Assembly</strong> <strong>Language</strong>Second <strong>Exam</strong> (60 Minutes)Dr. Bassam Kahhaleh17 Apr <strong>2012</strong>االس م . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Name:الرقم اجلامعي . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ID: StudentClass No: . . . . . . . . . . .الرقم التسلسلييف الشعبةمن 1( – )43Grade:1. / 72. / 73. a) / 3b) / 3Total / 20

1. A computer was designed with an integer arithmetic unit using 2’s complement system and 4-bitregisters. Two registers can be combined to hold 8-bit values. The unit can perform:(7 Points) 4-bit + 4-bit producing 4-bit result. 4-bit – 4-bit producing 4-bit result. 4-bit × 4-bit producing 8-bit result. 8-bit ÷ 4-bit producing 4-bit quotient and 4-bit remainder.Determine:a) Is it possible to get an overflow error when performing addition?b) Is it possible to get an overflow error when performing subtraction?c) Is it possible to get an overflow error when performing multiplication?d) Is it possible to get an overflow error other than divide by zero when performing division?e) The magnitude of the largest negative operand that can be correctly added to – 1.f) The magnitude of the largest positive operand that can be correctly multiplied by + 1.g) The magnitude of the largest positive operand that can be correctly divided by – 1.

2. A sequential unsigned integer multiplier wasdesigned to multiply 5 bits by 4 bits using an10-bit ALU, two 10-bit and one 4-bitregisters.(7 Points)a) Is there a possibility of overflow?Multiplicand0 0 0 0 0 0 0 0 0 010-bit ALUResult0 0 0 0 0 0 0 0 0 0Multiplier0 0 0 0b) How many times maximum would the ALU perform addition?c) How many times was the Result register shifted?d) If the Multiplier = 12, i.e. (1100) 2 , how many clocks would it take to finish the multiplication?e) To multiply a small number × a bigger number, would you put the bigger number in the Multiplicand,Multiplier or Result register?f) If the initial values of Multiplicand = M, the Multiplier = N, the Result = 1, determine what the finalvalue in the Result register would be after the multiplication operation is finished.g) Can we use 9 bits instead of 10 for the ALU, Multiplicand and Result without the possibility of anoverflow?

Princess Sumaya University for Technology<strong>Computer</strong> Engineering Dept.Dr. B. Kahhaleh 22342 <strong>Computer</strong> <strong>Organization</strong> & <strong>Assembly</strong> <strong>Language</strong> 17 Apr <strong>2012</strong>Second <strong>Exam</strong> (60 Minutes)1. A computer was designed with an integer arithmetic unit using 2’s complement system and 4-bitregisters. Two registers can be combined to hold 8-bit values. The unit can perform:(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer 4-bit + 4-bit producing 4-bit result. 4-bit – 4-bit producing 4-bit result. 4-bit × 4-bit producing 8-bit result. 8-bit ÷ 4-bit producing 4-bit quotient and 4-bit remainder.Determine:a) Is it possible to get an overflow error when performing addition?Yes.b) Is it possible to get an overflow error when performing subtraction?Yes.c) Is it possible to get an overflow error when performing multiplication?No.d) Is it possible to get an overflow error other than divide by zero when performing division?Yes.e) The magnitude of the largest negative operand that can be correctly added to – 1.7.f) The magnitude of the largest positive operand that can be correctly multiplied by + 1.7.g) The magnitude of the largest positive operand that can be correctly divided by – 1.8.2. A sequential unsigned integer multiplier was designed tomultiply 5 bits by 4 bits using an 10-bit ALU, two 10-bit and one4-bit registers.Multiplicand0 0 0 0 0 0 0 0 0 0Multiplier0 0 0 0(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answer(1 Point)Answera) Is there a possibility of overflow?10-bit ALUNo.b) How many times maximum would the ALU perform addition?Result4.0 0 0 0 0 0 0 0 0 0c) How many times was the Result register shifted?0.d) If the Multiplier = 12, i.e. (1100) 2 , how many clocks would it take to finish the multiplication?4.e) To multiply a small number × a bigger number, would you put the bigger number in theMultiplicand, Multiplier or Result register?Multiplicand.f) If the initial values of Multiplicand = M, the Multiplier = N, the Result = 1, determine what thefinal value in the Result register would be after the multiplication operation is finished.Result = M × N + 1.g) Can we use 9 bits for the ALU, Multiplicand and Result without the possibility of an overflow?Yes.3. Using IEEE754 standard:(3 Points)Answer(3 Points)Answera) Write the normalized 32-bit binary representation of the number (6 × 2 – 1 ).0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0.b) What is the decimal value of: 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0.1.25 × 2 1 = 2.5