UNIDAD 4

MIA-Unidad 4 (.pdf)

MIA-Unidad 4 (.pdf)

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

60<br />

3.- El ejemplo 4.1 muestra la forma usual de utilizar el bus PCI en un sistema<br />

uniprocesador.<br />

Ejemplo 4.1: Uso de un bus PCI en un sistema uniprocesador<br />

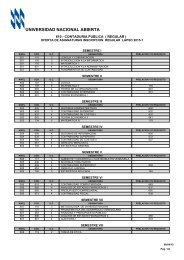

En la figura 4.1 se muestra una configuración usual del bus PCI. En esta<br />

configuración un dispositivo que integra el controlador DRAM y el adaptador<br />

al bus PCI proporciona el acoplamiento al procesador y la posibilidad de<br />

generar datos a velocidades elevadas. El adaptador actúa como un registro<br />

de acople (buffer) de datos, puesto que la velocidad del bus PCI puede<br />

diferir de la capacidad de E/S del procesador.<br />

Procesador<br />

Cache<br />

Monitor<br />

Adaptador/con -<br />

trolador de<br />

memoria<br />

DRAM<br />

Audio<br />

Imágenes<br />

en<br />

movimiento<br />

Bus PCI<br />

Adaptador<br />

del bus de<br />

expansión<br />

Dispositivos<br />

de E/S<br />

básicos<br />

CS<br />

Gráficos<br />

Graficador<br />

Bus de expansión<br />

Figura 4.1 Bus PCI en un sistema uniprocesador<br />

5.- El ejemplo 4.2 presenta el uso de una interfaz de bus ISA que se decodifica<br />

en las direcciones 800H y 803H.<br />

Ejemplo 4.2: Interfaz de bus ISA que contiene un 82C55 accedido por<br />

medio de direcciones de puertos.<br />

2.- La figura 5.2 muestra una interfaz ISA decodificada en las direcciones 800H<br />

a 803H: