Ensemble 3000 Series OpenVPX System - dynamic c4 pte. ltd.

Ensemble 3000 Series OpenVPX System - dynamic c4 pte. ltd.

Ensemble 3000 Series OpenVPX System - dynamic c4 pte. ltd.

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

DATASHEET<br />

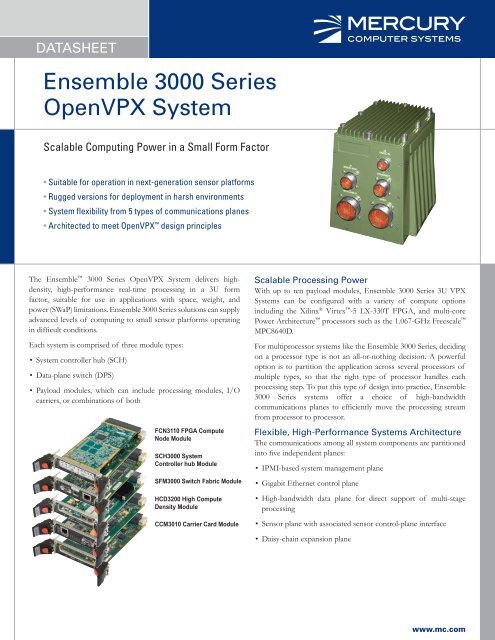

<strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong><br />

<strong>OpenVPX</strong> <strong>System</strong><br />

Scalable Computing Power in a Small Form Factor<br />

Suitable for operation in next-generation sensor platforms<br />

Rugged versions for deployment in harsh environments<br />

<strong>System</strong> fl exibility from 5 types of communications planes<br />

Architected to meet <strong>OpenVPX</strong> design principles<br />

The <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> <strong>OpenVPX</strong> <strong>System</strong> delivers highdensity,<br />

high-performance real-time processing in a 3U form<br />

factor, suitable for use in applications with space, weight, and<br />

power (SWaP) limitations. <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> solutions can supply<br />

advanced levels of computing to small sensor platforms operating<br />

in diffi cult conditions.<br />

Each system is comprised of three module types:<br />

• <strong>System</strong> controller hub (SCH)<br />

• Data-plane switch (DPS)<br />

• Payload modules, which can include processing modules, I/O<br />

carriers, or combinations of both<br />

FCN3110 FPGA Compute<br />

Node Module<br />

SCH<strong>3000</strong> <strong>System</strong><br />

Controller hub Module<br />

SFM<strong>3000</strong> Switch Fabric Module<br />

HCD3200 High Compute<br />

Density Module<br />

CCM3010 Carrier Card Module<br />

Scalable Processing Power<br />

With up to ten payload modules, <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> 3U VPX<br />

<strong>System</strong>s can be confi gured with a variety of compute options<br />

including the Xilinx ® Virtex -5 LX-330T FPGA, and multi-core<br />

Power Architecture processors such as the 1.067-GHz Freescale <br />

MPC8640D.<br />

For multiprocessor systems like the <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong>, deciding<br />

on a processor type is not an all-or-nothing decision. A powerful<br />

option is to partition the application across several processors of<br />

multiple types, so that the right type of processor handles each<br />

processing step. To put this type of design into practice, <strong>Ensemble</strong><br />

<strong>3000</strong> <strong>Series</strong> systems offer a choice of high-bandwidth<br />

communications planes to effi ciently move the processing stream<br />

from processor to processor.<br />

Flexible, High-Performance <strong>System</strong>s Architecture<br />

The communications among all system components are partitioned<br />

into fi ve independent planes:<br />

• IPMI-based system management plane<br />

• Gigabit Ethernet control plane<br />

• High-bandwidth data plane for direct support of multi-stage<br />

processing<br />

• Sensor plane with associated sensor control-plane interface<br />

• Daisy-chain expansion plane<br />

www.mc.com

The <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> SCH<strong>3000</strong> is a critical component,<br />

functioning as both a control-plane Ethernet switch and a<br />

system-management-plane communications hub/controller. The<br />

Gigabit Ethernet module’s control-plane switch enables<br />

application fl exibility. This architectural approach allows<br />

applications to support a range of control functions without<br />

compromising or being affected by data-movement operations.<br />

The system manager function within the SCH<strong>3000</strong> performs the<br />

tasks accomplished in an ATCA ® /MicroTCA ® system by a carrier<br />

management controller and a shelf manager. This comprehensive<br />

system control uses communications over a dedicated<br />

management plane based on the Intelligent Platform<br />

Management Interface (IPMI) standard. Operating independently<br />

of the control and data planes are IPMI communications lines<br />

from the SCH<strong>3000</strong> to the data-plane switch and the payload<br />

modules within a 3U VPX system.<br />

Built in Accordance with <strong>OpenVPX</strong> Design<br />

Principles<br />

The architecture of the <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> 3U VPX<br />

<strong>System</strong> complies with the guidelines established by the <strong>OpenVPX</strong><br />

Working Group. <strong>OpenVPX</strong> is an industry effort to establish<br />

system design principles and practices for implementing the VPX<br />

standard to ensure truly interoperable system components.<br />

Built for Harsh Environments<br />

Designed in compliance with VITA 46 and 48 standards<br />

(VPX-REDI), conduction-cooled versions of the <strong>Ensemble</strong><br />

<strong>3000</strong> <strong>Series</strong> 3U VPX <strong>System</strong>s are fully capable of deployment in<br />

harsh environments, including extreme ranges of temperature and<br />

humidity, high levels of shock and vibration, and poor air quality. Aircooled<br />

options are available for use in less demanding environments.<br />

Physical slot number<br />

Logical slot number<br />

Sensor Plane<br />

(4 lanes)<br />

Sensor Control Plane<br />

(4 lanes)<br />

Expansion Plane<br />

(4 lanes)<br />

Data Plane<br />

(4 lanes)<br />

Control Plane<br />

(1 lane)<br />

Management Plane<br />

(IPMB)<br />

VPX<br />

1<br />

1<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

VPX<br />

2<br />

2<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

Payload Slots Switch/Management<br />

VPX<br />

3<br />

3<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

VPX<br />

4<br />

4<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

VPX<br />

5<br />

11<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

Figure 1. <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> 3U VPX <strong>System</strong> Topologies<br />

VPX<br />

6<br />

5<br />

Control<br />

Switch<br />

VPX<br />

7<br />

6<br />

Data<br />

Switch<br />

External<br />

ChMC IPMC<br />

Advanced Reliability, Maintainability,<br />

and Availability<br />

The IPMI-based management plane communications support<br />

a range of sophisticated functions, including voltage and<br />

temperature monitoring.<br />

The conduction-cooled versions of all modules, including payload<br />

modules, offer the ability to support two-level maintenance (2LM).<br />

Three Styles of Data Movement<br />

<strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> 3U <strong>OpenVPX</strong> <strong>System</strong>s offer three styles<br />

of data-plane operations, all of which can be used concurrently.<br />

Each application can implement the data movement style that<br />

best fi ts its processing model, or use multiple styles at different<br />

stages within complex models.<br />

The most fl exible mode of data-plane communications is via<br />

a high-bandwidth switch fabric. The <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong><br />

SFM<strong>3000</strong> Data-Plane Switch provides a RapidIO ® data-plane<br />

switching function for low-latency, non-blocking, deterministic<br />

switching among eight of the ten payload slots. There is also a<br />

point-to-point RapidIO link between the two remaining payload<br />

slots. The channel to each module consists of 10-Gbps, fullduplex,<br />

serial RapidIO (4 x 3.125 Gbps, with 8/10 encoding).<br />

This style of high-bandwidth, RapidIO-based inter-processor<br />

communication is commonly used to achieve maximum throughput<br />

in applications that need to divide a single math operation, like<br />

an FFT, among multiple processors.<br />

A second style of data movement is via a point-to-point sensor<br />

plane. The ten payload slots within a system are organized fi rst<br />

into two four-slot groupings with direct, full-duplex 10-Gbps<br />

point-to-point links (4 x 3.125 Gbps, with 8/10 encoding) in the<br />

backplane among all members of a group. The two remaining<br />

VPX<br />

8<br />

12<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

VPX<br />

9<br />

7<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

Payload Slots<br />

VPX<br />

10<br />

8<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

VPX<br />

11<br />

9<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

VPX<br />

12<br />

10<br />

Sensor<br />

Plane<br />

Discrete<br />

I/Os<br />

Expan<br />

Plane<br />

Data<br />

Plane<br />

Control<br />

Plane<br />

IPMC<br />

FPGA Clusters<br />

and Sensor Control<br />

<strong>OpenVPX</strong>

payload slots are directly linked with each other in the same<br />

manner. These links can support RapidIO, 10 Gigabit Ethernet,<br />

or the Aurora protocol. This style of data movement delivers<br />

maximum performance for algorithms like beamforming, which<br />

require coherence among processors.<br />

The third style of data movement uses the expansion plane,<br />

linking adjacent slots with direct backplane communications in<br />

a daisy-chain fashion using 16-Gbps PCI Express ® links (8 x 2.5<br />

Gbps, with 8/10 encoding). This style fi ts well with applications<br />

that bring in high-bandwidth I/O from multiple channels<br />

simultaneously and need to move it effi ciently to the fi rst stage<br />

of processing.<br />

Software Environment<br />

The <strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong><br />

supports the nextgeneration<br />

MultiCore Plus ® software environment, which<br />

offers application portability among Mercury platforms.<br />

MultiCore Plus incorporates open standards such as Linux ® ®<br />

and<br />

the Eclipse IDE. The popular Mercury algorithm suite, Scientifi c<br />

Algorithm Library (SAL), in both its single-core and multi-core<br />

(MC SAL) versions, is included in the Mercury MathPack<br />

software package.<br />

Software Development Target Production <strong>System</strong><br />

Eclipse Framework<br />

Mercury Today<br />

TATL<br />

SUPERVISOR<br />

MultiCore Debug<br />

VMC<br />

3rd-Party IDE Plug-ins<br />

Figure 2. MultiCore Plus Software Tools Environment<br />

Applications<br />

<strong>Ensemble</strong> <strong>3000</strong> <strong>Series</strong> 3U <strong>OpenVPX</strong> systems have a unique blend<br />

of high-performance real-time processing and ultra compact<br />

packaging, making them ideal for communications, sensor, and<br />

signal processing applications in space- and weight-constrained<br />

deployments, such as small, unmanned air and ground vehicles.<br />

The processing architecture and performance can accommodate<br />

diverse payload applications including:<br />

• Radar<br />

• Electro-optic/infrared (EO/IR)<br />

• Mission computing<br />

• Signals intelligence<br />

OpenFDK - SVE<br />

ICS<br />

TimeStorm FPGA Driver (FDK) Extended OS<br />

Windows - Linux<br />

Customer Applications<br />

FPGA IP (FDK)<br />

TCP/IP<br />

Ethernet RIO<br />

Third-Party CSN Enabling Software Customer IP<br />

MPI<br />

OFED<br />

VxWorks BSP<br />

HIGH AVAILABILITY<br />

MultiCore MathPack<br />

SYST. MGT. SVCS<br />

DIAGNOSTICS<br />

RT Linux LSP<br />

Specifi cations<br />

Software MultiCore Plus Software Platform<br />

Development tools MultiCore Plus and MathPack 1.0<br />

Operating system support Linux ®<br />

Available Modules<br />

High compute density<br />

Freescale MPC8640 dual-core running at 1.067 GHz<br />

Xilinx Virtex-5 LX-330T or LX-110T<br />

Carrier card XMC site<br />

Carrier card with FPGA XMC site and Virtex-5 LX-330T<br />

<strong>System</strong> controller hub<br />

1 GigE control plane switch, system management hub<br />

Data-plane switch 10-Gbps RapidIO<br />

Internal Communications<br />

RapidIO<br />

One 10-Gbps full-duplex link to each payload slot<br />

Aurora, RapidIO, 10 Gigabit Ethernet<br />

Direct 10-Gbps full-duplex links among grouped payload slots<br />

PCI Express<br />

Direct 16-Gbps full-duplex links between adjacent payload slots<br />

Gigabit Ethernet<br />

1-Gbps full-duplex link to each payload slot<br />

IPMI<br />

400-Kbps I 2 C link to each payload slot<br />

12-Slot Air-Cooled Chassis<br />

Size (excluding connectors) 7U 19-in rackmount chassis<br />

Height 12.22 in<br />

Width 16.45 in<br />

Depth 17.0 in<br />

Card cage 12 slots on 1-inch pitch<br />

Power supplies<br />

Two, each with 750W max output<br />

Cooling<br />

Forced convection (15 CFM min per slot)<br />

~60W per slot at 50°C inlet temperature<br />

Air-Cooled Chassis Environmental<br />

Temperature<br />

Operating 0°C to 50°C up to 10,000 ft MSL<br />

Storage -40°C to +100°C<br />

Humidity 3-95% relative humidity, non-condensing<br />

Shock MIL-S-901 (15g at 40 ms, 30g at 20 ms, 100g at 5 ms)<br />

Vibration MIL-STD-167-1, Telcordia GR-63-CORE (NEBS)<br />

www.mc.com

Some of Mercury’s products are subject to the jurisdiction of the U. S. International Traffi c in Arms Regulations (ITAR). Please contact your Mercury sales representative for more information.<br />

<strong>Ensemble</strong> and Challenges Drive Innovation are trademarks of Mercury Computer <strong>System</strong>s, Inc. RapidIO is a registered trademark of the RapidIO Trade Association. <strong>OpenVPX</strong> is a trademark of VITA. Other<br />

products mentioned may be trademarks or registered trademarks of their respective holders. Mercury Computer <strong>System</strong>s, Inc. believes this information is accurate as of its publication date and is not responsible<br />

for any inadvertent errors. The information contained herein is subject to change without notice.<br />

Copyright © 2009 Mercury Computer <strong>System</strong>s, Inc. 1982.02E-1209-DS-3uvpxsys<br />

Corporate Headquarters<br />

201 Riverneck Road<br />

Chelmsford, MA 01824-2820 USA<br />

+1 (978) 967-1401 +1 (866) 627-6951<br />

Fax +1 (978) 256-3599<br />

www.mc.com<br />

Europe<br />

Mercury Computer <strong>System</strong>s, Ltd.<br />

Unit 1 - Easter Park, Benyon Road Silchester, Reading RG7 2PQ UNITED KINGDOM<br />

+ 44 0 1189 702050 Fax + 44 0 1189 702321<br />

Asia<br />

Nihon Mercury Computer <strong>System</strong>s K.K.<br />

No. 2 Gotanda Fujikoshi Bldg. 4F 5-23-1 Higashi Gotanda Shinagawa-ku, Tokyo 141-0022 JAPAN<br />

+81 3 3473 0140 Fax +81 3 3473 0141<br />

Challenges Drive Innovation