SOHA HASSOUN - Department of Computer Science - Tufts University

SOHA HASSOUN - Department of Computer Science - Tufts University

SOHA HASSOUN - Department of Computer Science - Tufts University

- TAGS

- soha

- hassoun

- tufts

- www.cs.tufts.edu

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

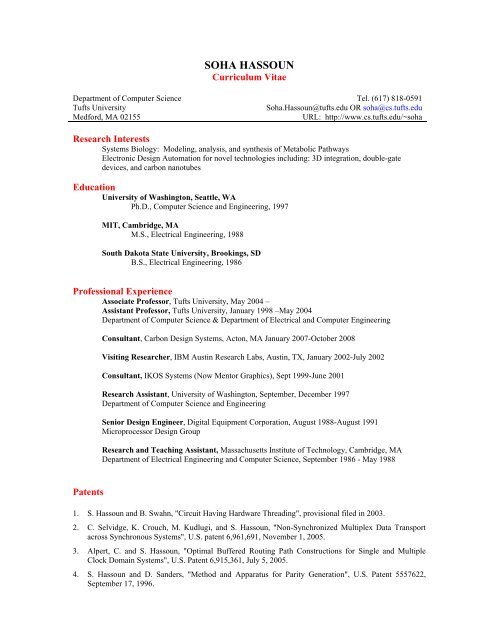

<strong>Department</strong> <strong>of</strong> <strong>Computer</strong> <strong>Science</strong><br />

<strong>Tufts</strong> <strong>University</strong><br />

Medford, MA 02155<br />

<strong>SOHA</strong> <strong>HASSOUN</strong><br />

Curriculum Vitae<br />

Tel. (617) 818-0591<br />

Soha.Hassoun@tufts.edu OR soha@cs.tufts.edu<br />

URL: http://www.cs.tufts.edu/~soha<br />

Research Interests<br />

Systems Biology: Modeling, analysis, and synthesis <strong>of</strong> Metabolic Pathways<br />

Electronic Design Automation for novel technologies including: 3D integration, double-gate<br />

devices, and carbon nanotubes<br />

Education<br />

<strong>University</strong> <strong>of</strong> Washington, Seattle, WA<br />

Ph.D., <strong>Computer</strong> <strong>Science</strong> and Engineering, 1997<br />

MIT, Cambridge, MA<br />

M.S., Electrical Engineering, 1988<br />

South Dakota State <strong>University</strong>, Brookings, SD<br />

B.S., Electrical Engineering, 1986<br />

Pr<strong>of</strong>essional Experience<br />

Associate Pr<strong>of</strong>essor, <strong>Tufts</strong> <strong>University</strong>, May 2004 –<br />

Assistant Pr<strong>of</strong>essor, <strong>Tufts</strong> <strong>University</strong>, January 1998 –May 2004<br />

<strong>Department</strong> <strong>of</strong> <strong>Computer</strong> <strong>Science</strong> & <strong>Department</strong> <strong>of</strong> Electrical and <strong>Computer</strong> Engineering<br />

Patents<br />

Consultant, Carbon Design Systems, Acton, MA January 2007-October 2008<br />

Visiting Researcher, IBM Austin Research Labs, Austin, TX, January 2002-July 2002<br />

Consultant, IKOS Systems (Now Mentor Graphics), Sept 1999-June 2001<br />

Research Assistant, <strong>University</strong> <strong>of</strong> Washington, September, December 1997<br />

<strong>Department</strong> <strong>of</strong> <strong>Computer</strong> <strong>Science</strong> and Engineering<br />

Senior Design Engineer, Digital Equipment Corporation, August 1988-August 1991<br />

Microprocessor Design Group<br />

Research and Teaching Assistant, Massachusetts Institute <strong>of</strong> Technology, Cambridge, MA<br />

<strong>Department</strong> <strong>of</strong> Electrical Engineering and <strong>Computer</strong> <strong>Science</strong>, September 1986 - May 1988<br />

1. S. Hassoun and B. Swahn, "Circuit Having Hardware Threading", provisional filed in 2003.<br />

2. C. Selvidge, K. Crouch, M. Kudlugi, and S. Hassoun, "Non-Synchronized Multiplex Data Transport<br />

across Synchronous Systems", U.S. patent 6,961,691, November 1, 2005.<br />

3. Alpert, C. and S. Hassoun, "Optimal Buffered Routing Path Constructions for Single and Multiple<br />

Clock Domain Systems", U.S. Patent 6,915,361, July 5, 2005.<br />

4. S. Hassoun and D. Sanders, "Method and Apparatus for Parity Generation", U.S. Patent 5557622,<br />

September 17, 1996.

Journals<br />

1. N. Khan, S. Hassoun, and D. Brooks, “A System-Level Study <strong>of</strong> Carbon Nanotubes for Power<br />

Delivery in Single-Die and 3D Architectures”, under review, IEEE Transactions on Very Large<br />

Scale Integration (VLSI) Systems.<br />

2. Khan, S. Alam, and S. Hassoun, “Power Delivery Design for 3D ICs Using Different TSV<br />

Technologies”, Accepted for publication, IEEE Transactions on Very Large Scale Integration<br />

(VLSI) Systems, September 2009.<br />

3. B. Swahn and S. Hassoun, “Thermal Analysis <strong>of</strong> Multi-Fin Devices”, IEEE Transactions on Very<br />

Large Scale Integration (VLSI) Systems, 816-829, July 2008.<br />

4. S. Hassoun, M. Kudlugi, C. Selvidge, and D. Pryor, "A Transaction-Based Unified Architecture for<br />

Simulation and Emulation", IEEE Transactions on Very Large Scale Integration (VLSI) Systems,<br />

pp. 278-287, February, 2005.<br />

5. S. Hassoun, C., Cromer, and E. Calvillo-Gámez, "Static Timing Analysis for Level-Clocked<br />

Circuits in the Presence <strong>of</strong> Cross Talk", IEEE Transactions on <strong>Computer</strong>-Aided Design, September,<br />

2003.<br />

6. D. Dobberpuhl, R. Witek, R. Allmon, R. Anglin, D. Bertucci, S. Britton, L. Chao, R. Conrad, D.<br />

Dever, B. Gieseke, S. Hassoun, G. Hoeppner, K. Kuchler, M. Ladd, B. Leary, L. Madden, E.<br />

McLellan, D. Meyer, J. Montanaro, D. Priore, V. Rajagopalan, S. Samudrala, S. Santhanam. "A<br />

200 MHz 64-b Dual-Issue CMOS Microprocessor", IEEE Journal <strong>of</strong> Solid-State Circuits,<br />

November, 1992, Vol. 27, No. 11. Also appears in Digital Technical Journal. Vol. 4, No. 4, 1992.<br />

Highly-Refereed Conferences (acceptance rates less than 25%)<br />

7. E . Ullah, K. Lee, and S. Hassoun, “A Weighted Graph Algorithm for Identifying Dominant-Edge<br />

Metabolic Pathways”, International Conference on <strong>Computer</strong>-Aided Design (ICCAD), November,<br />

2009.<br />

8. B. Swahn and S. Hassoun, "Gate Sizing: FinFETs vs. 32nm Bulk MOSFETs", Design Automation<br />

Conference (DAC), July, 2006.<br />

9. S. Hassoun and C. Alpert, "Optimal Path Routing in Single and Multiple Clock Domain Systems",<br />

IEEE Transaction on <strong>Computer</strong>-Aided Design (ICCAD), November, 2003.<br />

10. B. Swahn and S. Hassoun, "Hardware Scheduling for Dynamic Adaptability Using External<br />

Pr<strong>of</strong>iling and Hardware Threading", International Conference on <strong>Computer</strong>-Aided Design<br />

(ICCAD), November, 2003.<br />

11. S. Hassoun, C. Alpert, and M. Thiagarajan, "Optimal Buffered Routing Path Constructions for<br />

Single and Multiple Clock Domain Systems", International Conference on <strong>Computer</strong>-Aided Design<br />

(ICCAD), pp. 247—252, November, 2002.<br />

12. S. Hassoun, C. Cromer, and E. Calvillo-Gámez, "Verifying Clock Schedules in the Presence <strong>of</strong><br />

Cross Talk", Design Automation and Test in Europe (DATE) Conference, pp. 346—350, March,<br />

2002.<br />

13. M. Kudlugi, S. Hassoun, C. Selvidge, and D. Pryor, "A Transaction-Based Unified<br />

Simulation/Emulation Architecture for Functional Verification", Design Automation Conference<br />

(DAC), pp. 623—8, June, 2001.<br />

14. S. Hassoun, "Critical Path Analysis Using a Dynamically Bounded Delay Model", Design<br />

Automation Conference (DAC), 260—265, June, 2000.<br />

CV - Soha Hassoun, 1/7 Updated March, 2010

15. S. Hassoun, and C. McCreary, "Regularity Extraction Via Clan-Based Structural Circuit<br />

Decomposition", International Conference on <strong>Computer</strong>-Aided Design (ICCAD), pp. 414—419,<br />

November, 1999.<br />

16. S. Hassoun, and C. Ebeling, "Using Precomputation in Architecture and Logic Synthesis",<br />

International Conference on <strong>Computer</strong>-Aided Design (ICCAD), pp. 316—423, November, 1998.<br />

17. S. Hassoun and C. Ebeling, "Architectural Retiming: Pipelining Latency-Constrained Circuits",<br />

Design Automation Conference (DAC), June, 1996.<br />

18. R. Allmon, B. Benschneider, M. Callander, L. Chao, D. Dever, J. Farrell, N. Fitzgerald, J.<br />

Grodstein, S. Hassoun, L. Hudepohl, D. Kravitz, J. Lundberg, R. Marcello, S. Marino, J. Pickholtz,<br />

R. Preston, M. Richesson, S. Samudrala, and D. Sanders. "System, Process, and Design<br />

Implications <strong>of</strong> a Reduced Supply Voltage Microprocessor", IEEE International Solid-State<br />

Circuits Conference (ISSCC), February, 1990.<br />

19. W. Dally, L. Chao, A. Chien, S. Hassoun, W. Horwat, J. Kaplan, P. Song, B. Totty, and S. Wills,<br />

"Architecture <strong>of</strong> a Message-Driven Processor", International Symposium on <strong>Computer</strong> Architecture<br />

(ISCA), June, 1987. (A re-write <strong>of</strong> this article appears in the Best <strong>of</strong> ISCA 2000.)<br />

Refereed Conferences<br />

20. N. Khan, S. M. Alam, and S. Hassoun “TSV-induced Noise Characterization and Noise Mitigation<br />

using Coaxial TSVs”, IEEE International 3D System Integration Conference, 2009.<br />

21. N. Khan, S. M. Alam, and S. Hassoun “System-Level Comparison <strong>of</strong> Power Delivery Design for<br />

2D and 3D ICs”, IEEE International 3D System Integration Conference, 2009.<br />

22. B. Swahn and S. Hassoun, " METS: Metric for Electro- Thermal Sensitivity, and Its Application<br />

To FinFETs", International Symposium on Quality Electronic Design, March, 2006.<br />

23. S. Hassoun, "Optimal Use Of 2-Phase Transparent Latches In Buffered Maze Routing", IEEE<br />

International Symposium on Circuits and Systems (ISCAS), May, 2003.<br />

24. F. Aloul, S. Hassoun, K. Sakallah, and D. Blaauw, "Robust SAT-Based Search Algorithm for<br />

Leakage Power Reduction", International Workshop on Power and Timing Modeling, Optimization<br />

and Simulation (PATMOS), 2002.<br />

25. S. Hassoun, "Fine Grain Incremental Rescheduling via Architectural Retiming", International<br />

Symposium on System Synthesis (ISSS), pp. 158-163, December, 1998.<br />

Books and Book Chapters<br />

26. S. Hassoun and T. Sasao, Editors, Logic Synthesis and Verification, Kluwer Academic Publishers,<br />

2002. Book has 15 chapters with contributions from 27 experts in the field.<br />

27. S. Hassoun and T. Villa, "Optimization <strong>of</strong> Synchronous Circuits", a chapter in "Logic Synthesis<br />

and Verification", editors: Hassoun and Sasao, Kluwer Academic Publishers, pp. 225—253, 2002.<br />

Other Publications<br />

28. E. Ullah, Kyongbum Lee, and Soha Hassoun, “DOMINANT-EDGE PATHWAY: A Weighted<br />

Graph Algorithm for Identifying Dominant Metabolic Pathways”, International Workshop on Bio<br />

Design Automation, July, 2009. Also appears as “An Algorithm for Identifying Dominant-Edge<br />

Metabolic Pathways”, at the International Workshop on Logic and Synthesis, July 2009.<br />

CV - Soha Hassoun, 2/7 Updated March, 2010

29. J. Rieffel et al., “Evolving S<strong>of</strong>t Robotic Locomotion in PhysX”, Workshop on Computational<br />

Intelligence on Consumer Games and Graphics Hardware, 2009.<br />

30. B. Swahn and S. Hassoun, "Thermal and Sensitivity Analysis <strong>of</strong> Multi-fin devices", International<br />

Workshop on Thermal Investigation <strong>of</strong> ICs and Systems, Sept, 2006.<br />

31. B. Swahn, S. Hassoun, S. Alam, D. Botha, and A. Vidyarthi, “Thermal Analysis <strong>of</strong> FinFETs and its<br />

Application to Gate Sizing”, ACM/IEEE International Workshop on Timing Issues in<br />

the Specification and Synthesis <strong>of</strong> Digital Systems (TAU), February, 2005.<br />

32. A. Vidyarthi and S. Hassoun, “Wave Pipelining for Interconnect”, ACM/IEEE workshop on Logic<br />

and Synthesis, June, 2004.<br />

33. S. Hassoun and D. Marculescu, “Towards GALS Design Methodologies”, workshop on Formal<br />

Methods For Globally Asynchronous Locally Synchronous (GALS) Architecture, September, 2003.<br />

34. J. Xie and S. Hassoun, "A Case Study in IP Functional Customization: The UART 16550",<br />

International Workshop on Logic Synthesis (IWLS), June, 2001.<br />

35. S. Hassoun and C. McCreary, "Clan-Based Structural Circuit Decomposition", International<br />

Workshop on Logic Synthesis (IWLS), June, 1999.<br />

36. S. Hassoun and C. Ebeling, "An Overview <strong>of</strong> Prediction-Based Architectural Retiming",<br />

International Workshop on Timing Issues in the Specification and Synthesis <strong>of</strong> Digital Systems<br />

(TAU), December, 1997.<br />

37. S. Hassoun and C. Ebeling, "Experiments in the Iterative Application <strong>of</strong> Resynthesis and<br />

Retiming", International Workshop on Timing Issues in the Specification and Synthesis <strong>of</strong> Digital<br />

Systems (TAU), December, 1997.<br />

38. S. Hassoun and C. Ebeling, "Sequential Circuit Optimization Using Precomputation", International<br />

Workshop on Logic Synthesis, May, 1997.<br />

39. S. Hassoun and C. Ebeling, "Architectural Retiming: An Overview", International Workshop on<br />

Timing Issues in the Specification and Synthesis <strong>of</strong> Digital Systems (TAU), Seattle, WA,<br />

November, 1995.<br />

40. K. Bolding, S.-C. Cheung, S.-E. Choi, C. Ebeling, S. Hassoun, T. Ngo, and R. Wille, "The Chaos<br />

Router Chip: Design and Implementation <strong>of</strong> an Adaptive Router", International Conference on<br />

Very Large Scale Integration, Grenoble, France, September, 1993.<br />

41. S. Hassoun and G. Borriello, "Improving Finite State Assignment for Two-Level Programmable<br />

Logic Devices", International Workshop on Logic Synthesis (IWLS), May, 1993.<br />

42. S. Hassoun, "A Memory Design for the Message-Driven Processor", MIT VLSI Memo No. 88-564,<br />

August, 1988.<br />

Education Related Publications<br />

43. S. Hassoun and S. Bana, “Practices for Recruiting and Retaining Graduate Women Students in<br />

<strong>Computer</strong> <strong>Science</strong> and Engineering, International Conference on Microelectronic Systems<br />

Education, June, 2001.<br />

44. S. Hassoun and G. Janssen, “First CADathlon Programming Contest Held at 2002 ICCAD“, IEEE<br />

Design and Test Magazine, pp. 104—107, May-June, 2003.<br />

Research Grants & Gifts<br />

1. “Multi-Resolution Partitioning and Kinetic Function Estimation for Dynamic Biochemical Network<br />

Model Development”, NSF, Co-PI Kyongbum Lee, Sept 2008-August 2011, with an REU supplement.<br />

CV - Soha Hassoun, 3/7 Updated March, 2010

2. “Modeling Neuro-Mechnical Control in S<strong>of</strong>t-Tissue Organism”, Co-PI: Barry Trimmer, CRA-W, Sept<br />

08-Aug 09<br />

3. Gift, from the Altera Corp., March 2005<br />

4. “Tools for Double-Gate FETs”, NSF, August 2004-August 2006<br />

5. “<strong>Tufts</strong> CSEMS-Scholars Program", NSF, Co-PI Diane Souvaine, Laurie Baise, Caroline Cao, and<br />

Misha Kilmer, January 2002- January 2006<br />

6. “Tools for Designing and Integrating Configurable Components”, NSF CAREER Award,<br />

February 2001, February 2006<br />

7. “Verification for Deep Submicron Designs”, DAC Design Automation Scholarship, June 2000<br />

8. "Functional and Physical Co-Analysis in Timing Verification", NSF', August 1999-February 2001<br />

9. "Microarchitectural Optimizations and Synthesis", DAC Design Automation Scholarship, June 1998<br />

Select Presentations & Invited Talks<br />

� Computing Research Association Distinguished Lecturer, <strong>University</strong> <strong>of</strong> Virginia, VA, Oct, 2007<br />

� Distinguished Lecturer, Northeastern <strong>University</strong>, Boston, MA, Oct, 2007<br />

� Invited speaker on the topic <strong>of</strong> FinFETs, <strong>University</strong> <strong>of</strong> Toronto, Jan 2006, Altera Corp, Jan. 2006,<br />

<strong>University</strong> <strong>of</strong> Michigan Ann Arbor, February 2006, IBM Research Labs Austin, Oct 2006<br />

� Invited speaker, 2006, 2007, 2008, and 2009. Computing Research Association Graduate Cohort<br />

workshops<br />

� Invited speaker, “Optimal Route Construction”, Cadence Berkeley Labs, August, 2003; Intel,<br />

August, 2003; Harvard <strong>University</strong>, November, 2003; <strong>University</strong> <strong>of</strong> Mass, Amherst, Fall, 2003;<br />

<strong>Tufts</strong> CS seminar, Fall 2003<br />

� Invited speaker, “Let’s Re-sort the Phone Book and Other Topics in <strong>Computer</strong> <strong>Science</strong>”, first year<br />

student orientation at <strong>Tufts</strong>, September, 2003<br />

� Panelist, “Future Leaders and Ideal Hires”, a panel at the International Conference on<br />

Microelectronic Systems Education, June 2001<br />

� Invited speaker, "<strong>Department</strong> and Grassroots: Improving Graduate School Environment for Female<br />

Students". A presentation at the CRA Snowbird Conference, July 1998. [CRA is the annual meeting<br />

for heads <strong>of</strong> <strong>Computer</strong> <strong>Science</strong> <strong>Department</strong>s in the US]<br />

� Invited speaker, “Architectural Retiming”, Intel, February, 1998; Synopsys, March, 1998<br />

Pr<strong>of</strong>essional Service<br />

� Member, Defense <strong>Science</strong> Study Group, Institute for Defense Analysis, 2010-2011<br />

� Associate Editor for IEEE Transactions on <strong>Computer</strong>-Aided Design (TCAD), January 2002-<br />

January 2006<br />

� Associate Editor for IEEE Design and Test Magazine (D&T), January 2002- current<br />

� Design Community Chair and member <strong>of</strong> the Executive Committee for the Design Automation<br />

Conference, June 2008-current<br />

� Technical Program Co-Chair, Design Automation Conference, 2011<br />

� Co-Founder, Executive and Technical Committee member for the International Workshop on<br />

Biology Design Automation, July 2009, and Publicity chair for 2010<br />

CV - Soha Hassoun, 4/7 Updated March, 2010

� PhD Forum Co-Chair (2010) and Panelists (2009) for the Grace Hopper Celebration for Women in<br />

Computing<br />

� Member <strong>of</strong> the IEEE CEDA (Council on Design Automation), and member <strong>of</strong> the technical<br />

activities group, June 2005-current. Vice President <strong>of</strong> Technical Activities committee, July 2007-<br />

August 2008<br />

� Member <strong>of</strong> the CACM (Communication <strong>of</strong> the ACM) Task Force, A group <strong>of</strong> dynamic individual<br />

charged by David Patterson, President <strong>of</strong> ACM, to remap the key flag publication<br />

� Advisory Board member for ACM's Special Interest on Design Automation (SIGDA), 1999-2004<br />

� Director <strong>of</strong> Educational Activities, ACM/SIGDA. Initiated, organized, and currently direct the<br />

following programs: Ph. D. Forum at DAC, CADathlon at ICCAD, Design Automation Summer<br />

School. Also oversee SIGDA's International Lectureship Program<br />

� Executive Committee member for the International Conference on <strong>Computer</strong>-Aided Design<br />

(ICCAD), June 2001-2007<br />

� General Chair, the International Conference on <strong>Computer</strong>-Aided Design (ICCAD), 2006<br />

� Technical Program Chair, the International Conference on <strong>Computer</strong>-Aided Design (ICCAD), 2005<br />

� Technical Program Vice Chair, the International Conference on <strong>Computer</strong>-Aided Design (ICCAD),<br />

2004<br />

� Chairperson for the technical sub-committee on Synthesis for the Design Automation Conference<br />

(DAC), 2003, 2004, and 2005<br />

� Technical Program Committee member for the Design Automation Conference (DAC), 2002-2005<br />

� General Chairperson for The International Workshop on Logic and Synthesis, 2002<br />

� Technical Program Chairperson for The International Workshop on Logic and Synthesis, 2001<br />

� Technical Program Committee Member for The International Workshop on Logic and Synthesis,<br />

2000-2005<br />

� Technical Program Committee Member for The International Workshop on Timing Issues in the<br />

Specification and Synthesis <strong>of</strong> Digital Systems, 2002-2006<br />

� Guest Editor, with Leon Stok (IBM Watson) and Steve Nowick (Columbia), for IEEE Transactions<br />

on <strong>Computer</strong>-Aided Design special issue on Logic Synthesis, May 2003<br />

� Guest Editor, with Sani Nassif (IBM Austin Research Labs) for IEEE Design and Test Magazine<br />

special issue on Power Grid Design and Analysis, May-June 2003<br />

� Guest Editor, with Yong-Bin Kim (Northeastern) and Fabrizio Lombardi (Northeastern), for IEEE<br />

Design and Test Magazine special issue on Clockless Design, November-December 2003<br />

� Reviewer: IEEE Transactions on <strong>Computer</strong>-Aided Design, ACM Transaction on Design<br />

Automation <strong>of</strong> Electronic Systems, IEEE Transaction on VLSI, IEEE Transaction on Electron<br />

Devices, and other conferences and workshops<br />

� Reviewer: Best paper selection committee, ICCAD 2003<br />

� Reviewer: NSF Panel, 2002, 2003, 2004, 2007, 2008, 2009; MICRO program, 2003, 2004<br />

Service and Activities at <strong>Tufts</strong><br />

� Undergraduate Committee Chair, 2008-2009<br />

� Member, Campus Planning and Development Committee (CPDC), September 2001- May 2005.<br />

Fall 2008-current<br />

� Member, Equal Educational Opportunity Committee (EEOC), September 2001- May 2004<br />

� Graduate Program Director, 2005-2006, and member <strong>of</strong> the graduate committee 2001-2006<br />

� Faculty search committee, 2003-2004, 2004-2005, 2008-2009, 2009-2010<br />

Teaching<br />

VLSI & Architecture<br />

� Introduction to VLSI, EE/COMP 103<br />

� Advanced VLSI Design, EE 104<br />

CV - Soha Hassoun, 5/7 Updated March, 2010

� <strong>Computer</strong> Architecture, COMP 40<br />

� <strong>Computer</strong> Organization, EE 126<br />

� Advanced <strong>Computer</strong> Architecture, COMP 150-ACA<br />

� Analog Electronics, EE 11<br />

� <strong>Computer</strong>-Aided Design (Novel technologies) COMP 150-CAD<br />

� <strong>Computer</strong>-Aided Design (Algorithms) COMP 150-CAD<br />

Other<br />

� Algorithms, COMP 160<br />

� Data Structures, COMP 15<br />

� Stochastic Search and Genetic Algorithms, COMP 150-GA<br />

� Exploring <strong>Computer</strong> <strong>Science</strong>, an introductory course, COMP 10<br />

Research Student Advising<br />

� 4 current Ph.D. students; 1 master; 4 undergrads<br />

� Supervised 1 PhD, 8 master projects, and 14 senior design projects<br />

Awards & Distinction<br />

� NSF CAREER award<br />

� IEEE Senior member<br />

� ACM/SIGDA Distinguished Service Award, June 2007<br />

� <strong>Tufts</strong> <strong>University</strong> Mellon Fellowship, Spring 2003<br />

� ACM/SIGDA Technical Leadership Award, June 2002<br />

� ACM/SIGDA Service Award, June 2000<br />

� 1995-1996, Women and Minorities Fellowship, CSE Dept., <strong>University</strong> <strong>of</strong> Washington<br />

� 1991-1992, Digital Equipment Corporation Fellowship<br />

� 1986-1987, Tau Beta Pi Fellow<br />

CV - Soha Hassoun, 6/7 Updated March, 2010