GENERADOR DE RUIDO ESTOCÁSTICO COLOREADO ...

GENERADOR DE RUIDO ESTOCÁSTICO COLOREADO ...

GENERADOR DE RUIDO ESTOCÁSTICO COLOREADO ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

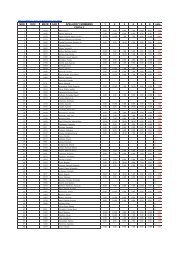

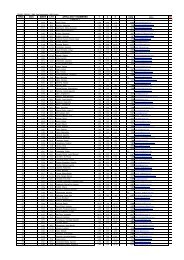

1sourcevalid0selecciona ki1:0Input4a[18]:[18]X r [36]:[36]1/f^23source realsel(1:0)0-a[18]:[18]a = b X q + rb[18]:[18]q[36]:[0]r[18]:[18]1sink realenac(13:0)|a|Magnitudeb[18]:[18]1/f^31-MUXDivider1Scope2Increment Decrementd(17:0)q(8:0)a[18]:[18]1/f1/f^42-3-2source imaga[18]:[18]a = b X q + rb[18]:[18]q[36]:[0]r[18]:[18]2sink imagb[18]:[18]X r [36]:[36]MultiplexerDivider3Scope1Fig. 1 Bloque generador de vector f k , divisor.espectro de potencia plano, función densidad deprobabilidad uniforme y valor medio cero.2. Se calcula la transformada rápida de Fourier (FFT)(1)obteniéndose el vector complejo y k(1)3. Se multiplica el vector complejo y k por f --k/2(2)obteniéndose y k .(2)4. Se simetriza y k para que represente una funciónreal del tiempo y se realiza la IFFT. Luego dedescartar las pequeñas componentes imaginariasque surgen del cálculo se obtiene la serie temporalcuyo espectro de potencia tiene la forma f -k . Estemétodo constructivo produce además ruidos noGausianos.La metodología utilizada para la implementación enhardware sigue los mismos lineamientos expuestos comose describe en la sección siguiente.3. DISEÑO EN HARDWAREEl diseño se realizó en el paquete Simulink © deMATLAB © con el toolbox Altera DSP Builder Blocksetversión 7.2 © . Este toolbox contiene todos los bloquesadmitidos por los distintos modelos de FPGA deALTERA. La principal ventaja de programar en el entornoMATLAB © es la simulación del sistema utilizando todaslas herramientas disponibles tales como generadores deseñales e instrumentos virtuales de medición que permitentestear cada etapa del proyecto. Además de las funcionesbásicas, el toolbox de ALTERA consta de funciones máscomplejas agrupadas en la librería ALTERA IP-MegaCores © [14,15].Una vez finalizado el diseño, el proyecto se compiló ypor último se llevó al QUARTUS © II Web Edition para laposterior programación de la FPGA.La arquitectura adoptada consta de cuatro etapasbásicas. La primera etapa (ver Fig. 2) realiza la FFT de unruido blanco uniforme con media cero. Existen dosopciones para ingresar el ruido blanco, la primera esutilizar un generador externo a la placa (como se hizo eneste caso), y la segunda es generar el ruido blanco en lamisma FPGA empleando sistemas caóticos randomizados[4,5].El segundo bloque (ver Fig. 1) se encarga de “colorear”el espectro recibido, es decir convertir el espectro del ruidoblanco en uno de ruido de tipo f -k , con k = 1,2,3,4. Desdeel punto de vista de las aplicaciones no es de interésutilizar valores mayores de k pues el espectro se vuelvedemasiado concentrado en las bajas frecuencias.En la tercera etapa (ver Fig. 3) se realiza la IFFT de laseñal coloreada y finalmente la cuarta etapa prepara losdatos para la salida.Para implementar las funciones de FFT e IFFT seutilizo un bloque de la librería de ALTERA IP-MegaCores © , fft_v7_2. Este bloque permite la selecciónen forma externa de la transformación a realizarse (FFT oIFFT). El bloque calcula la transformada discreta deFourier (DFT) de una señal de entrada muestreada delongitud N. Para reducir la complejidad del cálculo utilizael algoritmo Cooley-Tukey radix-r decimación-enfrecuencia(DIF) FFT. Este algoritmo particionarecursivamente la secuencia de entrada en N/r secuenciasde longitud r y requiere log r (N) etapas de cálculo. Sepuede adoptar para r uno de los valores 2, 4 ó 16.Se utilizó aritmética de punto fijo, con resolución de 18bits. Sin embargo la función FFT MegaCore © utilizainternamente aritmética de punto flotante en bloque (BFP)para realizar los cálculos. La arquitectura BFP es uncompromiso entre las aritméticas de punto fijo y de puntoflotante.