GENERADOR DE RUIDO ESTOCÁSTICO COLOREADO ...

GENERADOR DE RUIDO ESTOCÁSTICO COLOREADO ...

GENERADOR DE RUIDO ESTOCÁSTICO COLOREADO ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

1sourcevalid0selecciona ki1:0Input4a[18]:[18]X r [36]:[36]1/f^23source realsel(1:0)0-a[18]:[18]a = b X q + rb[18]:[18]q[36]:[0]r[18]:[18]1sink realenac(13:0)|a|Magnitudeb[18]:[18]1/f^31-MUXDivider1Scope2Increment Decrementd(17:0)q(8:0)a[18]:[18]1/f1/f^42-3-2source imaga[18]:[18]a = b X q + rb[18]:[18]q[36]:[0]r[18]:[18]2sink imagb[18]:[18]X r [36]:[36]MultiplexerDivider3Scope1Fig. 1 Bloque generador de vector f k , divisor.espectro de potencia plano, función densidad deprobabilidad uniforme y valor medio cero.2. Se calcula la transformada rápida de Fourier (FFT)(1)obteniéndose el vector complejo y k(1)3. Se multiplica el vector complejo y k por f --k/2(2)obteniéndose y k .(2)4. Se simetriza y k para que represente una funciónreal del tiempo y se realiza la IFFT. Luego dedescartar las pequeñas componentes imaginariasque surgen del cálculo se obtiene la serie temporalcuyo espectro de potencia tiene la forma f -k . Estemétodo constructivo produce además ruidos noGausianos.La metodología utilizada para la implementación enhardware sigue los mismos lineamientos expuestos comose describe en la sección siguiente.3. DISEÑO EN HARDWAREEl diseño se realizó en el paquete Simulink © deMATLAB © con el toolbox Altera DSP Builder Blocksetversión 7.2 © . Este toolbox contiene todos los bloquesadmitidos por los distintos modelos de FPGA deALTERA. La principal ventaja de programar en el entornoMATLAB © es la simulación del sistema utilizando todaslas herramientas disponibles tales como generadores deseñales e instrumentos virtuales de medición que permitentestear cada etapa del proyecto. Además de las funcionesbásicas, el toolbox de ALTERA consta de funciones máscomplejas agrupadas en la librería ALTERA IP-MegaCores © [14,15].Una vez finalizado el diseño, el proyecto se compiló ypor último se llevó al QUARTUS © II Web Edition para laposterior programación de la FPGA.La arquitectura adoptada consta de cuatro etapasbásicas. La primera etapa (ver Fig. 2) realiza la FFT de unruido blanco uniforme con media cero. Existen dosopciones para ingresar el ruido blanco, la primera esutilizar un generador externo a la placa (como se hizo eneste caso), y la segunda es generar el ruido blanco en lamisma FPGA empleando sistemas caóticos randomizados[4,5].El segundo bloque (ver Fig. 1) se encarga de “colorear”el espectro recibido, es decir convertir el espectro del ruidoblanco en uno de ruido de tipo f -k , con k = 1,2,3,4. Desdeel punto de vista de las aplicaciones no es de interésutilizar valores mayores de k pues el espectro se vuelvedemasiado concentrado en las bajas frecuencias.En la tercera etapa (ver Fig. 3) se realiza la IFFT de laseñal coloreada y finalmente la cuarta etapa prepara losdatos para la salida.Para implementar las funciones de FFT e IFFT seutilizo un bloque de la librería de ALTERA IP-MegaCores © , fft_v7_2. Este bloque permite la selecciónen forma externa de la transformación a realizarse (FFT oIFFT). El bloque calcula la transformada discreta deFourier (DFT) de una señal de entrada muestreada delongitud N. Para reducir la complejidad del cálculo utilizael algoritmo Cooley-Tukey radix-r decimación-enfrecuencia(DIF) FFT. Este algoritmo particionarecursivamente la secuencia de entrada en N/r secuenciasde longitud r y requiere log r (N) etapas de cálculo. Sepuede adoptar para r uno de los valores 2, 4 ó 16.Se utilizó aritmética de punto fijo, con resolución de 18bits. Sin embargo la función FFT MegaCore © utilizainternamente aritmética de punto flotante en bloque (BFP)para realizar los cálculos. La arquitectura BFP es uncompromiso entre las aritméticas de punto fijo y de puntoflotante.

PulsesopPulseeopUniform RandomNumberibitInput2reset0Constant41Constant3ibitInput3ibitInputi17:00Input1Constant11Constant27reset12 nsClockreset_ninversesink_validsink_sopsink_eopsink_real(17:0)sink_im ag(17:0)sink_error(1:0)source_readyfft 7.2FFTSignal Compilersink_readysource_error(1:0)source_sopsource_eopsource_validsource_exp(5:0)source_real(17:0)source_im ag(17:0)4sop5eop1sour valid36sour exp1sour real2sour imagFig. 2 Bloque FFT.3sop4eop1sink real2sink imag0Constant45reset11Constant61Constant7reset_ninversesink_validsink_sopsink_eopsink_real(17:0)sink_imag(17:0)sink_error(1:0)source_readyfft 7.2IFFTsink_readysource_error(1:0)source_sopsource_eopsource_validsource_exp(5:0)source_real(17:0)source_imag(17:0)obitOutput12sour exp21sour re2Fig. 3 Bloque IFFT.1sour re2(17:0)01234567891011121314151617Bus Splitter4012345678(16:0)910111213141516Bus Builder43sour exp110++ + r2 +|a|sour exp2MagnitudeParallel Adder Subtractora(17:0)distance(4:0) directionBarrel Shifterr(17:0)(7:0)01234567Bus Splitter2(16:0)012345678910111213141516Bus Splitter0123456789(17:0)1011121314151617Bus Buildero17:0salida realScope15Fig. 4 Bloque de ajuste de ganancia.

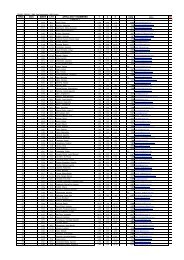

Los datos de entrada ingresan como valores en puntofijo. Internamente, los pares de valores enteros complejosse representan con un único factor de escala: luego de cadaetapa de la FFT, se detecta el máximo valor de salida y losresultados intermedios son cambiados de escala paramejorar la precisión. El exponente almacena la cantidad dedesplazamientos utilizados para realizar el cambio deescala. Las salidas source_real y source_imag combinadascon la salida source_exp entregan las partes real eimaginaria respectivamente.Las Figs. 1 a 4 muestran el caso de generación de unruido 1/f pero la misma metodología de diseño permite laselección entre cuatro tipos de ruido de la forma f -k , con k= 1, 2, 3, 4; mediante una entrada externa. Primeramentese ingresa al bloque FFT, por el pin sink_real, con unaseñal de ruido blanco, generada por ejemplo con la fuenteUniform Random Number de Simulink © que presenta unespectro de potencia plano. En el caso del ejemplo losniveles utilizados en la entrada sink_real van desde -2 12 a2 12 , y son digitalizados a 18 bits. Por su parte la entradasink_imag es seteada a cero (es decir que la señal deentrada es real).El bloque FFT fue previamente parametrizado delsiguiente modo: 1) una transformada de longitud N=2 14 , 2)una resolución de 18 bits, 3) la familia Stratix II deAltera © . El resto de los parámetros se mantuvieron con losvalores prefijados por defecto. Las partes real e imaginariade la FFT del ruido blanco son entregadas por las salidassource_real y source_imag del bloque FFT. Ambas salidasse dividen por el vector f 0.5 (en el caso general se dividepor f 0.5k ).Cuando la salida source_valid=1 hay salida válida ensource_real y source_imag y comienza a incrementarse uncontador para generar un vector de frecuencia a pasos f pasodados por la expresión (1), donde T ck es el período dereloj. A excepción del caso k=2, la salida del contadoringresa a un bloque que realiza la raíz cuadrada (ver Fig.1)y la salida de ese bloque pasa por un sistema compuesto demultiplicadores para generar f 0.5k −14f = 2 / T(1)pasoEl valor de k se selecciona a través de una entradaexterna de un multiplexor. La salida divide al espectrocomplejo (source_real y source_imag) generando así a lasalida de los divisores las componentes espectrales real eimaginaria del ruido elegido.Una vez obtenida la FFT requerida, ingresamos a unsegundo bloque FFT con la entrada inverse=1, que realizala transformada inversa de Fourier.Finalmente un último bloque ajusta la ganancia totaldel proceso. En primer lugar se debe convertir nuevamentecka punto fijo tomando en cuenta el valor de las salidassource_exp de los dos bloques FFT (el que realiza la FFTy el que realiza la IFFT). Además la función MegaCore ©no aplica internamente el factor de escala 1/N=2 -nrequerido por la IFFT. Luego hay que aplicarloexternamente (en el caso de la Fig. 4 n = 10).4. RESULTADOSEn las Figs. 5 y 6 se muestran los ruidos 1/f y 1/f 2generados mediante la arquitectura descripta. El valor de mindicado en esas figuras es la pendiente estimada de lospuntos ajustados a una recta mediante la función polyfit deMATLAB © . También se presentan el período de muestreo(T ck ) y el valor de k elegido.Puede verse que el espectro obtenido presenta la formade ruido coloreado esperado en cada caso.5. CONCLUSIÓN Y TRABAJO FUTUROSe ha diseñado, un generador de ruido estocásticocoloreado, del tipo f -k , con vistas a su implementación enuna placa FPGA. El sistema permite seleccionar el tipo deruido deseado dentro del rango k=1 a 4.En esta primera etapa no era importante laoptimización de recursos si no el definir una metodologíageneral de diseño que fuera aplicable no sólo al ruido f -ksino también a otros ruidos estocásticos de interés, talescomo los gaussianos fraccionarios. No obstante en unasegunda etapa debe realizarse la optimización de recursosutilizados en cada caso [16-18].La principal conclusión en esta etapa de diseño es laventaja de la utilización del entorno Simulink para diseñoy simulación, dado que permite en forma relativamentesimple una futura ampliación. Por otra parte basándose enla misma metodología se prevé la implementación de otrostipos de ruido estocástico.6. AGRA<strong>DE</strong>CIMIENTOSEste trabajo ha sido parcialmente financiado porCONICET (PIP2004), ANPCyT (PICT 04) y UNMDP.7. REFERENCIAS[1] H. A. Larrondo, M. T. Martín, C. M. González, A. Plastinoand O. A. Rosso, “Intensive Statistical Complexity Measureof Pseudorandom Bit Generators”, Physica A, vol. 356, pp133-138, 2005.

ln |FFT| 2ln |FFT| 2201510506 8 10 12 14ln f(Hz)3025201510T ck= 2 10 -6 , k= 1, m= -1.03Fig. 5 Espectro de potencial del ruido 1/fT ck= 2 10 -6 , k= 2, m= -1.9954 6 8 10 12 14ln f(Hz)Fig. 6 Espectro de potencial del ruido 1/f 2[2] H. A. Larrondo, M. T. Martín, C. M. González, A. Plastinoand O. A. Rosso, “Random Number Generators andCausality”, Physics Lett. , vol. 352, pp. 421-425, 2006.[3] L. M. Pecora, T. L. Carroll, “Synchronization in chaoticsystems”, Phys. Rev. Lett. , vol. 64, pp. 821-824, 1990.[4] R. M. Hidalgo, J. G. Fernández, R. R. Rivera, H. A.Larrondo, “Versatile DSP-based chaotic communicationsystem”, Electronic Lett., vol. 37, pp. 1204-1205, 2001[5] J. G. Fernández, H. A. Larrondo, H. A. Slavin, D. G. Levin,R. M. Hidalgo, R. R. Rivera, “Masking properties of APDcommunication systems”, Physica A, vol. 354, pp. 281-300,2005.[6] S. Callegari, R. Rovatti, G. Setti, “Spectral Properties ofChaos-Based FM Signals: theory and simulation results”,IEEE Trans. Circuits Sys. I, vol. 50, no. 1, pp. 3-15 , 2003.[7] L. De Micco, R. A. Petrocelli, H. A. Larrondo, “ConstantEnvelope Wideband Signals using Arbitrary Chaotic Maps”,Proceedings of XII RPIC, 2007, ISBN 978-987-1242-23-8,pp. 381.[8] G. Setti, G. Mazzini, R. Rovatti, S. Callegari, “StatisticalModeling of Discrete-Time chaotic processes: Basic Finite-Dimensional Tools and Applications”, Proceedings of theIEEE, vol 90, no. 5, pp. 662-690, 2002.[9] R. A. Petrocelli, L. De Micco, D. O. Carrica, H. A.Larrondo, “Acquisition of Low Frequency SignalsImmersed in Noise by Chaotic Sampling and FIR filters”,Proceedings of WISP2007, ISBN 1-4244-0830-X, vol. 1,2007, pp. 351-356.[10] C. M. Arizmendi, F. Family, AL Salas-Brito, “Quencheddisorder effects on deterministic inertia ratchets”, Phys. Rev.E, vol. 63, pp 0611041-0611045, 2001.[11] O. A. Rosso, H. A Larrondo, M. T. Martin, A. Plastino, andM. A. Fuentes “Distinguishing noise from chaos” Phys. Rev.Lett., vol. 99, pp. 154102-154106, 2007.[12] C. M. González, H. A. Larrondo, C. A Gayoso, L. J.Arnone, “Secuencias Binarias Pseudo aleatorias generadaspor un mapa caótico 2D”, X Workshop de IBERCHIP,2004.(http://www.iberchip.org/iberchip2004/articles/11-2-CMGONZALEZ-MDP_IBERCHIP_04.PDF )[13] E. C. M. González, H. A. Larrondo, C. A Gayoso, L. J.Arnone, “Generación de Secuencias Binarias PseudoAleatorias por Medio de un Mapa Caótico 3D” ,IXWorkshop de IBERCHIP, 2003.(http://www.iberchip.org/IX/Articles/PAP-013.pdf )[14] Para información sobre las FPGA de ALTERAhttp://www.altera.com/[15] Para información sobre las herramientas de diseñohttp://www.altera.com/products/ip/design/basesuite/ipbasesuite.html.[16] E. Boemo and G. Sutter, “Permutación de los Datos deEntrada como Estrategia de Diseño de Bajo Consumo:Algunos Ejemplos en FPGAs”, en ComputaciónReconfigurable & FPGAs, ISBN 84-60099-28-8, pp. 225-232, 2003.[17] S. Lopez-Buedo, J. Garrido and E. Boemo, “ThermalTesting on Reconfigurable Computers”, IEEE Design &Test of Computers, vol. 17, no. 1, pp. 84-90, 2000.[18] E. Todorovich, M. Gilabert, G. Sutter, S. Lopez-Buedo andE. Boemo, “A Tool for Activity Estimation in FPGAs”,Lecture Notes in Computer Science, vol. 2438, pp. 340-349,2002.