Solution Final automne 2009 - Moodle

Solution Final automne 2009 - Moodle

Solution Final automne 2009 - Moodle

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

INF8500 Examen final Automne <strong>2009</strong><br />

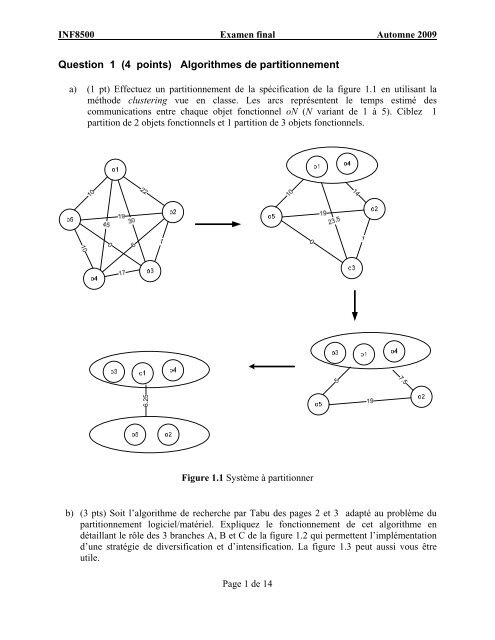

Question 1 (4 points) Algorithmes de partitionnement<br />

a) (1 pt) Effectuez un partitionnement de la spécification de la figure 1.1 en utilisant la<br />

méthode clustering vue en classe. Les arcs représentent le temps estimé des<br />

communications entre chaque objet fonctionnel oN (N variant de 1 à 5). Ciblez 1<br />

partition de 2 objets fonctionnels et 1 partition de 3 objets fonctionnels.<br />

10<br />

22<br />

10<br />

14<br />

6<br />

10<br />

0<br />

0<br />

5<br />

7.5<br />

6.25<br />

Figure 1.1 Système à partitionner<br />

b) (3 pts) Soit l’algorithme de recherche par Tabu des pages 2 et 3 adapté au problème du<br />

partitionnement logiciel/matériel. Expliquez le fonctionnement de cet algorithme en<br />

détaillant le rôle des 3 branches A, B et C de la figure 1.2 qui permettent l’implémentation<br />

d’une stratégie de diversification et d’intensification. La figure 1.3 peut aussi vous être<br />

utile.<br />

Page 1 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Figure 1.2 Algorithme de recherche Tabu pour le partitionnement logiciel/matériel<br />

Page 2 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Figure 1.3 Structure de données pour l’algorithme de recherche Tabu<br />

La méthode Tabu se classe dans la catégorie des algorithmes hill climb.<br />

Contrairement à l’approche de recuit simulé, la recherche Tabu contrôle les déplacements de<br />

blocs de manière intelligente plutôt qu’avec le hasard comme c’est le cas du recuit simulé.<br />

Plus précisément, on garde une liste des voisinages visités récemment dans une liste Tabu. Il<br />

s’agit en fait d’une queue de profondeur (degree) de 7 à 20 ou encore de .5N1/2 à 21/2 où N<br />

est fonction de la dimension du problème.<br />

Avec le test de A, deux situations peuvent survenir :<br />

1) À partir de la solution courante, on va tout d’abord explorer des solutions voisines (par<br />

exemple en déplaçant un objet du logiciel au matériel ou vide versa). Pour ces solutions<br />

voisines (k = 1 à M), on calcule un coût dcost(k). Si ce dcost(k) est plus petit que le<br />

meilleur dcost obtenu à ce jour et que k n’est pas dans la liste Tabu on conserve la<br />

solution (permet la diversification).<br />

2) Si dcost(k) est plus grand que le meilleur dcost obtenu à ce jour ou si k est pas dans la<br />

liste Tabu on va donner une pénalité à k (penalty(k)) qui est ajouté à dcost(k). Cette<br />

pénalité est fonction de la fréquence d’apparition d’un certain sous-voisinage de k (k bits<br />

LSB). Plus ce sous-voisinage est apparu souvent plus la pénalité est grande (permet la<br />

diversification). Par contre cette dernière est moins grande si k est apparu au cours des<br />

Page 3 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Kq dernières itérations, ce qu’on appelle promising region et qui permet l’intensification.<br />

<strong>Final</strong>ement, on sélectionne le plus petit dcost(k) pour les k qui ne sont pas dans la liste<br />

Tabu et pour ceux qui le sont on choisi le k le plus profond dans la queue.<br />

<strong>Final</strong>ement, on détermine le meilleur dcost parmi 1) et 2) qui devient alors Snow.<br />

Page 4 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Question 2 (4 points) Partitionnement vs ordonnancement<br />

La figure 2.1 représente un résultat de partitionnement logiciel/matériel sur 8 tâches (objets<br />

fonctionnels). On souhaite maintenant ordonnancer ce résultat. Les contraintes au niveau<br />

ressource sont les suivantes : 1 processeur pour l’exécution du logiciel, 2 coprocesseurs pour<br />

l’exécution du matériel, 1 bus pour le processeur, 1 bus partagé entre le logiciel et le matériel et 1<br />

bus pour le matériel. Également, considérez qu’une tâche ne peut écrire et lire au même moment<br />

sur un bus.<br />

À partir de ce résultat, complétez l’ordonnancement de la figure 2.2 en vous inspirant de<br />

l’algorithme vu en classe qui se base sur le list scheduling (voir Annexe)<br />

Figure 2.1 Résultat de partitionnement. Chaque nœud est étiqueté d’un numéro entre 1 et 8, suivi<br />

d’une valeur en parenthèse qui représente le temps d’exécution de ce nœud. La valeur associée à<br />

chaque arc représente le temps de communication.<br />

Page 5 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Figure 2.2 Ordonnancement logiciel/matériel. À compléter.<br />

Page 6 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

QUESTION 3 (4 points) Architecture d’un testbench<br />

a) (2 pts) Donnez le schéma général d’un testbench (banc d’essai) qui doit contenir les<br />

éléments suivants : agent, scoreboard, checker, driver, monitor et generator. Puis,<br />

expliquez pourquoi dans le laboratoire no 3 vous n’avez pas eu recours au Driver et au<br />

Receiver Indiquez brièvement à quoi servent ces 2 éléments.<br />

b) (.5 pt) À quel endroit retrouve-t-on généralement les assertions dans un banc d’essai<br />

Justifiez.<br />

Avec le DUT, surtout si on a besoin de variable locale (en boîte blanche).<br />

Page 7 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

c) (1.5 pts) Soit l’interface System Verilog de la figure 3.1, le programme test (testbench) de<br />

la figure 3.2a et finalement un arbitre (DUT) de la figure 3.2b. Complétez le diagramme<br />

temporel de la figure 3.3.<br />

interface arb_if (input bit clk);<br />

logic [1:0] grant, request;<br />

logic reset;<br />

clocking cb @(posedge clk);<br />

output request<br />

input grant<br />

endclocking<br />

modport TEST(clocking cb, output reset);<br />

modport DUT(input request, reset, output grant);<br />

endinterface<br />

Figure 3.1 Interface du système<br />

‘timescale 1ns/1ns<br />

program test(arb_if.TEST arbif)<br />

initial begin<br />

//petit testbench artisanal…<br />

#7 arbif.cb.request

INF8500 Examen final Automne <strong>2009</strong><br />

Question 4 (4 points) Assertions avec System Verilog<br />

a) (1 pt) Quelle différence faites-vous entre une assertion de type assert et un point de<br />

couverture Expliquez.<br />

Les assertions permettent de détecter les comportements non-souhaitables alors que les points de<br />

couverture (couverture fonctionnelle) permettent de répertorier les comportements désirés.<br />

b) (3 pts) Soit l’interface d’un module Verilog qui réalise l’arbitration sur un bus tel que<br />

présenté à la figure 4.1 (page suivante). Décrivez le rôle joué de chacune des assertions<br />

ci-après (no 1 à 3) et proposez à l’aide d’un diagramme temporel une situation qui la fait<br />

échouer.<br />

Assertion no 1 :<br />

property property1;<br />

(@(posedge clk) roundORpriority && $rose (req[0]) |-> ##[1:4] gnt[0]);<br />

endproperty<br />

assert_property1: assert property (property1);<br />

L’assertion no 1 permet de s’assurer que la réponse à la requête i se fait entre 1 et 4 cycles en<br />

mode RR<br />

Assertion no 2 :<br />

property property2(i);<br />

(@(posedge clk) disable iff (rst)<br />

gnt[i] |=> (~gnt[i] throughout (req[i]) [-> 1]);<br />

endproperty<br />

generate<br />

begin<br />

genvar i;<br />

for (i=0; i

INF8500 Examen final Automne <strong>2009</strong><br />

Assertion no 3 :<br />

property property3(i, j);<br />

@(posedge clk) disable iff (rst)<br />

!roundORpriority && (i > j) && $rose(req[i])<br />

##1 (~gnt[i] throughout (gnt[j]) [-> 1]) |-> 0;<br />

endproperty<br />

generate<br />

begin<br />

genvar i, j;<br />

for (i=0; i

INF8500 Examen final Automne <strong>2009</strong><br />

Question 5 (4 points) Génération aléatoire et vérification fonctionnelle<br />

Soit le DUT (Design Under Test) et son testbench de l’unité arithmétique et logique (présenté en<br />

classe lors du dernier cours) que nous souhaitons vérifier. La figure 5.1 présente les contraintes<br />

que l’on donne lors de la génération aléatoire d’un stimulis. La figure 5.2 présente des points de<br />

couverture que l’on souhaite couvrir pour tenter d’obtenir 100% de couverture fonctionnelle.<br />

a) (1 pt) Décrivez textuellement les contraintes de notre stimulis (Figure 5.1)<br />

b) (1.5 pt) Décrivez textuellement la couverture que l’on souhaite faire ici (Figure 5.2)<br />

c) (1 pts) À partir de cette information (figure 5.1 et 5.2) set de la spécification de l’unité<br />

arithmétique et logique donné en Annexe, croyez-vous que l’on puisse obtenir (ou tendre<br />

vers) 100% de couverture fonctionnelle en supposant que l’on simule durant 5ms.<br />

Justifiez clairement votre réponse.<br />

d) (.5 pt) Si vous avez bien compris le lien entre les figures 5.1 et 5.2 et en sachant que<br />

plusieurs générateurs peuvent être définis pour un même testbench, vous devriez<br />

maintenant être en mesure de répondre à la question suivante : À quel endroit devrait<br />

retrouver les groupes de couverture dans un testbench Justifiez.<br />

class Packet;<br />

rand reg [`REGISTER_WIDTH-1:0] src1;<br />

rand reg [`REGISTER_WIDTH-1:0] src2;<br />

rand reg [`REGISTER_WIDTH-1:0] imm;<br />

rand reg [`REGISTER_WIDTH-1:0] mem_data;<br />

rand reg immp_regn_op_gen;<br />

rand reg [2:0] operation_gen;<br />

rand reg [2:0] opselect_gen;<br />

reg<br />

enable;<br />

string<br />

name;<br />

constraint Limit {<br />

src1 inside {[-10:10],0,32'hffffffff,32'h55555555,32'haaaaaaaa};<br />

src2 inside {[-10:10],0,32'hffffffff,32'h55555555,32'haaaaaaaa};<br />

imm inside {[0:65534]};<br />

mem_data inside {[0:65534]};<br />

//payload_size inside {[9:12]};<br />

opselect_gen inside {[0:1]};<br />

if ((opselect_gen == `ARITH_LOGIC)){<br />

operation_gen inside {[0:7]}; }<br />

else if ((opselect_gen == `SHIFT_REG)) {<br />

immp_regn_op_gen inside {0};<br />

operation_gen inside {[0:3]}; }<br />

}<br />

extern function new(string name = "Packet");<br />

endclass<br />

Page 11 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Figure 5.1 Contraites System Verilog lors de la génération aléatoire d’un stimulis<br />

a) Comme on peut le voir, la plage des registres src1 et src2 est redéfinie pour tenir compte<br />

des négatifs et des points particuliers désirés, ce qui n’était pas le cas de l’exemple<br />

présenté au dernier cours. Également, on se concentre ici sur les opérations<br />

arithmétiques et sur le décalage. On suppose que l’opération de mémoire est OK.<br />

b) En ce qui concerne les points de couverture, nous avons avons défini des points de<br />

couverture très spécifiques pour que les couvertures croisées soient réalisées uniquement<br />

sur l'ensemble de possibilitées voulues (toutes les fonctions arithmétiques et toutes les<br />

fonctions de déplacement (« shift »). Pour ce faire, nous avons défini les points de<br />

couverture opselect_cov_arithm, opselect_cov_shift, arithm_cov et shift_opn_cov. Ces<br />

points de couverture servent à réaliser une sélection (intersect) uniquement sur ce qui est<br />

désiré : le premier pour le sélecteur d'opération arithmétique, le deuxième pour les<br />

déplacement. Ensuite, les deux suivants sont remplis pour toutes les opérations<br />

arithmétiques (ADD, ADDU, SUB, …) et le dernier pour les opérations de déplacement.<br />

Ainsi, les couvertures croisées définies arith_cov2 et shift_cov2 permettent de faire<br />

automatiquement pour la première les couvertures de toutes les opérations arithmétiques<br />

et pour la deuxième toutes les opérations de déplacement<br />

c) La couverture fonctionnelle pourrait tendre vers 100% car les limitations de a) et de b)<br />

permettent une intersection fini (e.g. -10 à 10 pour les entrées, 8 opération arithmétiques<br />

et 4 opérations de décalage). Il faut bien comprendre que cette couverture représente<br />

l'ensemble des cas spécifiques définis dans les contraintes du générateur de paquet.<br />

Page 12 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Packet pkt_sent = new(); // Packet object from Driver<br />

covergroup Arith_Cov;<br />

src1_cov: coverpoint pkt_sent.src1 {<br />

bins zero = {0};<br />

bins allfs = {32'hffffffff};<br />

bins special1 = {32'h55555555};<br />

bins special2 = {32'haaaaaaaa};<br />

bins positive = {[0:'1]} iff(pkt_sent.src1[31] == 1'b0);<br />

bins negative = {[0:'1]} iff(pkt_sent.src1[31] == 1'b1);<br />

}<br />

src2_cov: coverpoint pkt_sent.src2 {<br />

bins zero = {0};<br />

bins allfs = {32'hffffffff};<br />

bins special1 = {32'h55555555};<br />

bins special2 = {32'haaaaaaaa};<br />

bins positive = {[0:'1]} iff(pkt_sent.src2[31] == 1'b0);<br />

bins negative = {[0:'1]} iff(pkt_sent.src2[31] == 1'b1);<br />

}<br />

opselect_cov: coverpoint pkt_sent.opselect_gen {<br />

bins shift = {0};<br />

bins arith = {1};<br />

bins mem = {[4:5]};<br />

}<br />

opselect_cov_arith: coverpoint pkt_sent.opselect_gen {<br />

bins arith = {1};<br />

}<br />

opselect_cov_shift: coverpoint pkt_sent.opselect_gen {<br />

bins shift = {0};<br />

}<br />

arithm_opn_cov: coverpoint pkt_sent.operation_gen {<br />

bins arith_logic_ops = {[0:7]} iff(pkt_sent.opselect_gen==1);<br />

}<br />

shift_opn_cov: coverpoint pkt_sent.operation_gen {<br />

bins shift_ops = {[0:3]} iff(pkt_sent.opselect_gen==0);<br />

arith_cov2: cross src1_cov, src2_cov, opselect_cov_arith, arithm_opn_cov<br />

shift_cov2: cross src1_cov, src2_cov, opselect_cov_shift, shift_opn_cov<br />

}<br />

endgroup<br />

Figure 5.2 Points de couverture demandés<br />

Page 13 de 14

INF8500 Examen final Automne <strong>2009</strong><br />

Annexe<br />

Algorithme du list scheduling adapté au partitionnement logiciel/matériel<br />

Assignation du matérielle<br />

Page 14 de 14