Solution Final automne 2009 - Moodle

Solution Final automne 2009 - Moodle

Solution Final automne 2009 - Moodle

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

INF8500 Examen final Automne <strong>2009</strong><br />

Question 4 (4 points) Assertions avec System Verilog<br />

a) (1 pt) Quelle différence faites-vous entre une assertion de type assert et un point de<br />

couverture Expliquez.<br />

Les assertions permettent de détecter les comportements non-souhaitables alors que les points de<br />

couverture (couverture fonctionnelle) permettent de répertorier les comportements désirés.<br />

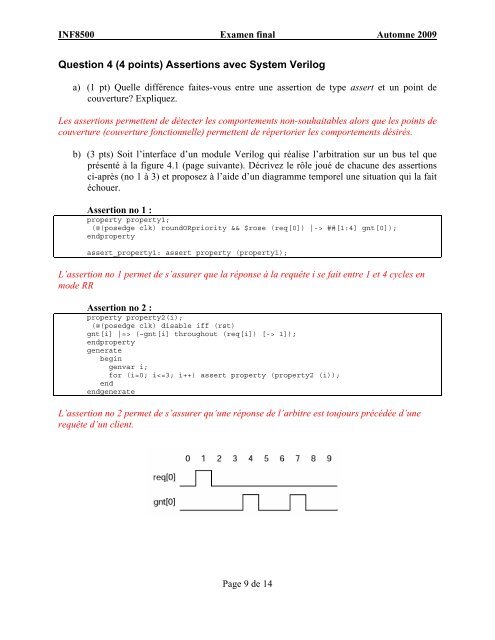

b) (3 pts) Soit l’interface d’un module Verilog qui réalise l’arbitration sur un bus tel que<br />

présenté à la figure 4.1 (page suivante). Décrivez le rôle joué de chacune des assertions<br />

ci-après (no 1 à 3) et proposez à l’aide d’un diagramme temporel une situation qui la fait<br />

échouer.<br />

Assertion no 1 :<br />

property property1;<br />

(@(posedge clk) roundORpriority && $rose (req[0]) |-> ##[1:4] gnt[0]);<br />

endproperty<br />

assert_property1: assert property (property1);<br />

L’assertion no 1 permet de s’assurer que la réponse à la requête i se fait entre 1 et 4 cycles en<br />

mode RR<br />

Assertion no 2 :<br />

property property2(i);<br />

(@(posedge clk) disable iff (rst)<br />

gnt[i] |=> (~gnt[i] throughout (req[i]) [-> 1]);<br />

endproperty<br />

generate<br />

begin<br />

genvar i;<br />

for (i=0; i