Esercizi svolti sulle reti logiche 1 - unielettronica

Esercizi svolti sulle reti logiche 1 - unielettronica

Esercizi svolti sulle reti logiche 1 - unielettronica

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

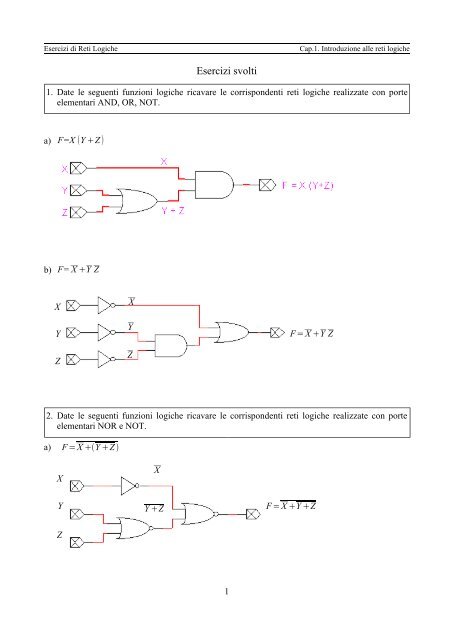

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

<strong>Esercizi</strong> <strong>svolti</strong><br />

1. Date le seguenti funzioni <strong>logiche</strong> ricavare le corrispondenti <strong>reti</strong> <strong>logiche</strong> realizzate con porte<br />

elementari AND, OR, NOT.<br />

a) F=X Y Z <br />

b) F= X Y Z<br />

X<br />

Y<br />

Z<br />

2. Date le seguenti funzioni <strong>logiche</strong> ricavare le corrispondenti <strong>reti</strong> <strong>logiche</strong> realizzate con porte<br />

elementari NOR e NOT.<br />

a) F = X Y Z <br />

X<br />

Y<br />

Z<br />

X<br />

Y<br />

Z<br />

X<br />

Y Z<br />

1<br />

F=X Y Z<br />

F = X Y Z

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

b)<br />

X<br />

Y<br />

Z<br />

F = X Y X Z<br />

3. Date le seguenti funzioni <strong>logiche</strong> ricavare le corrispondenti <strong>reti</strong> <strong>logiche</strong> realizzate con porte<br />

elementari NAND e NOT.<br />

a) F = X Y Z F=X Y Z ⇒F = X Y Z <br />

X<br />

Y<br />

Z<br />

b) F = XY XZ<br />

X<br />

Y<br />

Z<br />

X<br />

Y<br />

Z<br />

Y<br />

Z<br />

X Y<br />

X Z<br />

XY<br />

XZ<br />

2<br />

F = X Y X Z<br />

Y Z Y Z F = X Y Z <br />

F=XY XZ = XY XZ =XY XZ

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

4. Data la rete logica di figura ricavare le corrispondenti funzioni combinatorie in forma minima<br />

A<br />

B<br />

C<br />

S=C A BABC A BAB<br />

S=C A⊕BC A⊕B<br />

S= A⊕B⊕C <br />

R=ABC A BAB<br />

R=ABA BCABC<br />

R=ABABCABCA BCABC<br />

R=ABA BCABCABCABC<br />

R=ABACBC<br />

5. Dimostrare per manipolazione algebrica la proprieta' del consenso T11': .<br />

T11' :<br />

A BAB<br />

3<br />

T9, Distributiva<br />

T8, Assorbimento: AB + ABC + ABC = AB ,<br />

T6, pr. Commutativa<br />

T10', combinazione<br />

XY X Z YZ<br />

XY XZY Z= XYZ XYZ XYZ XYZ X YZ XYZ<br />

XY XZY Z= XYZ XYZ X YZ XYZ<br />

XY XZY Z= XYZ XYZ XYZ X YZ<br />

XY XZY Z=X Y XZ<br />

A B<br />

AB<br />

XY XZY Z= XY XZ<br />

C A BB A<br />

C A BAB<br />

C A BAB<br />

AB<br />

A BA B=A⊕B<br />

XY XZY Z<br />

XY XZY Z= XYZ XYZ XYZ X YZ XYZ XYZ<br />

S=C A BABC A BAB<br />

S<br />

R<br />

R=ABC A BAB<br />

A BA B=A⊕B<br />

T10'<br />

pr. della<br />

combinazione<br />

T6<br />

pr. Commutativa<br />

T3<br />

idempotenza<br />

T6<br />

pr. Commutativa<br />

T10'<br />

pr. della<br />

combinazione

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

6. Dato un segnale a 4 bit (con ultimo bit di parità) indicare la tabella di verità di una rete logica<br />

che verifichi se la parità e’ corretta e costruire la corrispondente mappa di Karnaugh.<br />

7. Full Adder: Ricavare la tabella di verità e le mappe di Karnaugh per una rete logica che<br />

effettua l'addizione ad un bit con riporto in ingresso ed in uscita.<br />

Descrizione:<br />

Mappa di Karnaugh<br />

4<br />

Tabella di verita'<br />

La somma tra numeri binari e' effettuata da <strong>reti</strong> <strong>logiche</strong> denominate half adder e full adder.<br />

Tali <strong>reti</strong> operano su parole ad 1 bit. Interconnettendo tra loro piu’ <strong>reti</strong> si ottengono circuiti logici<br />

in grado di operare con parole ad n bit.

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

Half adder (mezzo sommatore) ad un bit (effettua la somma tra due parole ad i bit)<br />

Blocco funzionale e tabella di verità' Diagramma dei tempi e mappe di Karnaugh<br />

Full adder<br />

(sommatore completo) ad un bit (effettua la somma tra due parole ad un bit, tiene<br />

conto del riporto precedente)<br />

Blocco funzionale e tabella di verità'<br />

5<br />

Diagramma dei tempi e mappe di Karnaugh

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

8. Data la rete di figura ricavare la funzione logica in forma algebrica. Semplificare la funzione<br />

combinatoria.<br />

A<br />

B<br />

C<br />

D<br />

C<br />

Y =C DBAC<br />

B<br />

Altro modo:<br />

Y =C DBAC<br />

C D<br />

Y =C DBACC DB<br />

Y =ACC DBC DB<br />

Y =ACD B<br />

Y =ACC DB<br />

Y =ACD B<br />

ACD B<br />

C<br />

A, C<br />

C<br />

A, C<br />

A<br />

A<br />

C , D B<br />

A, C, D B<br />

C<br />

A, C<br />

D B<br />

A D B<br />

A<br />

AC<br />

C D B<br />

6<br />

T8, Assorbimento aggiungo<br />

T6, pr. Commutativa<br />

T10' pr. della combinazione<br />

T6, pr. Commutativa<br />

T8''<br />

T8'''<br />

Y =C DBAC<br />

Assorbimento 2:<br />

X XY= X Y<br />

X X Y = XY<br />

C D B

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

9. Semplificare per manipolazione algebrica la seguente espressione booleana.<br />

ABCDABCDABCD<br />

AAA BACADBAB BB CBDC AC BC CC DDAD BD CDD<br />

ABCD<br />

AA BACADBABCBDC AC BCC DDAD BD CD<br />

ABCD<br />

ACDABCD<br />

AAA BACA DC AC BC CC DDAD BD CD D<br />

AA BACA DC AC BCC DDAD BD C<br />

ACD B<br />

T8, pr. Assorbimento (D)<br />

T9', pr. Distributiva<br />

T3', pr. Idempotenza<br />

7<br />

T9', pr. Distributiva<br />

T5', pr. Complementarieta'<br />

T8, pr. Assorbimento (A)<br />

T3', pr. Idempotenza<br />

T8, pr. Assorbimento C <br />

Forma minima !!<br />

T5', pr. Complementarieta'<br />

T8, pr. Assorbimento (A)<br />

T8, pr. Assorbimento C

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

10.Verificare che le seguenti espressioni risultano duali:<br />

a) NOR e NAND<br />

b) EXOR e EXNOR<br />

NOR e NAND Y =AB ⇒ Y'=AB<br />

EXOR e EXNOR<br />

Principio di dualità<br />

Y =A⊕B=ABA B ⇒ Y'= ABAB=AAA BBAB B<br />

Y'=A BAB=A⊙B<br />

11.Ricavare la funzione logica in forma algebrica e semplificare applicando i teoremi dell'algebra<br />

booleana.<br />

A<br />

B<br />

C<br />

C<br />

B<br />

B<br />

A<br />

A<br />

AC<br />

AB<br />

BCBC<br />

Y = ACABBCB CABA B<br />

Y = ACABBCB CABA B<br />

Y = AC AB BCB C ABA B<br />

Y = AC AB BCB C ABA B<br />

ACAB<br />

ABA B BCBCABA B<br />

Y = AC ABBC BC AB A B<br />

Y = AC ABBC BC ABAB<br />

Y =A AA BC AC B BC BC ABAB<br />

Y =A BC AC B BC BC ABAB<br />

Y =A BC AC B BBBCC BCC AAABBABB<br />

8<br />

Y = ACABBCBCABA B

<strong>Esercizi</strong> di Reti Logiche Cap.1. Introduzione alle <strong>reti</strong> <strong>logiche</strong><br />

Y =A BC AC B BCC BABBA<br />

Y =A BC AC BBC ABBC BAC BABC BBA<br />

Y =A BC AC BABBCA BCABCABBC<br />

Y =A BC AC BA BCABC<br />

Y =A BC AC BABC<br />

Y =A BACB C C B<br />

Y =A BACBC B<br />

Y =A BACABC B<br />

Y =A BACBCAB<br />

Y =A BACAB<br />

Y =A BABAC<br />

Y =A⊕BAC<br />

T8''<br />

T8'''<br />

T11', consenso :<br />

Forma minima<br />

9<br />

Assorbimento 2:<br />

X XY= X Y<br />

X X Y = XY<br />

XY XZYZ = XY XZ