Multiplicador Binário com Sinal - PCS - USP

Multiplicador Binário com Sinal - PCS - USP

Multiplicador Binário com Sinal - PCS - USP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

RESUMO<br />

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

Nesta experiência será implementado circuito para multiplicação binária <strong>com</strong> sinal. Deve ser aplicada a<br />

metodologia para projeto estruturado de sistemas digitais apresentada em experiências anteriores. A<br />

parte experimental será desenvolvida <strong>com</strong> o auxílio da ferramenta de software Quartus II da Altera e<br />

depois implementada <strong>com</strong> o dispositivo lógico Altera EPM7128SLC84-7.<br />

1. PARTE TEÓRICA<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong><br />

1.1. Revisão sobre Multiplicação Binária<br />

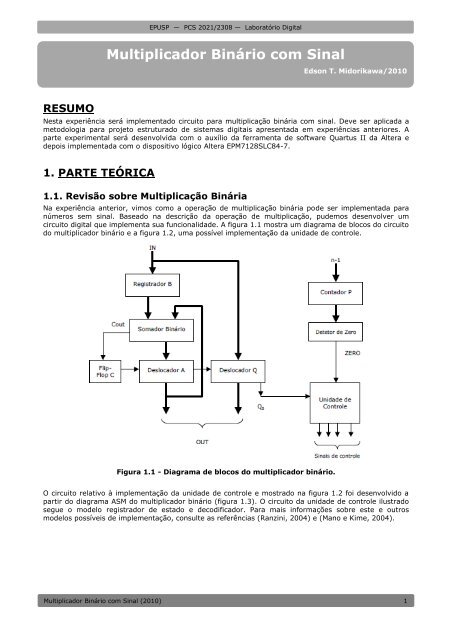

Na experiência anterior, vimos <strong>com</strong>o a operação de multiplicação binária pode ser implementada para<br />

números sem sinal. Baseado na descrição da operação de multiplicação, pudemos desenvolver um<br />

circuito digital que implementa sua funcionalidade. A figura 1.1 mostra um diagrama de blocos do circuito<br />

do multiplicador binário e a figura 1.2, uma possível implementação da unidade de controle.<br />

Figura 1.1 - Diagrama de blocos do multiplicador binário.<br />

Edson T. Midorikawa/2010<br />

O circuito relativo à implementação da unidade de controle e mostrado na figura 1.2 foi desenvolvido a<br />

partir do diagrama ASM do multiplicador binário (figura 1.3). O circuito da unidade de controle ilustrado<br />

segue o modelo registrador de estado e decodificador. Para mais informações sobre este e outros<br />

modelos possíveis de implementação, consulte as referências (Ranzini, 2004) e (Mano e Kime, 2004).<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 1

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

Figura 1.2 - Uma implementação da unidade de controle do multiplicador binário.<br />

A unidade de controle do multiplicador binário tem 3 estados (PARADO, MUL0 e MUL1), e gera sinais de<br />

controle para o fluxo de dados para acionar seus <strong>com</strong>ponentes (registradores deslocadores A e Q, flipflop<br />

C e contador P)<br />

Figura 1.3 - Diagrama ASM da unidade de controle do multiplicador binário.<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 2

1.2. Multiplicação Binária <strong>com</strong> <strong>Sinal</strong><br />

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

Quando consideramos números <strong>com</strong> sinal, o algoritmo usado na experiência anterior não pode ser<br />

aplicado. Considere a multiplicação de 11 (1011 2) <strong>com</strong> 13 (1101 2), onde obtemos o resultado 143<br />

(10001111 2). Se considerarmos estes valores binários <strong>com</strong>o números em <strong>com</strong>plemento de dois, teríamos<br />

a multiplicação de -5 (1011 2) <strong>com</strong> -3 (1101 2) resultando em -113 (10001111 2), que é um valor diferente<br />

de 15 (00001111 2). Para mais detalhes consulte (Stallings, 2002).<br />

Uma forma de levar em consideração o sinal dos operandos na operação de multiplicação binária é usar o<br />

algoritmo de Booth. A figura 1.4 mostra fluxograma para o algoritmo de Booth.<br />

A A – M<br />

= 10<br />

NÃO<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 3<br />

INÍCIO<br />

A 0, Q -1 0<br />

M multiplicando<br />

Q multiplicador<br />

Contador n<br />

Q 0,Q -1<br />

Deslocamento aritmético<br />

para a direita de A,Q,Q -1<br />

Contador Contador -1<br />

Contador<br />

= 0?<br />

= 00<br />

= 11<br />

= 01<br />

SIM<br />

Figura 1.4 – Fluxograma do algoritmo de Booth.<br />

A A + M<br />

Convém apontar alguns aspectos a serem considerados no projeto do fluxo de dados do multiplicador<br />

binário <strong>com</strong> sinal:<br />

• presença do bloco somador/subtrator;<br />

• presença do flip-flop F à direita do multiplicador para armazenar Q -1;<br />

• o deslocamento do acumulador deve ser aritmético (o que isto significa e o que muda no circuito<br />

em relação ao multiplicador sem sinal?);<br />

• a decisão de soma ou subtração depende do bit menos significativo do multiplicador (Q 0) e do<br />

flip-flop F (Q -1). Estes sinais de estado são enviados à unidade de controle;<br />

• a unidade de controle é bem parecida <strong>com</strong> a do multiplicador binário de números sem sinal.<br />

FIM

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

A figura 1.5 mostra o diagrama de blocos básico do multiplicador binário <strong>com</strong> sinal. O flip-flop F mantém<br />

o dado que é identificado <strong>com</strong>o Q -1 no fluxograma da figura 1.4.<br />

registra_M<br />

desloca<br />

desloca<br />

registra_Q<br />

registra_A<br />

soma/subtrai<br />

IN<br />

Multiplicando<br />

M<br />

Somador / Subtrador<br />

Acumulador<br />

A<br />

OUT<br />

<strong>Multiplicador</strong><br />

Q<br />

Flip-<br />

Flop F<br />

Figura 1.5 – Diagrama de blocos básico do multiplicador binário <strong>com</strong> sinal.<br />

Algumas dicas sobre o projeto do <strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong>:<br />

Contador P<br />

Detetor de Zero<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 4<br />

Q 0<br />

Q -1<br />

n<br />

Unidade de<br />

Controle<br />

...<br />

Sinais de controle<br />

1) o bloco somador/subtrador pode ser facilmente projetado <strong>com</strong> um somador binário e portas OU<br />

EXCLUSIVO (XOR). O sinal que indica a operação (0=soma, 1=subtração) é conectado em uma das<br />

entrada das portas e também na entrada de vem-um do somador binário;<br />

2) O sinal acima para soma ou subtração pode vir direto do bit menos significativo do registrador Q<br />

(sinal Q 0): quando Q 0=0, deve ocorrer uma soma, e quando Q 0=1, uma subtração.<br />

3) Na unidade de controle do multiplicador binário sem sinal, era realizada a soma somente se o sinal<br />

Q 0 fosse igual a 1. Caso contrário, havia somente o deslocamento dos registradores. Na unidade de<br />

controle do multiplicador binário <strong>com</strong> sinal, se Q 0≠F (ou seja, Q 0F=1) ocorre a soma ou subtração,<br />

dependendo do valor de Q 0, e depois o deslocamento dos registradores. Caso Q 0=F (ou seja,<br />

Q 0F=0), deve ocorrer somente o deslocamento. Deste modo, acredito que a unidade de controle<br />

não deve ser mudada quanto a este aspecto.<br />

4) Para mais informações sobre a metodologia de projeto a ser considerada consulte referência (Ranzini<br />

et al, 2002).<br />

ZERO

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

1.3. Exemplos do Algoritmo de Booth<br />

Ilustramos aqui vários exemplos de multiplicação binária para números em <strong>com</strong>plemento de dois <strong>com</strong><br />

representação binária de 4 bits. Sejam os números: 6 = 0110 e -6 = 1010.<br />

Nos exemplos abaixo, a legenda das tabelas indicam:<br />

acum. = acumulador A<br />

mult. = multiplicador Q<br />

F = flip-flop a direita do multiplicador (Q -1)<br />

a) –6 x 6<br />

b) 6 x -6<br />

PASSO ACUM. MULT. F. Condição (Q 0,F) -> Ação<br />

0<br />

1<br />

2<br />

3<br />

0000 0110 0 00 -> não faz nada<br />

0000 0011 0 shift aritmético<br />

0000 0011 0<br />

-1010<br />

0110 0011 0<br />

10 -> subtrai<br />

0011 0001 1 shift aritmético<br />

0011 0001 1 11-> não faz nada<br />

0001 1000 1 shift aritmético<br />

0001 1000 1<br />

+1010<br />

1011 1000 1<br />

01 -> soma<br />

1101 1100 0 shift aritmético<br />

fim 1101 1100 resultado = -36<br />

PASSO ACUM. MULT. F. Condição (Q 0,F) -> Ação<br />

0<br />

1<br />

2<br />

3<br />

0000 1010 0 00 -> não faz nada<br />

0000 0101 0 shift aritmético<br />

0000 0101 0<br />

-0110<br />

1010 0101 0<br />

10 -> subtrai<br />

1101 0010 1 shift aritmético<br />

1101 0010 1<br />

+0110<br />

0011 0010 1<br />

01 -> soma<br />

0001 1001 0 shift aritmético<br />

0001 1001 0<br />

-0110<br />

1011 1001 0<br />

10-> subtrai<br />

1011 1100 1 shift aritmético<br />

fim 1011 1100 resultado = -36<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 5

c) 6 x 6<br />

d) -6 x -6<br />

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

PASSO ACUM. MULT. F. Condição (Q 0,F) -> Ação<br />

0<br />

1<br />

2<br />

3<br />

0000 0110 0 00 -> não faz nada<br />

0000 0011 0 shift aritmético<br />

0000 0011 0<br />

-0110<br />

1010 0011 0<br />

10 -> subtrai<br />

1101 0001 1 shift aritmético<br />

1101 0001 1 11-> não faz nada<br />

1110 1000 1 shift aritmético<br />

1110 1000 1<br />

+0110<br />

0100 1000 1<br />

01 -> soma<br />

0010 0100 0 shift aritmético<br />

fim 0010 0100 resultado = 36<br />

PASSO ACUM. MULT. F. Condição (Q 0,F) -> Ação<br />

0<br />

1<br />

2<br />

3<br />

0000 1010 0 00 -> não faz nada<br />

0000 0101 0 shift aritmético<br />

0000 0101 0<br />

-1010<br />

0110 0101 0<br />

10 -> subtrai<br />

0011 0010 1 shift aritmético<br />

0011 0010 1<br />

+1010<br />

1101 0010 1<br />

01 -> soma<br />

1110 1001 0 shift aritmético<br />

1110 1001 0<br />

-1010<br />

0100 1001 1<br />

10-> subtrai<br />

0010 0100 1 shift aritmético<br />

fim 0010 0100 resultado = 36<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 6

2. PARTE EXPERIMENTAL<br />

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

Nesta experiência será desenvolvido um circuito baseado no multiplicador binário desenvolvido na<br />

experiência anterior. O projeto pode ser feito usando os <strong>com</strong>ponentes discretos básicos MSI e SSI ou<br />

<strong>com</strong> a linguagem VHDL.<br />

2.1. Especificação do <strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong><br />

O circuito <strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (MBcS) é responsável pela realização de uma multiplicação de<br />

dois números binários <strong>com</strong> sinal de 4 bits, introduzidos separadamente no circuito através de uma única<br />

via de dados (CH0 a CH3). A operação é iniciada <strong>com</strong> o acionamento do sinal INICIAR (botão B1), e o<br />

resultado da operação <strong>com</strong> 8 bits (OUT) deve ser conectado a dois displays de saída. Os operandos da<br />

multiplicação são especificados para o MBcS pelos sinais ENTRA_MULTIPLICANDO (CH6) e<br />

ENTRA_MULTIPLICADOR (CH7). O sinal PRONTO indica o final da multiplicação.<br />

Os sinais de entrada e saída do <strong>Multiplicador</strong> <strong>Binário</strong> são os seguintes:<br />

• IN - via de dados de entrada, <strong>com</strong> quatro bits;<br />

• INICIAR - sinal de controle utilizado iniciar a multiplicação;<br />

• ENTRA_MULTIPLICANDO - especifica o multiplicando da operação;<br />

• ENTRA_MULTIPLICADOR - especifica o multiplicador da operação;<br />

• OUT - via de dados de saída, <strong>com</strong> oito bits;<br />

• PRONTO – indica final da operação.<br />

A figura 2.1 abaixo mostra o MBcS <strong>com</strong> os sinais descritos anteriormente:<br />

INICIAR<br />

ENTRA_MULTIPLICANDO<br />

ENTRA_MULTIPLICADOR<br />

IN[3:0]<br />

Figura 2.1 – Sinais de entrada e de saída do <strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong><br />

a ser desenvolvido.<br />

A operação do circuito deve seguir os seguintes passos:<br />

1. Acertar um valor binário na vida de dados de entrada (IN);<br />

2. Ativar o sinal ENTRA_MULTIPLICANDO;<br />

3. Colocar outro valor na via de dados de entrada;<br />

4. Ativar o sinal ENTRA_MULTIPLICADOR;<br />

MBcS<br />

5. Acionar o botão INICIAR para a execução da multiplicação binária;<br />

6. Verificar resultado na via de dados de saída (OUT, PRONTO).<br />

OUT[7:0]<br />

PRONTO<br />

Caso se deseje repetir um valor anteriormente ajustado no circuito MBcS, os passos 1 e 2 ou os passos 3<br />

e 4 podem ser ignorados, visto que um registrador interno deve manter os valores do multiplicador e do<br />

multiplicando da operação anterior.<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 7

DICAS:<br />

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

1. Para auxiliar a depuração do circuito do MBcS, determine alguns sinais internos do circuito projetado<br />

para serem monitorados durante os testes e depuração do circuito. Estes sinais devem ser ligados<br />

nos leds disponíveis no painel de montagens.<br />

2. Apresentar o diagrama ASM do circuito do MBcS, explicando os sinais de estado e de controle usados.<br />

3. A depuração da máquina de estados da unidade de controle pode ser feita <strong>com</strong> uma indicação (sinal<br />

externo) do estado atual do circuito.<br />

4. O fluxo de dados do projeto deve armazenar tanto o multiplicando <strong>com</strong>o o multiplicador para<br />

poderem ser reaproveitados entre multiplicações consecutivas. Que alterações devem ser feitas no<br />

fluxo de dados apresentado na figura 1.5?<br />

5. Trazer o arquivo do projeto para o Laboratório Digital (bdf ou vhd).<br />

2.2. Montagem e Depuração<br />

a) O projeto do MBcS deve ser programado na pastilha da placa MAX7-<strong>PCS</strong> e os sinais de entrada e<br />

saída devem ser conectados no painel de montagens experimentais (botões, chaves, leds e displays).<br />

b) Execute testes iniciais do circuito usando os casos de teste dos exemplos da seção 1.3.<br />

2.3. Avaliação<br />

a) Elabore uma tabela contendo todos os códigos binários de 4 bits em <strong>com</strong>plemento de dois e o seu<br />

respectivo valor equivalente. Por exemplo, o código ―0001‖ é a representação do valor ―+1‖ e ―1111‖<br />

é a representação do valor ―-1‖.<br />

b) Escolha mais casos de teste para avaliar o correto funcionamento do MBcS.<br />

c) Execute os casos de teste escolhidos e avalie os resultados.<br />

Perguntas<br />

1. Explique a diferença entre deslocamento e deslocamento aritmético. Exemplifique.<br />

2. Como é implementado o deslocamento aritmético no fluxo de dados?<br />

3. Decreva detalhadamente o funcionamento e a implementação da unidade de controle do MBcS.<br />

4. Que fatores influenciaram na escolha do grupo no projeto do MBcS (<strong>com</strong>ponentes discretos ou<br />

VHDL)? Que vantagens e desvantagens vocês poderiam ressaltar para cada alternativa?<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 8

3. BIBLIOGRAFIA<br />

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<br />

1. MANO, M. M.; KIME, C. R. Logic and <strong>com</strong>puter design fundamentals. 3 rd edition, New Jersey:<br />

Prentice-Hall, 2004.<br />

2. MIDORIKAWA, E.T. Lógica programável II. Apostila de Laboratório Digital. Escola Politécnica da<br />

<strong>USP</strong>, 2004.<br />

3. PARHAMI, B. Computer arithmetic: algorithms and hardware designs. Oxford: Oxford University<br />

Press, 2000.<br />

4. PATTERSON, D. A. & HENNESSY, J. L. Computer organization and design: the hardware/<br />

software interface. 2nd edition, San Francisco: Morgan Kaufmann, 1998.<br />

5. RANZINI, E.; HORTA, E. L. Lógica programável. Apostila de Laboratório Digital. Escola Politécnica<br />

da <strong>USP</strong>, 2000.<br />

6. RANZINI, E.; HORTA, E. L.; MIDORIKAWA, E. T. Projeto de circuitos <strong>com</strong> MAX+PLUS II. Apostila<br />

de Laboratório Digital. Escola Politécnica da <strong>USP</strong>, 2002.<br />

7. RANZINI, E. Exemplo 1 de projeto de circuito síncrono: multiplicador binário. Resumo da<br />

disciplina <strong>PCS</strong>2304 - Projeto Lógico Digital. Escola Politécnica da <strong>USP</strong>, 2004.<br />

8. STALLINGS, W. Arquitetura e organização de <strong>com</strong>putadores. 5ª edição, Prentice-Hall, 2002.<br />

4. EQUIPAMENTOS NECESSÁRIOS<br />

1 fonte de alimentação fixa, 5V 5%, 4A.<br />

1 osciloscópio digital.<br />

1 multímetro digital.<br />

1 gerador de pulsos.<br />

1 painel de montagens experimentais.<br />

1 placa MAX7-<strong>PCS</strong>, <strong>com</strong> cabo para interface paralela.<br />

1 <strong>com</strong>putador PC <strong>com</strong> programa Altera Quartus II.<br />

Histórico de Revisões<br />

E.T.M./2004 – primeira versão da experiência.<br />

E.T.M./2010 – revisão geral e atualização do texto.<br />

<strong>Multiplicador</strong> <strong>Binário</strong> <strong>com</strong> <strong>Sinal</strong> (2010) 9