Laboration 2

Laboration 2

Laboration 2

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Laboration</strong> 2<br />

I den förenklade prestandamodellen har vi inte tagit hänsyn till inverkan av cacheorganisationen på hit-ratio och<br />

accesstid. I själva verket beror hit-ratio på cacheorganisationen och programbeteendet, P. H är således en funktion<br />

av dessa, dvs H = H( O, P ). Vidare gäller att accesstiden för cachen beror av cacheorganisationen, dvs<br />

A 1 = A 1 ( O ). Eftersom det inte finns något icke-trivialt analytiskt uttryck för dessa funktioner, är enda sättet att via<br />

experiment studera inverkan av cacheorganisationen och programbeteendet på dessa.<br />

Låt oss nu studera hur hit-ratio varierar i tiden under det att ett program exekveras.<br />

Uppgift 2.8<br />

Starta simulatorn med programmet example1. Välj en direktavbildande cache med 64 ord och 2 ord/block. Exekvera<br />

programmet i full fart (med Go ). Tag därefter upp show-menyn (mittersta musknappen) och välj alternativet<br />

Show Hitgraph, All. Efter en stund kommer ett diagram upp. I diagrammet ser man hur hit-ratio varierar<br />

med tiden. Tag även upp lokalitetsgrafen för instruktionsreferenser.<br />

Förklara varför hit-ratio till en början är mycket låg<br />

Svar: _____________________________________________________________________________________<br />

_________________________________________________________________________________________<br />

Vad beror variationerna i hit-ratio i mitten av grafen på<br />

Svar: _____________________________________________________________________________________<br />

Varför sjunker hit-ratio i slutet Ledning: Studera programlistan<br />

Svar: _____________________________________________________________________________________<br />

———————————————————————————————————— Slut på uppgift 2.8<br />

Cachestorlekens inverkan på hit-ratio<br />

Vi skall nu studera cachestorlekens inverkan på hit-ratio.<br />

Uppgift 2.9<br />

Ändra cachens organisation enligt följande. Välj en direktavbildande cache på 16 ord som utnyttjar write-through<br />

och med blockstorleken 1 ord.<br />

Vi skall bara studera instruktionsreferenser. Vi väljer därför en cache som endast cachar instruktioner. Välj därför<br />

Cache Type = Instr. cache i samma meny som du väljer övriga cache parametrar.<br />

Exekvera programmet i full fart. Tag därefter upp Show result och fyll i uppgifterna i tabellen nedan. Gör om samma<br />

mätningar för de cachestorlekar som finns upptagna i tabellen. Se hela tiden till att du har en direkt-avbildande<br />

cache. Rita in mätpunkterna i diagrammet och besvara därefter frågorna nedan.<br />

S (cachestorlek) H (total hit-ratio)<br />

16<br />

32<br />

64<br />

128<br />

15<br />

<strong>Laboration</strong> 2<br />

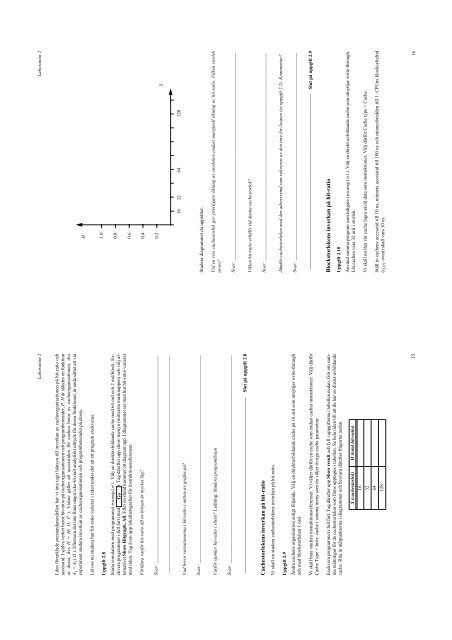

H<br />

1.0<br />

0.8<br />

0.6<br />

0.4<br />

0.2<br />

S<br />

16 32 64 128<br />

Studera diagrammet du upprättat.<br />

Vid en viss cachestorlek ger ytterligare ökning av storleken endast marginell ökning av hit-ratio. Vilken storlek<br />

avses<br />

Svar: _____________________________________________________________________________________<br />

Vilken hit-ratio erhålls vid denna cachestorlek<br />

Svar: _____________________________________________________________________________________<br />

Jämför cachestorleken med den adressrymd som refereras av den inre for-loopen (se uppgift 2.2). Kommentar<br />

Svar: _____________________________________________________________________________________<br />

———————————————————————————————————— Slut på uppgift 2.9<br />

Blockstorlekens inverkan på hit-ratio<br />

Uppgift 2.10<br />

Använd samma program som tidigare (example1). Välj en direkt-avbildande cache som utnyttjar write-through.<br />

Låt cachen vara 32 ord i storlek.<br />

Vi skall nu låta vår cache lagra såväl data som instruktioner. Välj därför Cache type = Cache.<br />

Ställ in cachens accesstid till 10 ns, minnets accesstid till 100 ns och minnesbredden till 1. CPUns klockcykeltid<br />

(t CPU ovan) skall vara 10 ns.<br />

16