Technika cyfrowa

Technika cyfrowa

Technika cyfrowa

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Technika</strong> <strong>cyfrowa</strong><br />

Tadeusz Łuba<br />

Gmach Elektroniki<br />

Nowowiejska 15/19<br />

pok. 472<br />

luba@tele.pw.edu.pl<br />

zpt2.tele.pw.edu.pl

Organizacja<br />

Wykład<br />

Tadeusz Łuba<br />

Laboratorium<br />

dr Paweł Tomaszewicz<br />

dr Grzegorz Borowik

Egzamin...<br />

LAB 40 pkt.<br />

Egzamin 60 pkt<br />

(w tym kolo za 20pkt)<br />

Oceny tradycyjnie

1. Ashar P., Devadas S., Newton A. R.: Sequential logic synthesis,<br />

Kluwer Academic<br />

2. Minimization Algorithms for VLSI Synthesis, Kluwer Academic<br />

Publishers, Boston, 1984.<br />

3. Brown F. M.: Boolean Reasoning. The Logic of Boolean Equation,<br />

Kluwer Academic Publishers, 1990.<br />

4. Brzozowski J. A, Seger C-J.: Asynchronous Circuits, Springer Verlag,<br />

New York 1995.<br />

5. Brzozowski J., Łuba T.: Decomposition of Boolean Functions Specified<br />

by Cubes. Journal of Multiple-Valued Logic and Soft Computing.<br />

Vol. 9, pp. 377–417. Old City Publishing, Inc., Philadelphia 2003.<br />

6. De Micheli G.: Synthesis and Optimization of Digital Circuits. McGraw-Hill,<br />

New York, 1994. Również tłumaczenie polskie: Synteza i optymalizacja<br />

układów cyfrowych. WNT, Warszawa Łuba 1998. T.(red.),<br />

7. Devadas, S., Ghosh, A., and Keutzer, K. Logic Synthesis. McGraw-Hill,<br />

New York, 1994.<br />

8. Gajski D.D.: Principles of digital design.<br />

Zbierzchowski<br />

Prentice-Hall International,<br />

B.:<br />

New jersey 1997.<br />

9. Hassoun S., Sasao T., Brayton R. (ed.): Logic Synthesis and Verification.<br />

Kluwer Academic Publishers, New York 2002.<br />

10. Iman S., Pedram M.: Logic Synthesis for Low Power VLSI Design, Kluwer<br />

Academic Publishers, 1999.<br />

11. Kamionka-Mikuła H., Małysiak H., Pochopień B.: Układy cyfrowe. Teoria<br />

i przykłady. Wyd. Pracowni Komputerowej Jacka Skalmierskiego.<br />

Gliwice 2003.<br />

12. Kania D.: Synteza logiczna przeznaczona dla matrycowych struktur<br />

programowalnych typu PAL. Politechnika Śląska. Zeszyty Naukowe.<br />

Nr 1619. Gliwice 2004.<br />

13. Katz R. H.: Contemporary logic design. The Benjamin/Cummings<br />

Publishing Company, Inc., Redwood City, 1994<br />

14. Kohavi Z.: Switching and Finite Automata Theory. Mc-Graw-Hill,<br />

New York, 1978.<br />

15. Kuźmicz W.: Układy ASIC w polskich realiach. Przegląd Telekomunikacyjny<br />

i Wiadomości Telekomunikacyjne, nr 8, pp. 457-460, 1995.<br />

16. Lala P.K.: Practical digital logic design and testing. Prentice-Hall,<br />

New Jersey 1996.<br />

17. Łuba T.(red.), Rawski M., Tomaszewicz P., Zbierzchowski B.: Synteza<br />

układów cyfrowych. WKŁ Warszawa 2003.<br />

18. Łuba T., Zbierzchowski B., Zbysiński P.: Układy reprogramowalne dla<br />

potrzeb telekomunikacji cyfrowej. Przegląd Telekomunikacyjny<br />

i Wiadomości Telekomunikacyjne, nr 5, 2002.<br />

Literatura<br />

Rawski M., Tomaszewicz P.,<br />

Programowalne układy<br />

przetwarzania sygnałów<br />

cyfrowych i informacji<br />

WKŁ Warszawa 2008<br />

19. Łuba T.: Synteza układów logicznych. Wyższa Szkoła Informatyki<br />

Stosowanej i Zarządzania, Wyd. 2, Warszawa 2001.<br />

20. Łuba T.: Rola i znaczenie syntezy logicznej w technice cyfrowej<br />

układów programowalnych. Elektronika, str. 15 ¸ 19, nr 7-8, 2002.<br />

21. Łuba T., Jasiński K., Zbierzchowski B.: Programowalne układy<br />

przetwarzania sygnałów i informacji - technika <strong>cyfrowa</strong><br />

w multimediach i kryptografii, Przegląd Telekomunikacyjny i Wiadomości<br />

Telekomunikacyjne, str. 408-418, nr 8-9, 2003.<br />

22. Majewski W., Albicki A.: Algebraiczna teoria automatów. WNT,<br />

Warszawa 1980.<br />

23. Mikołajczak B.: Algebraiczna i strukturalna teoria automatów. PWN,<br />

Warszawa – Łódź 1985.<br />

24. Mulawka J.: Systemy ekspertowe. WNT, Warszawa 1996.<br />

25. Mrózek A., Płonka L.: Analiza danych metodą zbiorów<br />

przybliżonych. Zastosowania w ekonomii, medycynie i sterowaniu.<br />

Akademicka Oficyna Wydawnicza PLJ, Warszawa 1999.<br />

26. McCluskey E. J.: Logic design principles, with emphasis on testable<br />

semicustom circuits. Prentice-hall International, Inc., New Jersey<br />

1986.<br />

27. Pawlak Z.:Rough Sets. Theoretical Aspects of Reasoning about<br />

Data, Kluwer Academic Publishers, 1999.<br />

28. Roth C. H.: Fundamentals of Logic Design. West Publ. CO., 1985.<br />

29. Salsic Z., Smailagic A.: Digital systems design and prototyping<br />

using field programmable logic. Kluwer Academic Publishers, 1997.<br />

30. Sasao T.: Switching Theory for Logic Synthesis, Kluwer Academic<br />

Publishers, 1999.<br />

31. Sasao T.: Logic Synthesis and Optimization. Kluwer Academic<br />

Publishers,1993.<br />

32. Słowiński R.(ed.): Intelligent Decision Support - Handbook of<br />

Applications and Advances of the Rough Sets Theory, Kluwer<br />

Academic Publishers, Dordrecht 1992.<br />

33. Scholl C.: Functional Decomposition with Application to FPGA<br />

Synthesis. Kluwer Academic Publisher, Boston 2001.<br />

34. Tyszer J.: Układy cyfrowe. Materiały pomocnicze do wykładów.<br />

Wyd. Politechniki Poznańskiej. Poznań 2000.<br />

35. Zieliński C.: Podstawy projektowania układów cyfrowych. PWN,<br />

Warszawa 2003.<br />

36. Zbysiński P., Pasierbiński J.: Układy programowalne – pierwsze<br />

kroki. Wyd. II, Wydawnictwo BTC. Warszawa 2004.<br />

4

Literatura<br />

5

<strong>Technika</strong> <strong>cyfrowa</strong> znalazła<br />

szczególne zastosowanie w układach<br />

cyfrowego przetwarzania informacji i<br />

sygnałów<br />

,89484,3,90031472,9.0<br />

474230<br />

8

. . . Rok 1958 . . .<br />

Jack Kilby z Texas Instruments zbudował pierwszy układ scalony …<br />

… za co otrzymał Nagrodę Nobla z fizyki w 2000.<br />

<br />

Pierwsze układy scalone zawierały mniej niż 20 tranzystorów.<br />

9

. . . 2011<br />

miliony bramek logicznych<br />

ASIC<br />

Nowa jakość…<br />

10

Nową jakością układów scalonych,<br />

o przełomowym znaczeniu dla techniki<br />

cyfrowej jest technologia programowalnych<br />

modułów logicznych, których konstrukcja<br />

jest bardzo prosta z ideowego punktu<br />

widzenia, ale jest to nowa jakość z punktu<br />

widzenia – niemożliwego do tej pory –<br />

programowania połączeń.<br />

11

Programowalne moduły y logiczne<br />

(Programmable Logic Devices)<br />

to układy scalone, których właściwości<br />

funkcjonalne są definiowane nie przez<br />

producenta, lecz przez końcowego<br />

użytkownika. Najważniejsza cechą tych<br />

układów jest możliwość nadawania im (przez<br />

programowanie) określonych przez<br />

użytkownika cech funkcjonalnych, w jego<br />

laboratorium czy na biurku, a nie w fabryce.<br />

PLD<br />

PLD<br />

12

Układy FPGA<br />

(Field Programmable Gate Array)<br />

Configurable Logic Block (CLB)<br />

Logic Element (LE)<br />

DATA IN<br />

LOGI C<br />

VARIABLES<br />

.di<br />

.a<br />

.b<br />

.c<br />

.d<br />

.e<br />

QX<br />

F<br />

CO MB INATIONAL<br />

FUNCTION<br />

G<br />

QY<br />

F<br />

DIN<br />

G<br />

F<br />

DIN<br />

G<br />

0<br />

MUX<br />

1<br />

0<br />

MUX<br />

1<br />

D Q<br />

RD<br />

D Q<br />

QX<br />

F<br />

G<br />

QY<br />

.X<br />

CLB<br />

OUTPUTS<br />

.Y<br />

ENABLE<br />

clk<br />

clk<br />

RESET<br />

.e c<br />

"1" (ENABLE)<br />

.k<br />

.rd<br />

"0 " (I NH IB IT)<br />

RD<br />

(GLOBAL RESET)<br />

Reprogramowania i<br />

rekonfiguracji<br />

13

Układy programowalne wyrównuj<br />

wnują szanse…<br />

14

Układ kryptograficzny<br />

PLD<br />

ASIC<br />

F@*q~<br />

PLD<br />

15

Komputerowe systemy projektowania<br />

Ze względu na skomplikowaną budowę struktur<br />

programowalnych ich realizacja nie może e się odbywać bez…<br />

GAL<br />

PAL<br />

FPGA<br />

FLEX<br />

EPLD<br />

16

Komputerowe projektowanie…<br />

Języki opisu sprzętu<br />

tu…<br />

Specyfikacja HDL<br />

Synteza funkcjonalna<br />

Synteza logiczna<br />

Hardware Description<br />

Language (HDL):<br />

VHDL<br />

VERILOG<br />

SystemC<br />

Odwzorowanie<br />

technologiczne<br />

FPGA<br />

17

Edytor tekstowy<br />

18

Przetwarzanie projektu - kompilator<br />

19

Programowanie<br />

20

Przełomowe znaczenie układów<br />

programowalnych wynika również<br />

z faktu, że otworzyły one drogę do<br />

stosowania nowych, niezwykle<br />

skutecznych procedur syntezy<br />

logicznej<br />

21

Przykład – prosty układ<br />

x 1<br />

x 2<br />

x 3<br />

x 10<br />

kombinacyjny<br />

Układ kombinacyjny<br />

UK<br />

y<br />

.type fr<br />

.i 10<br />

.o 1<br />

.p 25<br />

0010111010 0<br />

1010010100 0<br />

0100011110 0<br />

1011101011 0<br />

1100010011 0<br />

0100010110 0<br />

1110100110 0<br />

0100110000 0<br />

0101000010 0<br />

0111111011 1<br />

0000010100 1<br />

1101110011 1<br />

0100100000 1<br />

0100011111 1<br />

0010000110 1<br />

1111010001 1<br />

1111101001 1<br />

1111111111 1<br />

0010000000 1<br />

1101100111 1<br />

0010001111 1<br />

1111100010 1<br />

1010111101 1<br />

0110000110 1<br />

0100111000 1<br />

.e<br />

22

LIBRARY ieee;<br />

USE ieee.std_logic_1164.ALL;<br />

ENTITY tl27 IS<br />

PORT (<br />

in: IN STD_LOGIC_VECTOR(9<br />

DOWNTO 0);<br />

out: OUT STD_LOGIC_VECTOR(0<br />

DOWNTO 0)<br />

);<br />

END tl27;<br />

Realizacja funkcji F<br />

w systemie Quartus<br />

ARCHITECTURE tl27_arch OF tl27 IS<br />

BEGIN<br />

pandor: PROCESS (in)<br />

BEGIN<br />

CASE in IS<br />

WHEN "0010111010" => out out out out out out out out out out out out out out out out out out out out out out out out out out

LIBRARY ieee;<br />

USE ieee.std_logic_1164.ALL;<br />

ENTITY tl27 IS<br />

PORT (<br />

in: IN STD_LOGIC_VECTOR(9<br />

DOWNTO 0);<br />

out: OUT STD_LOGIC_VECTOR(0<br />

DOWNTO 0)<br />

);<br />

END tl27;<br />

Realizacja funkcji F<br />

w systemie Quartus<br />

ARCHITECTURE tl27_arch OF tl27 IS<br />

BEGIN<br />

pandor: PROCESS (in)<br />

BEGIN<br />

CASE in IS<br />

WHEN "0010111010" => out out out out out out out out out out out out out out out out out out out out out out out out out out

LIBRARY ieee;<br />

USE ieee.std_logic_1164.ALL;<br />

ENTITY tl27 IS<br />

PORT (<br />

in: IN STD_LOGIC_VECTOR(9<br />

DOWNTO 0);<br />

out: OUT STD_LOGIC_VECTOR(0<br />

DOWNTO 0)<br />

);<br />

END tl27;<br />

Ciekawe jak zachowa się<br />

Quartus z nową procedurą<br />

syntezy logicznej?<br />

ARCHITECTURE tl27_arch OF tl27 IS<br />

BEGIN<br />

pandor: PROCESS (in)<br />

BEGIN<br />

CASE in IS<br />

WHEN "0010111010" => out out out out out out out out out out out out out out out out out out out out out out out out out out

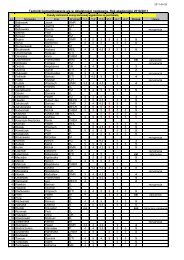

Implementacja filtru<br />

FIR<br />

F4<br />

F5<br />

F6<br />

F7<br />

F8<br />

F9<br />

Struktura<br />

sumatorów<br />

Bez dekompozycji<br />

Z dekompozycją<br />

LCs F max [MHz] LCs F max [MHz]<br />

pipel. 288 51.28 264 53.76<br />

comb. 224 25.25 204 26.60<br />

pipel. 642 47.62 530 52.36<br />

comb. 527 21.05 444 22.03<br />

pipel. 808 38.61 632 41.49<br />

comb. 710 19.27 551 19.61<br />

pipel. 680 47.62 560 47.85<br />

comb. 576 20.62 476 20.96<br />

pipel. 1404 42.74 834 48.31<br />

comb. 1314 22.73 746 22.73<br />

pipel 2624 31.25 1672 38.61<br />

comb. 2533 14.47 1564 20.92<br />

∑ 12330 8477<br />

% 100 68

Jaka jest przyczyna tej<br />

niekorzystnej sytuacji?<br />

Poziom RTL<br />

Sieć logiczna<br />

Specyfikacja HDL<br />

Synteza funkcjonalna<br />

niedoskonałość procedur<br />

syntezy logicznej<br />

Synteza logiczna<br />

Odwzorowanie<br />

technologiczne<br />

FPGA<br />

27

Skuteczne rozwiązanie zanie tego<br />

problemu…<br />

Tradycyjne procedury<br />

syntezy logicznej<br />

Specyfikacja HDL<br />

Synteza funkcjonalna<br />

Nowe procedury<br />

syntezy logicznej<br />

Synteza logiczna<br />

Odwzorowanie<br />

technologiczne<br />

FPGA<br />

28

Struktury programowalne FPGA znalazły<br />

ogromne zastosowania w układach<br />

cyfrowego przetwarzania sygnałów<br />

„FPGAs are on the verge of<br />

revolutionizing digital signal processing<br />

in the manner that programmable<br />

digital signal processors (PDSPs) did<br />

nearly two decades ago.”<br />

29

TELEFONIA KOMÓRKOWA<br />

PRZETWARZANIE DŹWID<br />

WIĘKU<br />

RADIOFONIA<br />

I TELEWIZJA<br />

Za pośrednictwem cyfrowego przetwarzania<br />

sygnałów w obszar zastosowań układ<br />

adów<br />

programowalnych rozszerza się na wiele dziedzin<br />

elektroniki, informatyki i telekomunikacji<br />

RADIOOMUNIKACJA<br />

TECHNIKA POMIAROWA<br />

TELEMEDYCYNA<br />

30

Nowe możliwo<br />

liwości<br />

Układy programowalne oraz języki opisu sprzętu stały się<br />

postawą koncepcji produktu wirtualnego - systemu,<br />

funkcji lub układu, który nie istnieje w rzeczywistości<br />

materialnej, ale potencjalnie – na podstawie kodu języka<br />

HDL - może być zrealizowany w każdej chwili w<br />

programowalnym module logicznym.<br />

31

Produkty wirtualne – co to jest?<br />

Struktury programowalne uzyskują fizyczną postać konkretnego<br />

układu cyfrowego dopiero w trakcie zaprogramowania.<br />

Z tej przyczyny układy te określa się mianem wirtualnych, gdyż<br />

do momentu zaprogramowania istnieją tylko jako odpowiednie<br />

pliki na dyskach komputerów (a nawet na kartce papieru).<br />

32

<strong>Technika</strong> produktów w wirtualnych<br />

Rynek własności intelektualnej IP (Intellectual Property)<br />

zawartej w układach zaprojektowanych i oferowanych do<br />

sprzedaży w postaci kodów źródłowych języków HDL.<br />

- ALTERA MEGAFUNCTION<br />

PARTNERS PROGRAM<br />

- XILINX ALLIANCE CORE<br />

- COMMON LICENSE<br />

CONSORTIUM<br />

- IP CATALYST PROGRAM<br />

- EXEMPLAR LOGIC-VENDOR<br />

INCENTIVE PROGRAM (VIP)<br />

- D & R DESIGN-REUSE.<br />

W Polsce: EVATRONIX<br />

-TILAB<br />

- inSILICON CORPORATION<br />

- SIBER CORE TECHNOLOGIES<br />

- DIGITAL COMMUNICATION<br />

TECHNOLOGIES<br />

- ARC CORES<br />

- VIRTUAL IP GROUP INC.<br />

- IP SEMICONDUCTORS<br />

- ALCATEL TECHNOLOGY<br />

LICENSING<br />

33

Evatronix S.A.<br />

Sztuka komputerowego tworzenia<br />

Rola wirtualnych komponentów w projektowaniu<br />

systemów scalonych

Komponenty wirtualne firmy Evatronix<br />

Mikrokontrolery oparte na architekturze 8051<br />

Koprocesory arytmetyczne<br />

Procesory sygnałowe<br />

Kontrolery łączy interfejsowych i sieciowych<br />

Kodery obrazów standardu JPEG2000<br />

35

Komponenty wirtualne firmy Evatronix<br />

W roku 2002 Evatronix S.A. opracowała wirtualny komponent<br />

kontroler Ethernet MAC (Media Access Control) 10/100Mbit.<br />

Komponent ten został zastosowany w...<br />

...airbus A380<br />

gdzie pełni rolę podstawowej arterii wymiany danych pomiędzy wszystkimi<br />

urządzeniami sterującymi i kontrolnym samolotu A380.<br />

36

Podsumowanie<br />

Układy programowalne umożliwiają<br />

budowę systemów cyfrowych łatwo i tanio.<br />

Ich uniwersalność i elastyczność<br />

predestynuje je do wielu zastosowań.<br />

Sytuacja ta czyni z układów<br />

programowalnych jedną z najciekawszych<br />

dziedzin techniki, której opanowanie może<br />

być kluczem do sukcesu zawodowego<br />

wielu specjalistów inżynierii<br />

komputerowej i teleinformatyki.<br />

37