4.5 Virtueller Speicher

4.5 Virtueller Speicher

4.5 Virtueller Speicher

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

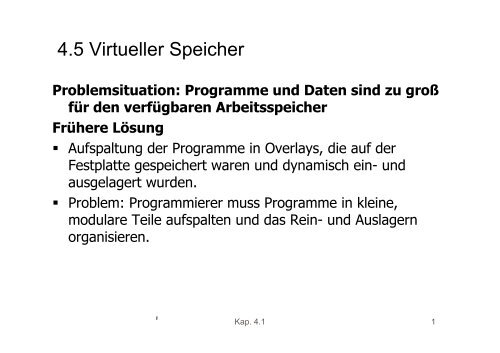

<strong>4.5</strong> <strong>Virtueller</strong> <strong>Speicher</strong><br />

Problemsituation: Programme und Daten sind zu groß<br />

für den verfügbaren Arbeitsspeicher<br />

Frühere Lösung<br />

Aufspaltung der Programme in Overlays, die auf der<br />

Festplatte gespeichert waren und dynamisch ein- und<br />

ausgelagert wurden.<br />

Problem: Programmierer muss Programme in kleine,<br />

modulare Teile aufspalten und das Rein- und Auslagern<br />

organisieren.<br />

Kap. 4.1 1

<strong>Virtueller</strong> <strong>Speicher</strong> und Cache: Gemeinsamkeiten<br />

<strong>Virtueller</strong> <strong>Speicher</strong> (VS)<br />

Ziel: Programmcode, Daten und<br />

Laufzeitkeller dürfen zusammen größer<br />

sein als der verfügbare Arbeitsspeicher.<br />

VS spiegelt einen (fast) beliebig großen<br />

Arbeitsspeicher von (fast) dessen<br />

Geschwindigkeit vor.<br />

Betriebssystem hält die “benötigten”<br />

<strong>Speicher</strong>bereiche im Arbeitsspeicher.<br />

Die anderen Bereiche liegen auf der<br />

Festplatte.<br />

Bei Zugriff auf fehlenden Bereich:<br />

Laden und Ersetzen einer Seite (page).<br />

Profitiert von Lokalität des Verhaltens.<br />

Cache<br />

Cache spiegelt einen schnellen <strong>Speicher</strong><br />

von der Größe des Arbeitsspeichers vor.<br />

Cache-Verwaltung hält “benötigte”<br />

<strong>Speicher</strong>blöcke im Cache.<br />

Die anderen Blöcke liegen im<br />

Arbeitsspeicher.<br />

Bei Zugriff auf fehlende Adresse: Laden<br />

und Ersetzen eines <strong>Speicher</strong>blocks.<br />

Profitiert von Lokalität des Verhaltens.<br />

Kap. 4.1 2

<strong>Virtueller</strong> <strong>Speicher</strong> und Cache: Unterschiede<br />

<strong>Virtueller</strong> <strong>Speicher</strong><br />

zwei Arten von Adressen:<br />

logische (virtuelle) Adressen im<br />

Programm<br />

physikalische Adressen für<br />

<strong>Speicher</strong>zellen<br />

Übersetzung<br />

logische → physikalische<br />

Adressen bei jedem Zugriff<br />

Cache<br />

identische Adressen für<br />

<strong>Speicher</strong>zellen in Cache und<br />

Arbeitsspeicher, Cache ist<br />

“transparent” für den<br />

Programmierer<br />

Kap. 4.1 3

<strong>Virtueller</strong> <strong>Speicher</strong>: Organisation<br />

<strong>Virtueller</strong> und physischer Adressraum werden aufgeteilt in<br />

Blöcke gleicher Größe,<br />

im virtuellen <strong>Speicher</strong> Seiten (pages),<br />

im physischen <strong>Speicher</strong> Rahmen (frames) genannt.<br />

Ein Rahmen kann also eine Seite aufnehmen.<br />

Eine Seite ist die Einheit der <strong>Speicher</strong>belegung und des<br />

Austauschs.<br />

Typische Seitengrößen: 2 – 16 KB.<br />

Kap. 4.1 4

Adressierung z.B. bei virtuellen 32-Bit-Adressen<br />

(d.h. 4-GB virtueller Adressraum)<br />

virtuelle Adresse:<br />

und Seitengröße s = 4096 Bytes:<br />

page offset<br />

20 12<br />

page = (virtuelle) Seitennummer<br />

offset = Distanzadresse<br />

je Prozess maximal 2 20 Seiten à 4096 Bytes<br />

Kap. 4.1 5

Seitentabelle<br />

Für jeden aktiven Prozess verwaltet das Betriebssystem<br />

eine Seitentabelle.<br />

Für jede Seite des Prozesses gibt es einen Tabelleneintrag<br />

mit Inhalt:<br />

• 1 Bit, resident, welches angibt, ob Seite im Hauptspeicher,<br />

• 1 Bit, dirty, welches angibt, ob Inhalt verändert wurde,<br />

• falls Seite im Hauptspeicher ist: Rahmennummer<br />

• falls Seite nicht im Hauptspeicher ist: Plattenspeicheradresse<br />

• weitere Information über <strong>Speicher</strong>schutz<br />

Kap. 4.1 6

Seitentabellen<br />

Register PTR zeigt auf die Basisadresse der Seitentabelle.<br />

p-ter Eintrag enthält Basisadresse, frame, des Rahmens für<br />

die Seite p, wenn Seite p im <strong>Speicher</strong> ist.<br />

*(PTR+p) zeigt auf Rahmen mit Basisadresse frame<br />

Adress-Übersetzung:<br />

address_map(p,d) {<br />

pa = *(PTR+p)+d;<br />

return pa<br />

}<br />

Die Seitentabelle für eine Adressraum von 4GByte bei einer<br />

Seitengröße von 4KByte hat 2 20 Einträge?<br />

Problem? Lösung?<br />

Kap. 4.1 7

Übersetzung: virtuelle in physische Adressen<br />

page offset<br />

frame<br />

Seitentabelle<br />

frame<br />

Hauptspeicher<br />

offset<br />

Jeder <strong>Speicher</strong>zugriff braucht eine Indirektion und eine Addition.<br />

Aufwendig!<br />

Kap. 4.1 8

Seitenaustausch (Demand paging)<br />

Seiten werden geladen, wenn gebraucht<br />

Bit resident, in der Seitentabelle gibt an,<br />

ob Seite aktuelle geladen ist<br />

Seitenfehler passiert bei Zugriff auf nicht geladene Seite<br />

address_map(p, w) {<br />

if (resident(*(PTR+p))) {<br />

pa = *(PTR+p)+w;<br />

return pa; }<br />

else page_fault;<br />

}<br />

Wird fehlende Seite geladen, muss evtl. eine Seite verdrängt werden<br />

→ Ersetzungsstrategie, z.B. LRU.<br />

Ist in der verdrängten Seite das dirty Bit gesetzt, muss die Seite<br />

zurück geschrieben werden.<br />

Kap. 4.1 9

Beschleunigung des Zugriffs<br />

Wie kann man den Aufwand für die Indirektion vermeiden?<br />

Cache für die zuletzt zugegriffenen Seitentabelleneinträge,<br />

Tanslation Lookaside Buffer, TLB<br />

voll assoziativ<br />

8 – 64 Einträge<br />

Statt Indirektion durch den <strong>Speicher</strong> und Addition parallele<br />

Suche in TLB, Dauer wenige Zyklen.<br />

Hitrate typischerweise bei 99%<br />

Laden von (page, frame) bei erstem Zugriff, aber<br />

Miss Penalty sehr groß, auf PowerPC 755: 12 reads, 1 write,<br />

520 Zyklen<br />

Voraussagbarkeit?<br />

Kap. 4.1 10

u page frame w d<br />

d = dirty bit<br />

w = writable bit – für Zugriffsschutz<br />

u = used bit: wird bei Verdrängung eines Eintrags<br />

durch einen neu benötigten Eintrags in allen Registern<br />

gelöscht und bei der Benutzung eines Eintrags in<br />

dessen Register gesetzt.<br />

Beim nächsten Verdrängen wird dort verdrängt,<br />

wo u nicht gesetzt ist,<br />

dabei d in Seitentabelle zurück schreiben!)<br />

Kap. 4.1 11

Schwankung der<strong>Speicher</strong>zugriffszeiten<br />

virtuelle<br />

Adresse<br />

a b<br />

D-Cache Arbeitsspeicher<br />

TLB<br />

Cache arbeitet mit<br />

virtuellen Adressen!<br />

Seitentabelle<br />

Kap. 4.1 12

Schwankung der <strong>Speicher</strong>zugriffszeiten<br />

virtuelle<br />

Adresse<br />

TLB-<br />

Hit<br />

a b<br />

TLB-<br />

Miss<br />

a base +<br />

TLB<br />

Cache arbeitet mit<br />

physischen Adressen!<br />

D-Cache<br />

Cache-<br />

Hit<br />

CPU<br />

Seitentabelle<br />

base<br />

+a<br />

Arbeitsspeicher<br />

Seitenfehlerer<br />

Kap. 4.1 13<br />

Seitentreffer

VS-Übergänge und ihre Kosten<br />

¬TLB(a)<br />

¬D-Cache(PT<br />

¬PT(a)<br />

lade Seite<br />

Seitenfehler<br />

PT(a)<br />

¬D-Cache(PT<br />

¬TLB(a)<br />

c<br />

tlb<br />

PT(a)<br />

D-Cache(PT<br />

TLB(a)<br />

lade D-Cache<br />

lade TLB<br />

Kap. 4.1 14

VS-Übergänge und ihre Kosten<br />

¬TLB(a)<br />

¬D-Cache(tr)<br />

¬PT(a)<br />

schlechtester Fall<br />

bester Fall<br />

TLB(a)<br />

D-Cache(tr)<br />

PT(a)<br />

ch<br />

lade Seite<br />

pf<br />

¬TLB(a)<br />

¬D-Cache(tr)<br />

PT(a)<br />

ma<br />

Lade Daten aus <strong>Speicher</strong><br />

(Daten auch in den D-Cache)<br />

cm = ma<br />

TLB(a)<br />

¬D-Cache(tr)<br />

PT(a)<br />

übersetze addr +<br />

load pte in TLB<br />

Kap. 4.1 15

Prozessor-<strong>Speicher</strong>-Schnittstelle<br />

Register:<br />

Memory Address Register (MAR)<br />

Verbunden mit Adress Bus<br />

Gibt Adresse für Laden aus oder<br />

<strong>Speicher</strong>n in <strong>Speicher</strong> an<br />

Memory Buffer Register (MBR)<br />

Signale:<br />

Verbunden mit Adress Bus<br />

enthält Inhalt der geladen wurde oder<br />

geschrieben werden soll<br />

writeEnable – gesetzt, wenn MBR an<br />

M[MAR] geschrieben werden soll,<br />

readEnable – gesetzt, wenn M[MAR] in<br />

MBR geladen werden soll.<br />

Prozessor<br />

(CPU)<br />

Hauptspeicher<br />

ALU<br />

Steuerwerk<br />

MAR MDR<br />

Systembus<br />

re we<br />

Kap. 4.1 16

Befehlsholen (Instruction Fetch)<br />

Zustand vorher:<br />

Adresse des nächsten Befehls ist in PC<br />

Addresse (MAR) platziert auf Adress-Bus<br />

Steuereinheit sendet ReadEnable-Signal<br />

Resultat aus dem <strong>Speicher</strong> erscheint auf<br />

dem Datenbus<br />

Inhalt des Datenbus wird ins MBR kopiert<br />

PC um 1 erhöht (parallel zum<br />

<strong>Speicher</strong>laden)<br />

Befehl wird aus MBR ins IR gebracht<br />

Zustand nachher: MBR ist wieder frei<br />

t1: MAR