Erstellen einer Verilog-Testbench im Cadence Design Framework

Erstellen einer Verilog-Testbench im Cadence Design Framework

Erstellen einer Verilog-Testbench im Cadence Design Framework

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

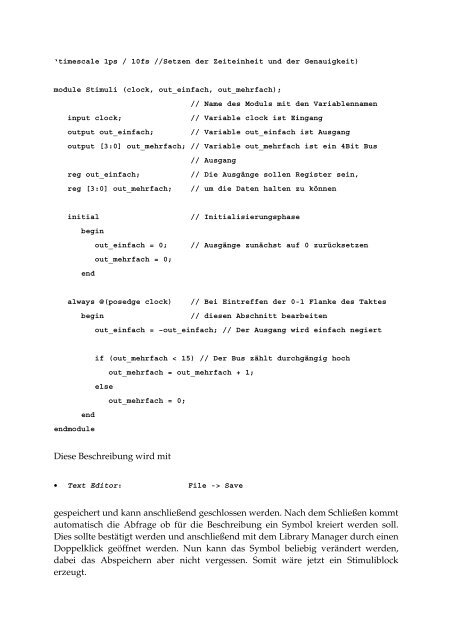

‘t<strong>im</strong>escale 1ps / 10fs //Setzen der Zeiteinheit und der Genauigkeit)<br />

module St<strong>im</strong>uli (clock, out_einfach, out_mehrfach);<br />

// Name des Moduls mit den Variablennamen<br />

input clock; // Variable clock ist Eingang<br />

output out_einfach; // Variable out_einfach ist Ausgang<br />

output [3:0] out_mehrfach; // Variable out_mehrfach ist ein 4Bit Bus<br />

// Ausgang<br />

reg out_einfach; // Die Ausgänge sollen Register sein,<br />

reg [3:0] out_mehrfach; // um die Daten halten zu können<br />

initial // Initialisierungsphase<br />

begin<br />

end<br />

out_einfach = 0; // Ausgänge zunächst auf 0 zurücksetzen<br />

out_mehrfach = 0;<br />

always @(posedge clock) // Bei Eintreffen der 0-1 Flanke des Taktes<br />

begin // diesen Abschnitt bearbeiten<br />

end<br />

endmodule<br />

out_einfach = ~out_einfach; // Der Ausgang wird einfach negiert<br />

if (out_mehrfach < 15) // Der Bus zählt durchgängig hoch<br />

else<br />

out_mehrfach = out_mehrfach + 1;<br />

out_mehrfach = 0;<br />

Diese Beschreibung wird mit<br />

• Text Editor: File -> Save<br />

gespeichert und kann anschließend geschlossen werden. Nach dem Schließen kommt<br />

automatisch die Abfrage ob für die Beschreibung ein Symbol kreiert werden soll.<br />

Dies sollte bestätigt werden und anschließend mit dem Library Manager durch einen<br />

Doppelklick geöffnet werden. Nun kann das Symbol beliebig verändert werden,<br />

dabei das Abspeichern aber nicht vergessen. Somit wäre jetzt ein St<strong>im</strong>uliblock<br />

erzeugt.