Erstellen einer Verilog-Testbench im Cadence Design Framework

Erstellen einer Verilog-Testbench im Cadence Design Framework

Erstellen einer Verilog-Testbench im Cadence Design Framework

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

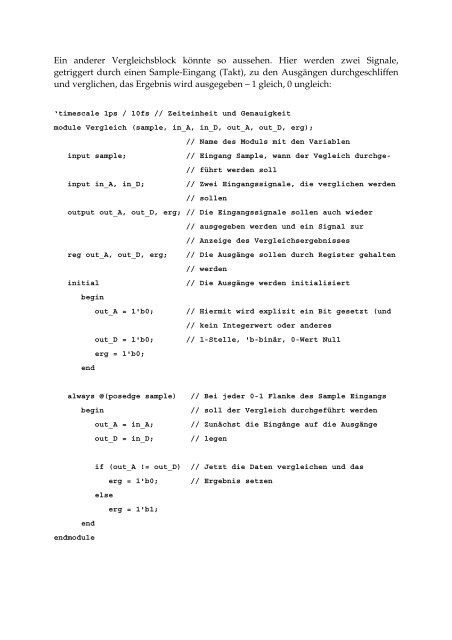

Ein anderer Vergleichsblock könnte so aussehen. Hier werden zwei Signale,<br />

getriggert durch einen Sample-Eingang (Takt), zu den Ausgängen durchgeschliffen<br />

und verglichen, das Ergebnis wird ausgegeben – 1 gleich, 0 ungleich:<br />

‘t<strong>im</strong>escale 1ps / 10fs // Zeiteinheit und Genauigkeit<br />

module Vergleich (sample, in_A, in_D, out_A, out_D, erg);<br />

// Name des Moduls mit den Variablen<br />

input sample; // Eingang Sample, wann der Vegleich durchge-<br />

// führt werden soll<br />

input in_A, in_D; // Zwei Eingangssignale, die verglichen werden<br />

// sollen<br />

output out_A, out_D, erg; // Die Eingangssignale sollen auch wieder<br />

// ausgegeben werden und ein Signal zur<br />

// Anzeige des Vergleichsergebnisses<br />

reg out_A, out_D, erg; // Die Ausgänge sollen durch Register gehalten<br />

// werden<br />

initial // Die Ausgänge werden initialisiert<br />

begin<br />

end<br />

out_A = 1'b0; // Hiermit wird explizit ein Bit gesetzt (und<br />

// kein Integerwert oder anderes<br />

out_D = 1'b0; // 1-Stelle, 'b-binär, 0-Wert Null<br />

erg = 1'b0;<br />

always @(posedge sample) // Bei jeder 0-1 Flanke des Sample Eingangs<br />

begin // soll der Vergleich durchgeführt werden<br />

end<br />

endmodule<br />

out_A = in_A; // Zunächst die Eingänge auf die Ausgänge<br />

out_D = in_D; // legen<br />

if (out_A != out_D) // Jetzt die Daten vergleichen und das<br />

else<br />

erg = 1'b0; // Ergebnis setzen<br />

erg = 1'b1;