Erstellen einer Verilog-Testbench im Cadence Design Framework

Erstellen einer Verilog-Testbench im Cadence Design Framework

Erstellen einer Verilog-Testbench im Cadence Design Framework

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

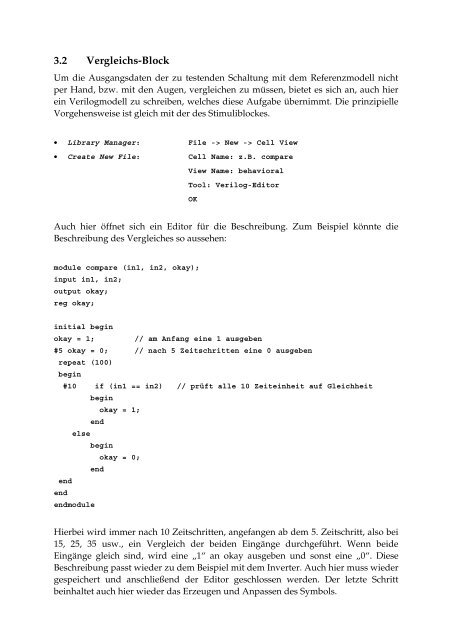

3.2 Vergleichs-Block<br />

Um die Ausgangsdaten der zu testenden Schaltung mit dem Referenzmodell nicht<br />

per Hand, bzw. mit den Augen, vergleichen zu müssen, bietet es sich an, auch hier<br />

ein <strong>Verilog</strong>modell zu schreiben, welches diese Aufgabe übern<strong>im</strong>mt. Die prinzipielle<br />

Vorgehensweise ist gleich mit der des St<strong>im</strong>uliblockes.<br />

• Library Manager: File -> New -> Cell View<br />

• Create New File: Cell Name: z.B. compare<br />

View Name: behavioral<br />

Tool: <strong>Verilog</strong>-Editor<br />

OK<br />

Auch hier öffnet sich ein Editor für die Beschreibung. Zum Beispiel könnte die<br />

Beschreibung des Vergleiches so aussehen:<br />

module compare (in1, in2, okay);<br />

input in1, in2;<br />

output okay;<br />

reg okay;<br />

initial begin<br />

okay = 1; // am Anfang eine 1 ausgeben<br />

#5 okay = 0; // nach 5 Zeitschritten eine 0 ausgeben<br />

repeat (100)<br />

begin<br />

#10 if (in1 == in2) // prüft alle 10 Zeiteinheit auf Gleichheit<br />

begin<br />

okay = 1;<br />

end<br />

else<br />

begin<br />

okay = 0;<br />

end<br />

end<br />

end<br />

endmodule<br />

Hierbei wird <strong>im</strong>mer nach 10 Zeitschritten, angefangen ab dem 5. Zeitschritt, also bei<br />

15, 25, 35 usw., ein Vergleich der beiden Eingänge durchgeführt. Wenn beide<br />

Eingänge gleich sind, wird eine „1“ an okay ausgeben und sonst eine „0“. Diese<br />

Beschreibung passt wieder zu dem Beispiel mit dem Inverter. Auch hier muss wieder<br />

gespeichert und anschließend der Editor geschlossen werden. Der letzte Schritt<br />

beinhaltet auch hier wieder das Erzeugen und Anpassen des Symbols.