3. Übersicht zum µC 8052 - No official entry point - HAW Hamburg

3. Übersicht zum µC 8052 - No official entry point - HAW Hamburg

3. Übersicht zum µC 8052 - No official entry point - HAW Hamburg

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Prof. Dr. J. Reichardt<br />

Prof. Dr. B. Schwarz UART - CPLD 95108 - C <strong>8052</strong><br />

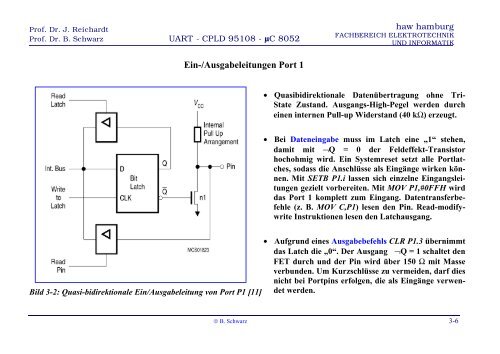

Ein-/Ausgabeleitungen Port 1<br />

Bild 3-2: Quasi-bidirektionale Ein/Ausgabeleitung von Port P1 [11]<br />

haw hamburg<br />

FACHBEREICH ELEKTROTECHNIK<br />

UND INFORMATIK<br />

• Quasibidirektionale Datenubertragung ohne Tri-<br />

State Zustand. Ausgangs-High-Pegel werden durch<br />

einen internen Pull-up Widerstand (40 kW) erzeugt.<br />

• Bei Dateneingabe muss im Latch eine “1– stehen,<br />

damit mit Q = 0 der Feldeffekt-Transistor<br />

hochohmig wird. Ein Systemreset setzt alle Portlatches,<br />

sodass die Anschlusse als Eingange wirken konnen.<br />

Mit SETB P1.i lassen sich einzelne Eingangsleitungen<br />

gezielt vorbereiten. Mit MOV P1,#0FFH wird<br />

das Port 1 komplett <strong>zum</strong> Eingang. Datentransferbefehle<br />

(z. B. MOV C,P1) lesen den Pin. Read-modifywrite<br />

Instruktionen lesen den Latchausgang.<br />

• Aufgrund eines Ausgabebefehls CLR P1.3 ubernimmt<br />

das Latch die “0–. Der Ausgang Q = 1 schaltet den<br />

FET durch und der Pin wird uber 150 W mit Masse<br />

verbunden. Um Kurzschlusse zu vermeiden, darf dies<br />

nicht bei Portpins erfolgen, die als Eingange verwendet<br />

werden.<br />

© B. Schwarz 3-6