Anleitung - HAW Hamburg

Anleitung - HAW Hamburg

Anleitung - HAW Hamburg

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

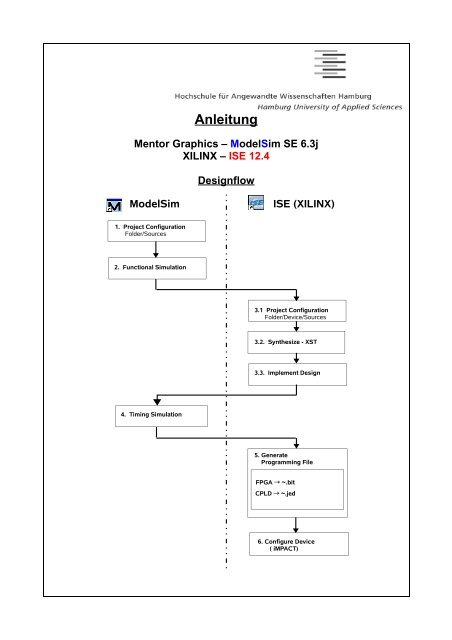

<strong>Anleitung</strong><br />

Mentor Graphics – ModelSim SE 6.3j<br />

XILINX – ISE 12.4<br />

ModelSim<br />

1. Project Configuration<br />

Folder/Sources<br />

2. Functional Simulation<br />

4. Timing Simulation<br />

Designflow<br />

ISE (XILINX)<br />

3.1 Project Configuration<br />

Folder/Device/Sources<br />

3.2. Synthesize - XST<br />

3.3. Implement Design<br />

5. Generate<br />

Programming File<br />

FPGA→~.bit<br />

CPLD→~.jed<br />

6. Configure Device<br />

( iMPACT)

Inhaltsverzeichnis<br />

1.Grundsätzliche Vorgaben..................................................................................................3<br />

1.1. Vorgeschriebenes Arbeitsverzeichnis.......................................................................3<br />

1.2. Verzeichnis- / Projektstruktur....................................................................................3<br />

2.ModelSim - Funktionale Simulation..................................................................................4<br />

2.1. ModelSim - Projekterstellung ...................................................................................4<br />

2.2. ModelSim - Compilierung ........................................................................................6<br />

2.3. ModelSim - Simulation..............................................................................................7<br />

3.ISE...................................................................................................................................10<br />

3.1. ISE – Projekterstellung...........................................................................................10<br />

3.1.1. Erstellen eines neuen Design Files.................................................................12<br />

3.1.2. Einbinden eines bestehenden Design Files....................................................13<br />

3.2. ISE – Synthese.......................................................................................................15<br />

3.2.1. ISE – Synthes für CPLD..................................................................................15<br />

3.2.2. ISE - Synthese für FPGA.................................................................................17<br />

3.3. ISE - Implementierung............................................................................................18<br />

3.3.1. ISE - Implementierung für CPLD.....................................................................18<br />

3.3.2. ISE - Implementierung für FPGA.....................................................................20<br />

4.ModelSim - Timing Simulation........................................................................................21<br />

5.ISE - Generieren des Programmierfiles..........................................................................23<br />

5.1. ISE - Generieren des Programmierfiles für CPLD..................................................23<br />

5.2. ISE - Generieren des Programmierfiles für FPGA.................................................23<br />

5.3. ISE - Generieren des Programmierfiles für EEPROM auf Modul Spartan3E........24<br />

6.ISE - Programmieren des IC...........................................................................................28<br />

6.1. Vorbereitung............................................................................................................28<br />

6.2. Programmierung CPLD / FPGA (direkt über JTAG-Schnittstelle)..........................28<br />

6.3. Programmierung des EEPROM's für Spartan3E (Modulares System)..................32<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 2 / 37

1. Grundsätzliche Vorgaben<br />

1.1. Vorgeschriebenes Arbeitsverzeichnis<br />

Es ist grundsätzlich das vorgesehene Arbeitsverzeichnis für das jeweilige<br />

Entwicklungstool zu verwenden.<br />

1.2. Verzeichnis- / Projektstruktur<br />

Die Verzeichnisstruktur auf Laufwerk D: ist wie nachstehend gegliedert.<br />

Für die Arbeit mit ModelSim und ISE sind die Verzeichnisse<br />

ModelSim_Projects, ISE_Projects sowie VHDL_Codes vorgesehen.<br />

Im Verzeichnis ISE_Lab_Files sind Hilfsdateien, wie z.B. die<br />

Vorlagen für die ~.do- und ~.ucf-Dateien, welche für die Projekte<br />

benötigt werden, abgelegt.<br />

Projektverlauf:<br />

Zuerst werden die vorbereiteten Quelldateien (~.vhd, ~.do, ~.ucf) in das Verzeichnis<br />

D:\VHDL_Codes kopiert.<br />

Danach wird ein ModelSim-Projekt in D:\ModelSim_Projects erstellt.<br />

Nach der funktionalen Simulation wird im Projektverzeichnis D:ISE_Projects ein<br />

ISE-Projekt erstellt. In diesem werden die Dateien für die Timingsimulation erzeugt.<br />

Anschließend wird die Timingsimulation mit ModelSim durchgeführt.<br />

Zuletzt wird das IC programmiert.<br />

Keine Leerzeichen oder Sonderzeichen wie “ü,ö,ä,/,\?,!,”,(,),%,” u.a. in<br />

Datei- oder Verzeichnisnamen verwenden!<br />

Keine Dateien oder Verzeichnisse irgendwo auf C:\ oder dem Desktop erstellen!<br />

Diese gehen bei einem evtl. erforderlichen Neustart des PC’s verloren!<br />

Zur Beachtung! Daten, die nach der jeweiligen Arbeitssitzung nicht auf<br />

externe Speichermedien kopiert werden, sind gegebenenfalls<br />

unwiederbringlich verloren.<br />

Nach einem Neustart des Rechners können die Projekte aus dem<br />

Ordner D:\BACKUP gerettet werden.<br />

Nach einem weitereren Neustart sind alle Projekte gelöscht.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 3 / 37

Sie befinden sich in Schritt 1.<br />

Project Configuration<br />

(ModelSim)<br />

2. ModelSim - Funktionale Simulation<br />

2.1. ModelSim - Projekterstellung<br />

– Starten von ModelSim durchDoppelklick auf<br />

Desktop Symbol<br />

– File → New → Project...<br />

– Im Create Project Fenster<br />

In Project Location über Browse das<br />

Verzeichnis<br />

D:\ModelSim_Projects auswählen<br />

– Ergänzen mit dem Projektordnername<br />

D:\ModelSim_Projects/my_project_folder<br />

– In Project Name den eigenen Projektnamen<br />

my_project eintragen<br />

– Default Library Name belassen auf work<br />

– Copy Library Mappings auswählen<br />

– OK<br />

– Bestätigen, dass ein neuer Projektordner erstellt werden soll.<br />

Es öffnet sich das Fenster Add Items to the Project<br />

– Nun die vorbereiteten Quellfiles (.vhd, .do) in den<br />

Ordner D:\VHDL_Codes kopieren, wenn noch nicht<br />

geschehen.<br />

Im Fenster Add Items to the Project<br />

– Klick auf Add Existing File<br />

Im Fenster Add File to Project<br />

– Über Browse Auswählen von<br />

my_sourcefile.vhd aus dem<br />

Quellordner (Quellordner ist Ihr<br />

Verzeichnis, in dem die vorbereitete<br />

Datei liegt; sollte D:\VHDL_Codes sein)<br />

– Reference from current location<br />

markieren.<br />

– OK<br />

Die Datei wird dem Projekt hinzugefügt.<br />

– Fenster Add Items to the Project<br />

mit Close schliessen.<br />

Das Projekt ist erstellt.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 4 / 37

Sie befinden sich in Schritt 1.<br />

Project Configuration<br />

(ModelSim)<br />

Im Reiter Project steht<br />

das eigene Quellfile<br />

my_sourcefile.vhd.<br />

Der Status ist mit einem<br />

? markiert.<br />

Das bedeutet, dieses<br />

Quellfile ist noch nicht<br />

compiliert.<br />

Im Reiter Library sind die<br />

eingebundenen Libraries<br />

aufgeführt.<br />

Die Library „work“ ist<br />

noch leer.<br />

(Durch einen Bug<br />

in ModelSim wird diese<br />

Library aber als gefüllt<br />

gekennzeichnet; es steht<br />

ein Pluszeichen davor.<br />

Es verschwindet, sobald<br />

darauf geklickt wird.)<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Neues Projekt<br />

wurde erstellt.<br />

Seite 5 / 37<br />

Altes Projekt<br />

wurde nicht<br />

gefunden.

Sie befinden sich in Schritt 2.<br />

Functional Simulation<br />

(ModelSim)<br />

2.2. ModelSim - Compilierung<br />

– Im Reiter Project das Designfile<br />

my_sourcefile<br />

markieren und durch Klick auf die<br />

Ikone die Datei kompilieren.<br />

Im Reiter Project hat das Design File nun<br />

den Status compiliert (grünes Häkchen), d.h.<br />

die Compilierung ist ordnungsgemäß<br />

verlaufen.<br />

Im Fenster Transcript wird in grüner Schrift<br />

eine Bestätigungsmeldung angezeigt.<br />

Ist die Compilierung nicht erfolgreich, so ist<br />

die Fehlermeldung in roter Schrift dargestellt.<br />

Ein Doppelklick auf diese Meldung öffnet<br />

eine erweiterte Fehlerbeschreibung.<br />

Im Reiter Library steht nun in work<br />

das compilierte Quellfile.<br />

Erkennbar am + vor work.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 6 / 37

Sie befinden sich in Schritt 2.<br />

Functional Simulation<br />

(ModelSim)<br />

2.3. ModelSim - Simulation<br />

– Öffne Simulate → Runtime Options...<br />

– Setze<br />

Default Run: 100<br />

(Falls keine Maßeinheit eingetragen wird,<br />

ist ps gesetzt.)<br />

Default Force Type: Freeze<br />

Default Radix: Hexadecimal<br />

– OK<br />

–<br />

– Klick auf (Simulate)<br />

Es öffnet sich das Fenster<br />

Start Simulation.<br />

Im Reiter Design die Library<br />

work öffnen.<br />

Die zu simulierende Datei<br />

my_sourcefile.vhd<br />

markieren.<br />

(Im Beispiel heißt die<br />

zugehörige entity „exor“.)<br />

Evtl. zur besseren Sicht das<br />

Fenster am rechten Rand<br />

mit der Maus aufziehen.<br />

– OK<br />

Die Simulation wird gestartet.<br />

Im ModelSim-Fenster erscheint ein weiteres Fenster Objects.<br />

In diesem werden die Signalnamen aufgelistet, wie sie im Designfile angegeben sind.<br />

Im Transcript Fenster werden die zugehörigen geladenen Libraries gezeigt.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 7 / 37

Sie befinden sich in Schritt 2.<br />

Functional Simulation<br />

(ModelSim)<br />

Um eine Berechnung der<br />

Simulationswerte in<br />

Abhängigkeit von Zuständen<br />

der Eingangssignale zu<br />

ermöglichen, werden dem<br />

Simulator über ein Macro<br />

(.do File) oder eine Testbench<br />

(.vhd File) Signalmuster für die<br />

Eingangssignale vorgegeben.<br />

Das Ergebnis ist ein<br />

Impulsmuster, welches im<br />

Wave Fenster, wie weiter<br />

unten gezeigt, grafisch<br />

dargestellt wird.<br />

(Wird eine Testbench benutzt, so ist diese ins Projekt wie ein Anwendungs-File<br />

einzubinden. Dabei ist zu beachten, dass das User-Design als Komponente in die<br />

Testbench eingebunden ist.)<br />

– Klick auf<br />

Tools → TCL → Execute Macro...<br />

– Auswählen my_do_file.do<br />

(Dieses File ist mittels eines<br />

einfachen Texteditor zu erstellen,<br />

um Steuerzeichen im Text zu<br />

vermeiden, die den Simulator<br />

irritieren.)<br />

– Klick Open<br />

Ist das Wave Fenster noch von einer vorherigen<br />

Berechnung geöffnet, Wave Format abwählen, um<br />

doppelte Eintragungen im Wavefenster zu vermeiden.<br />

– Klick Restart<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 8 / 37

Sie befinden sich in Schritt 2.<br />

Functional Simulation<br />

(ModelSim)<br />

– Im Wave Fenster ist das<br />

Ergebnis zu kontrollieren.<br />

Über die Lupenfunktionen<br />

kann die Auflösung des<br />

Wave-Fensters eingestellt<br />

werden.<br />

Durch Klick aufden<br />

Undock-Button<br />

lässt sich das Wave-Fenster<br />

ablösen und<br />

bildschirmfüllend vergrößern.<br />

Links unten im Wavefenster sind Auswahlbuttons zur Einstellung des<br />

Wavefensters zu finden. Damit lassen sich Kursors ein- und ausblenden sowie die<br />

Rasterung der Zeitdarstellung verändern.<br />

Die funktionale Simulation ist hiermit abgeschlossen.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 9 / 37

Sie befinden sich in Schritt 3.1.<br />

Project Configuration<br />

(ISE)<br />

3. ISE<br />

3.1. ISE – Projekterstellung<br />

– Klick auf die Ikone auf dem Desktop öffnet den Projektnavigator.<br />

– New Project... auswählen<br />

Es öffnet sich der<br />

New Project Wizzard<br />

mit dem<br />

Create New Project Fenster<br />

– Auswahl in Working Directory: D:\ISE_Projects<br />

– Auswahl in Location: D:\ISE_Projekts<br />

– Im Feld Name: den eigenen Projektnamen angeben, (im Beispiel: my_project).<br />

Im Feld Location: wird der<br />

Eintrag my_project automatisch ergänzt und somit ein Projektordner mit dem<br />

Projektnamen erzeugt.<br />

– Top-Level Source Type: auf HDL stellen.<br />

– Next<br />

Im Fenster Description: können<br />

Bemerkungen zum Projekt<br />

eingetragen werden.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 10 / 37

Sie befinden sich in Schritt 3.1.<br />

Project Configuration<br />

(ISE)<br />

– Die Hardware über<br />

Family, Device,<br />

Package und Speed<br />

entsprechend<br />

Tabelle auswählen.<br />

Einstellungen wie im<br />

nebenstehenden Bild<br />

auswählen.<br />

– Next<br />

CPLD FPGA<br />

Family XC9500 CPLD Coolrunner2 CPLD Spartan3 Spartan3E<br />

Device XC95108 XC9572 XC2C256 XC3S400 XC3S500E<br />

Package PC84 PC44 PQ208 TQ144 PQ208<br />

Speed -20 -15 -7 -4 -4<br />

– Es wird eine<br />

Zusammenfassung der<br />

Projekteinstellungen angezeigt.<br />

– Finish<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 11 / 37

Sie befinden sich in Schritt 3.1.<br />

Project Configuration<br />

(ISE)<br />

Am linken Rand des Fensters Design sind<br />

nebenstehende Iconen zu finden.<br />

Diese dienen zur Auswahl der gezeigten Funktionen.<br />

3.1.1. Erstellen eines neuen Design Files<br />

– Durch Anklicken der Icone New Source<br />

wird der New Source Wizzard gestartet,<br />

um ein neues Design File zu erstellen.<br />

– Markieren des Source Typ<br />

(hier VHDL Modul)<br />

– In File name: Name des<br />

Source Files eingeben.<br />

Sinnvoll ist ein Name, der<br />

einen Hinweis auf die<br />

Funktion des zu<br />

beschreibenden Designs<br />

gibt.<br />

– Haken bei Add to project<br />

setzen. Dadurch wird das<br />

erzeugte File in den<br />

Projektordner geschrieben.<br />

– Next<br />

– In Feld Architecture name<br />

den eigenen Architektur-<br />

Namen eintragen.<br />

– Port-Namen vergeben. Das<br />

sind die Signalnamen, die<br />

am Chip an den Pin<br />

anliegen sollen.<br />

– Zu jedem Signalnamen bei<br />

Direction die<br />

Datenflussrichtung<br />

auswählen.<br />

– Bei den Signalen, die einen<br />

Bus darstellen, bei Bus<br />

einen Haken setzen und<br />

die Vektorbreite bei MSB<br />

und LSB eintragen.<br />

Vektor B ist hier im Beispiel<br />

5 Bit breit.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 12 / 37<br />

New Source<br />

Add Source<br />

Add Copy of Source<br />

Set Module as Top<br />

Remove Source<br />

Edit Design Properties<br />

Edit Source Properties<br />

Change Orientation

Sie befinden sich in Schritt 3.1.<br />

Project Configuration<br />

(ISE)<br />

–<br />

– Next<br />

Es öffnet sich der Editor mit einem Designgerüst mit Voreinstellungen.<br />

Die Datentypen in der Portmap sind STD_LOGIC bzw. STD_LOGIC_VECTOR. Falls<br />

gefordert, sind diese in bit bzw. bit_vector umzubenennen.<br />

Die Architektur ist nun zu beschreiben.<br />

3.1.2. Einbinden eines bestehenden Design Files<br />

Üblicherweise liegt das bestehende Design File im Ordner D:\VHDL_Codes oder auf<br />

dem USB-Stick.<br />

– Click auf Icone Add Copy of Source Es öffnet sich das Fenster Add<br />

Source.<br />

Auswählen von D:\VHDL_Codes\my_sourcefile.vhd<br />

und wenn schon vorhanden my_sourcefile.ucf.<br />

– Open<br />

– Auswählen des/der<br />

bestehenden Quellfiles<br />

aus Ordner<br />

D:\VHDL_Codes.<br />

Es können .vhd-Files<br />

(Design-Files) und .ucf-<br />

Files (User Constraint<br />

Files) gleichzeitig<br />

eingefügt werden.<br />

(.ucf-Files beschreiben<br />

u.a. die Zuweisung der<br />

E/A-Signale auf<br />

Gehäuse-Pin)<br />

Es werden die .vhd-Dateien ausgewählt, die schon im ModelSim-Projekt verwendet<br />

wurden.<br />

Die Quellfiles werden nicht in das ISE-Projekt kopiert.<br />

Dadurch wird vermieden, dass es unterschiedliche Versionen in ModelSim und ISE<br />

gibt.<br />

– Next<br />

Im Fenster<br />

Adding Source Files...<br />

wird der Status der Quellfiles<br />

im Projekt angezeigt. Falls es<br />

Probleme beim Einbinden gibt,<br />

steht statt des grünen Hakens<br />

ein rotes Kreuz. Dazu wird<br />

eine Fehlermeldung generiert.<br />

– OK<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 13 / 37

Sie befinden sich in Schritt 3.1.<br />

Project Configuration<br />

(ISE)<br />

Die Files werden nun in das Projekt<br />

eingebunden und im Fenster Hierarchy<br />

angezeigt.<br />

Um die verschiedenen Arbeitsschritte im Projekt ausführen zu können, ist im Fenster<br />

Hierarchy eine Vorauswahl durch Markieren zu treffen. Je nachdem welcher Eintrag<br />

dort markiert ist, werden im Fenster Processes: die für diese Auswahl möglichen<br />

Arbeitsschritte angeboten.<br />

Im rechten großen Fenster werden die verschiedenen Editoren und Anzeigetools<br />

geöffnet.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 14 / 37

Sie befinden sich in Schritt 3.2<br />

Sythesize – XST<br />

(ISE)<br />

3.2. ISE – Synthese<br />

3.2.1. ISE – Synthes für CPLD<br />

– Im Fenster Hierarchy das zu bearbeitende Design<br />

File my_sourcefile.vhd markieren.<br />

– Im Fenster Processes:<br />

durch Klick auf + Implement Design öffnen.<br />

– Im Fenster Processes:<br />

durch Klicken auf + Synthesize-XST öffnen.<br />

– Durch Doppelklick auf Check Syntax wird das<br />

Design-File auf syntaktische Fehler überprüft.<br />

Das Tool prüft nicht, ob das Design-File die<br />

gewünschte Logic beschreibt!<br />

– Evtl. auftretende Fehler beseitigen.<br />

– Doppelklick auf Synthesize – XST<br />

Die Synthese wird durchgeführt.<br />

Ein arbeitendes Modul wird mit einer blauen sich drehenden<br />

Scheibe gekennzeichnet.<br />

Zur Orientierung, dass die einzelnen Arbeitsschritte<br />

ordnungsgemäß erledigt sind, erscheint links neben den<br />

einzelnen Prozessschritten ein grüner Kreis mit<br />

weißem Häkchen.<br />

Wurde im jeweiligen Arbeitsschritt ein Fehler erkannt,<br />

erscheint hier ein roter Kreis mit weißem Kreuz. Ist ein roter<br />

Kreis mit Fragezeichen angezeigt, so sind für diesen<br />

Prozessschritt noch nicht alle Arbeitsschritte abgearbeitet.<br />

Ein gelber Kreis mit weißem Ausrufungszeichen zeigt an,<br />

dass in diesem Arbeitsschritt eine Warnung ausgegeben<br />

wurde.<br />

Das unterste Fenster auf dem Bildschirm ist ein Protokollfenster.<br />

Je nach dem welcher der Reiter Console, Errors, Warnings oder Find in Files Results<br />

ausgewählt wurde, werden entsprechende Meldungen angezeigt.<br />

Die Abarbeitungsschritte der einzelnen Module werden bei Auswahl Console in diesem<br />

Fenster protokolliert. Die Fehler- bzw. Warnungsmeldungen werden hier ausführlicher<br />

gezeigt als in den Fenstern Error oder Warnings.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 15 / 37

Sie befinden sich in Schritt 3.2<br />

Sythesize – XST<br />

(ISE)<br />

Doppelklick auf View RTL-Schematic öffnet den Schaltplaneditor.<br />

Die Darstellung erfolgt in einer hierachischen Struktur.<br />

Durch Klicken auf die jeweiligen Blöcke der Schaltung lassen sich die<br />

Schaltungsstrukturen bis auf Gatterebene herunterbrechen.<br />

Das nebenstehende Bild<br />

zeigen beispielhaft die<br />

hierarchische Struktur<br />

einer XOR-Schaltung, die in<br />

VHDL beschrieben wurde.<br />

Die in der Entity<br />

angegebenen<br />

Signalnamen X1,X2 und Q1<br />

werden in den tiefer<br />

liegenden Ebenen durch<br />

die Namen Data(0), Data(1)<br />

und Result bzw. Xo1<br />

und Xo1 ersetzt.<br />

Das geschieht, weil für ein<br />

XOR bereits ein<br />

Funktionsmodell mit diesen Signalnamen im Sythesetool existiert.<br />

Weiter mit Pkt. 3.3.1 ISE - Implementierung für CPLD<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 16 / 37

Sie befinden sich in Schritt 3.2<br />

Sythesize – XST<br />

(ISE)<br />

3.2.2. ISE - Synthese für FPGA<br />

Dies sind die Fenster Hierarchy: und Processes:<br />

nach Erstellung eines FPGA Projektes mit<br />

Einbindung der Quellfiles.<br />

– Im Fenster Hierarchy: das Design File my_sourcefile.vhd<br />

markieren.<br />

Der Filename steht in Klammern. Vorn wird der Name der<br />

Top-Entity angezeigt.<br />

– Im Fenster Processes:<br />

durch Klicken auf + Synthesize-XST öffnen.<br />

– Durch Doppelklick auf Check Syntax wird das<br />

Design-File auf syntaktische Fehler überprüft.<br />

Das Tool prüft nicht, ob das Design-File die<br />

gewünschte Logic beschreibt!<br />

– Evtl. auftretende Fehler beseitigen.<br />

– Doppelklick auf Synthesize – XST<br />

Die Synthese wird durchgeführt.<br />

Ein arbeitendes Modul wird mit einer blauen sich drehenden<br />

Scheibe gekennzeichnet.<br />

Zur Orientierung, dass die einzelnen Arbeitsschritte<br />

ordnungsgemäß erledigt sind, erscheint links neben den<br />

einzelnen Prozessschritten ein grüner Kreis mit weißem<br />

Häkchen.<br />

Wurde im jeweiligen Arbeitsschritt ein Fehler erkannt,<br />

erscheint hier ein roter Kreis mit weißem Kreuz. Ist ein roter<br />

Kreis mit Fragezeichen angezeigt, so sind für diesen<br />

Prozessschritt noch nicht alle Arbeitsschritte abgearbeitet.<br />

Ein gelber Kreis mit weißem Ausrufungszeichen zeigt an,<br />

dass in diesem Arbeitsschritt eine Warnung ausgegeben<br />

wurde.<br />

Das unterste Fenster auf dem Bildschirm ist ein Protokollfenster.<br />

Je nach dem welcher der Reiter Console, Errors, Warnings oder Find in Files Results<br />

ausgewählt wurde, werden entsprechende Meldungen angezeigt.<br />

Die Abarbeitungsschritte der einzelnen Module werden bei Auswahl Console in diesem<br />

Fenster protokolliert. Die Fehler- bzw. Warnungsmeldungen werden hier ausführlicher<br />

gezeigt als in den Fenstern Error oder Warnings.<br />

Durch Klick auf View RTL Schematic wird der Schaltplan angezeigt. Durch Klicken auf die<br />

Funktionsboxen lässt sich durch die Hierarchie navigieren (siehe S.16).<br />

Weiter mit 3.3.2 ISE - Implementierung für FPGA<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 17 / 37

Sie befinden sich in Schritt 3.3<br />

Implement Design<br />

(ISE)<br />

3.3. ISE - Implementierung<br />

3.3.1. ISE - Implementierung für CPLD<br />

Voraussetzung: Die Synthese ist ordnungsgemäß abgelaufen.<br />

Hinweis!<br />

Vor der Implementierung sollte unbedingt das User Constraint File my_ucf_file.ucf in<br />

das Projekt eingebunden werden, falls noch nicht geschehen.<br />

Als Mustergeneratoren stehen für das Modulare System die Files<br />

UCF-GeneratorforModSys.ods (OpenOffice/Calc) und<br />

UCF-GeneratorforModSys.xls (MS Office/Excel)<br />

auf der Laborseite http://ieweb.etech.haw-hamburg.de/yamlt3/Download.285.0.html<br />

im Downlodbereich zur Verfügung. Die Benutzung wird in den jeweiligen Files erläutert.<br />

Für die CPLD Boards XC95108 und XC9572 werden auf der Webseite Musterfiles zur<br />

Verfügung gestellt.<br />

Ohne Verwendung des User Constraint File legt das ISE Implementierungstool die<br />

Pinzuordnung nach seinen eigenen Kriterien fest!<br />

– Im Fenster Processes<br />

durch Klicken auf + Implement Design öffnen.<br />

– Doppelklick auf Implement Design<br />

Die Implementierung wird bis zur Erstellung des<br />

Programmierfiles durchgeführt.<br />

Es wird ein sogenannter<br />

Fitterreport erstellt und im<br />

rechten Bildschirmfenster<br />

dargestellt.<br />

Durch Klick auf die in der grau<br />

hinterlegten Spalte angegebenen<br />

Themen, gelangt man auf die<br />

jeweiligen Protokollseiten.<br />

Wichtig ist die Pin List Seite.<br />

Hier ist eine Kontrolle, ob alle<br />

vorgegebenen Pinbelegungen<br />

eingehalten werden, sinnvoll.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 18 / 37

Sie befinden sich in Schritt 3.3<br />

Implement Design<br />

(ISE)<br />

Nachfolgend werden die Dateien zur Timingsimulation erzeugt.<br />

– Im Fenster Processes: durch Klicken auf + Optional Implementation Tools öffnen.<br />

– Doppelklick auf Generate Post-Fit Simulation Model<br />

Die Dateien entityname_timesim.vhd und entityname_timesim.sdf<br />

(z,B, exor_timesim.vhd, exor_timesim.sdf)<br />

werden im Verzeichnis D:\ISE_Projects\my_project\netgen\fit für die Timing Simulation<br />

erzeugt.<br />

Weiter mit Pkt 4. ModelSim - Timingsimulation.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 19 / 37

Sie befinden sich in Schritt 3.3<br />

Implement Design<br />

(ISE)<br />

3.3.2. ISE - Implementierung für FPGA<br />

– Voraussetzung: Die Synthese ist ordnungsgemäß abgelaufen.<br />

Hinweis!<br />

Vor der Implementierung sollte unbedingt das User Constraint File my_ucf_file.ucf in<br />

das Projekt eingebunden werden, falls noch nicht geschehen.<br />

Als Mustergeneratoren stehen für das Modulare System die Files<br />

UCF-GeneratorforModSys.ods (OpenOffice/Calc) und<br />

UCF-GeneratorforModSys.xls (MS Office/Excel)<br />

auf der Laborseite http://ieweb.etech.haw-hamburg.de/yamlt3/Download.285.0.html<br />

im Downlodbereich zur Verfügung. Die Benutzung wird in den jeweiligen Files erläutert.<br />

Für das FPGA Board Spartan3 werden auf der Webseite Musterfiles zur Verfügung<br />

gestellt.<br />

Ohne Verwendung des User Constraint File legt das ISE Implementierungstool die<br />

Pinzuordnung nach seinen Kriterien fest!<br />

– Im Fenster Processes<br />

durch Klicken auf + Implement Design öffnen.<br />

– Doppelklick auf Implement Design<br />

Die Implementierung wird durchgeführt.<br />

Zu den Modulen Translate, MAP, Place & Route<br />

können Reportdateien generiert werden.<br />

Dazu ist mit der rechten Maustaste zu klicken und<br />

View Text Report auszuwählen.<br />

Die Reports werden dann im rechten Fenster<br />

angezeigt.<br />

Erzeugung der Dateien zur<br />

Timingsimulation:<br />

– Place & Route öffnen<br />

– Doppelklick auf Generate Post-Place & Route<br />

Simulation Model<br />

Die Dateien entityname_timesim.vhd und<br />

entityname_timesim.sdf<br />

(z,B, exor_timesim.vhd, exor_timesim.sdf)<br />

werden im Verzeichnis<br />

D:\ISE_Projects\my_project\netgen\par<br />

für die Timing Simulation erzeugt.<br />

Weiter mit Pkt 4. ModelSim - Timingsimulation.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 20 / 37

Sie befinden sich in Schritt 4.<br />

Timing Simulation<br />

(ModelSim)<br />

4. ModelSim - Timing Simulation<br />

Zur Timing Simulation kann das schon vorhandene ModelSim Projekt aus der<br />

funktionalen Simulation verwenden werden.<br />

Einbinden des Quellfiles entityname_timesim.vhd über<br />

– Project → Add to Project → Existing File...<br />

– Browse<br />

Für FPGA: D:/ISE_Projects/my_project/netgen/par/entityname_timesim.vhd<br />

Für CPLD: D:/ISE_Projects/my_project/netgen/fit/entityname_timesim.vhd<br />

(Beispiel: Entity-Name = EXOR ⇒ D:/ISE_Projects/my_project/netgen/<br />

par/EXOR_timesim.vhd)<br />

– Reference from current location auswählen.<br />

– OK<br />

– File wie unter Pkt. 2. beschrieben<br />

compilieren und die Simulation mit<br />

starten.<br />

Im Fenster Start Simulation den<br />

– Reiter Design öffnen<br />

– die Library work durch Klick auf +<br />

öffnen und<br />

entityname_timesim.vhd auswählen.<br />

– Reiter SDF öffnen.<br />

– Im Fenster Add SDF Entry mittels<br />

Browse die Datei<br />

entityname_timesim.sdf auswählen.<br />

Die Suchpfade sind<br />

bei CPLD's<br />

D:/ISE_Projects/my_project/netgen/fit<br />

bei FPGA's<br />

D:/ISE_Projects/my_project/netgen/par<br />

Wird eine Testbench verwendet, so ist<br />

in Apply to Region der Marker einzutragen,<br />

bei dem die Topentity des Designs in die<br />

Testbench eingebunden wird.<br />

– Klicken auf OK<br />

Der Pfad zur entityname_timesim.sdf<br />

wird ins Fenster eingetragen.<br />

– Diesen Eintrag mit der Maus markieren.<br />

– OK<br />

Die Simulation wird gestartet.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 21 / 37

Sie befinden sich in Schritt 4.<br />

Timing Simulation<br />

(ModelSim)<br />

Im Fenster Object werden nun neben den Signalen aus der port map der Top-Entity<br />

weitere Signale, die von ISE in entityname_timesim.vhd erzeugt wurden, angezeigt.<br />

– Weiter wie in „Funktionale Simulation“ Tools → TCL → Execute Macro...(Seite 8).<br />

Es kann die gleiche .do-Datei verwendet werden, wie bei der funktionalen Simulation.<br />

Dabei ist zu beachten:<br />

Falls in der .do-Datei das Kommando vsim work.xxxxx benutzt wird, ist dieses für die<br />

Timimgsimulation mit einem vorangestellten # auszukommentieren.<br />

Charakteristisch für die Wavedarstellung einer Timingsimulation sind die Zeitabschnitte der<br />

„Einschwingvorgänge“ am Anfang der Zeitskala - hier rot dargestellt -<br />

für die der Simulator noch keine<br />

definierten Werte berechnen konnte.<br />

(In der timesim.vhd wird<br />

ausschließlich der<br />

standard_logic-Datentyp verwendet,<br />

auch wenn im my_sourcefile.vhd<br />

z.B. der Datentyp „bit“ benutzt wird.)<br />

– Die Funktion ist anhand der<br />

Wavetable zu kontrollieren.<br />

Die Timingsimulation ist hiermit abgeschlossen.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 22 / 37

Sie befinden sich in Schritt 5.<br />

Generate Programming File<br />

(ISE)<br />

5. ISE - Generieren des Programmierfiles<br />

5.1. ISE - Generieren des Programmierfiles für CPLD<br />

– Im Fenster Processes:<br />

durch Klick auf + Implement Design öffnen.<br />

– Doppelklick auf<br />

Generate Programming File<br />

Es wird das JEDEC-Programmierfile<br />

entityname.jed im Projektordner erzeugt.<br />

Dies ist das Standard-Programmierfile<br />

für alle handelsüblichen Programmiergeräte.<br />

Es dient als Quellfile zur direkten<br />

Programmierung mittels des<br />

ISE-Programmiertools iMPact.<br />

5.2. ISE - Generieren des Programmierfiles für FPGA<br />

Im Fenster Processes:<br />

– Doppelklick auf Generate Programming File.<br />

Es wird das Programmierfile entityname.bit<br />

im Projektordner erzeugt. Es dient als Quellfile<br />

für das Programmiertool iMPACT.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 23 / 37

Sie befinden sich in Schritt 5.<br />

Generate Programming File<br />

(ISE)<br />

5.3. ISE - Generieren des Programmierfiles für EEPROM auf Modul Spartan3E<br />

Hintergrund:<br />

Auf dem Target Board Spartan3E des Modularen Systems befindet sich ein serielles<br />

EEPROM vom Typ Xilinx XCF04S-V020. Dieses dient zur Aufnahme der<br />

Programmierdaten für den Spartan3E, um auch einen autonomen Betrieb des FPGA<br />

zu ermöglichen.<br />

Nach Anlegen der Versorgungsspannung an das Board lädt sich der Spartan3E die<br />

Designdaten selbständig aus dem EEPROM.<br />

Ausgangspunkt für die Erzeugung des Programmierfiles für<br />

das EEPROM ist das erzeugte Programmierfile<br />

für den Spartan3E, erkennbar am grünen Häkchen bei<br />

Generate Programming File.<br />

– Durch Klick auf das + Configure Target Device öffnen<br />

– Doppelklick auf Generate Target PROM/ACE File<br />

Die Warnung mit<br />

– OK bestätigen.<br />

– Im Fenster<br />

iMPACT Flows<br />

Doppelklick auf<br />

Create PROM File<br />

(PROM File<br />

Formatter)<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 24 / 37

Sie befinden sich in Schritt 5.<br />

Generate Programming File<br />

(ISE)<br />

– Xilinx<br />

Flash/PROM<br />

durch Klick<br />

markieren.<br />

– Mit Klick auf<br />

grünen Pfeil<br />

Step 2<br />

aktivieren.<br />

– Im Step 2<br />

Fenster:<br />

– In der<br />

Auswahlbox<br />

PROM<br />

Family<br />

Platform<br />

Flash<br />

auswählen.<br />

– In der<br />

Auswahlbox<br />

Device (bits)<br />

xcf04s [4M]<br />

auswählen.<br />

– Button Add<br />

Storage<br />

Device<br />

klicken.<br />

– Grünen Pfeil rechts neben Step 2 Fenster klicken,<br />

Step 3 wird aktiviert.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 25 / 37

Sie befinden sich in Schritt 5.<br />

Generate Programming File<br />

(ISE)<br />

– In Checksum<br />

Fill Value<br />

FF eintragen.<br />

– In<br />

Output File<br />

Name<br />

einen<br />

eigenen<br />

Namen<br />

eintragen.<br />

– In<br />

Output File<br />

Location<br />

den Projektpfad<br />

eintragen.<br />

– In<br />

File Format den Value-Wert MCS auswählen.<br />

– Klick OK<br />

– Klick OK<br />

im Fenster<br />

Add Device<br />

– Auswahl des<br />

.bit-Files<br />

my_Sourcefile.bit<br />

– Open<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 26 / 37

Sie befinden sich in Schritt 5.<br />

Generate Programming File<br />

(ISE)<br />

– Klick No<br />

Es wird kein weiteres File benötigt.<br />

– Klick OK<br />

– Im Fenster iMPACT Processes Doppelklick auf Generate File...<br />

Hiermit ist das Programmierfile<br />

für das EEPROM<br />

erstellt.<br />

Zum Programmieren des<br />

PROM im Fenster<br />

iMPACT Flows<br />

Doppelklick auf Boundary<br />

Scan<br />

Zur Programmierung weiter auf Seite 36!<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 27 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

6. ISE - Programmieren des IC<br />

Wichtig!<br />

Um eine Beschädigung des Zielsystems zu vermeiden, dürfen vor der<br />

Programmierung von CPLD noch keine IC-Anschlüsse mit Quellen (z.B. Schalter,<br />

Taster, Generator usw.) verbunden sein.<br />

D.h. Es dürfen keine Module an das Bord angesteckt sein.<br />

Beim Modularen System gilt das auch für das FPGA Spartan3E, weil hier u.U. das<br />

EEPROM aktiv ist.<br />

Hintergrund:<br />

CPLD behalten die Programmierinformation auch ohne angelegte Versorgungsspannung.<br />

Die Programmierung und damit die Pinbelegung der Ausgänge ist zum Nutzungszeitpunkt<br />

nicht bekannt. Wird nun z.B. ein Schalter, der „hart“ +5V oder 0V liefert (je nach Schalterstellung<br />

und ohne Schutzwiderstand), an einen Ausgang angeschlossen, so entsteht u.U.<br />

abhängig von den Ausgangspegeln an CPLD und Peripherie ein Kurzschluss.<br />

Dieser führt dann zur Zerstörung des IC.<br />

Bei dem FPGA Spartan3E des Modularen Systems ist eine zweite Betriebsart<br />

implementiert, bei der das FPGA die Programmierdaten sofort nach Einschalten der<br />

Spannungsversorgung aus einem EEPROM lädt. Diese Daten sind ebenfalls, wie beim<br />

CPLD, von den vorherigen Nutzern implementiert worden und somit zum<br />

Nutzungszeitpunkt nicht bekannt.<br />

6.1. Vorbereitung<br />

– Anstecken des Programmierkabels mittels Flachbandkabel von Platform Cable USB II<br />

oder Parallel Cable IV an die Programmierschnittstelle des Entwicklungsboardes.<br />

– Alle Module und weitere periphere Einheiten an dem Entwicklungsboard entfernen.<br />

– Einschalten der Versorgungsspannung am Entwicklungsboard.<br />

Die gelb leuchtende Anzeige am Programmierkabel wechselt zu grün.<br />

Das zeigt an, dass eine gültige Versorgungsspannung anliegt<br />

6.2. Programmierung CPLD / FPGA (direkt über JTAG-Schnittstelle)<br />

Im Fenster Processes:<br />

– Configure Target Device öffnen<br />

– Manage configuration Project (iMPACT)<br />

durch Doppelklick starten.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 28 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

– Im Fenster<br />

iMPACT Flows<br />

Linke Maustaste Doppelklick auf<br />

Boundary Scan<br />

– Der Anweisung im Fenster folgen<br />

Right click to Add......<br />

Es öffnet sich ein Auswahlfenster<br />

– Hier Klick auf Initialize Chain<br />

Das Tool sucht nun nach<br />

Schaltkreisen in der JTAG-Kette.<br />

Wurde mindestens ein IC gefunden,<br />

öffnet sich das Fenster<br />

Auto Assign Configuration Files<br />

Query Dialog.<br />

Die Frage<br />

Do you want to continue and assign<br />

configuration file(s)?<br />

– mit Klick auf Yes bestätigen.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 29 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

– Auswählen des Programmierfiles<br />

entityname.jed für CPLD's bzw.<br />

entityname.bit für FPGA's<br />

(hier my_Sourcefile.bit für ein FPGA)<br />

– Klick auf Open.<br />

– Falls ein Spartan3-Modul programmiert werden soll, erscheint noch das Abfragefenster<br />

Attach SPI or BPI PROM, weil das Tool noch ein EEPROM gefunden hat, welches<br />

auch die Modi SPI und BPI unterstützt.<br />

Wie das EEPROM programmiert wird, ist im Pkt. 6.3 beschrieben.<br />

– Klick auf No um diese Modi zu umgehen.<br />

Jetzt wird trotzdem die Auswahl für das<br />

Programmierfile des EEPROM angeboten.<br />

Da kein File existiert, ist Bypass<br />

anzuklicken.<br />

– Das Device Programming<br />

Properties Fenster mit<br />

OK bestätigen und schließen.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 30 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

Nun wird die daisy chain<br />

der gefundenen IC's angezeigt.<br />

Das ist eine Kette der über<br />

JTAG programmierbaren IC's.<br />

Dem FPGA XC3S500e<br />

(Spartan3) ist das<br />

Programmierfile<br />

my_sourcefile.bit zugeordnet.<br />

Da für das EEPROM kein<br />

Programmierfile existiert, wird<br />

die Programmierung<br />

übergangen, so wie im<br />

vorherigen Auswahlfenster<br />

angegeben.<br />

Wird das CPLD Coolrunner<br />

Modul programmiert, ist die<br />

Kette nur mit diesem IC<br />

angezeigt.<br />

– Klick auf zu programmierendes<br />

IC. Das ausgewählte IC färbt<br />

sich grün.<br />

Durch Klick auf oder<br />

Klick rechte Maustaste → Klick<br />

Program wird die<br />

Programmierung gestartet.<br />

Im Fenster Progress Dialog wird ein Fortschrittbalken angezeigt.<br />

Mit der Meldung Program Succeeded wird die ordnungsgemäße Programmierung<br />

bestätigt.<br />

Zum Testen des Designs:<br />

– Die Spannungsversorgung für das Entwicklungsboard abschalten.<br />

– Module an die jeweiligen Buchsen anstecken, wie zu Beginn mittels ucf-File vorgegeben.<br />

– Evtl. nötige Verkabelung des Übungsaufbaues durchführen.<br />

– Die Spannungsversorgung einschalten.<br />

– Versuchsaufbau entsprechend Aufgabenstellung testen.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 31 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

6.3. Programmierung des EEPROM's für Spartan3E (Modulares System)<br />

incl. Erzeugung Programmierfile<br />

– Starten von iMPACT entsprechend<br />

6.2 (Manage configuration Project<br />

(iMPACT))<br />

– Klick Create PROM File (PROM File<br />

Formatter)<br />

– In<br />

Step 1. Select<br />

Storage Target<br />

die<br />

Speicherfamilie<br />

Xilinx<br />

Flash/PROM<br />

markieren.<br />

– Auf grünen Pfeil<br />

klicken<br />

– In Step 2 Add Storage Device(s) die PROM Family<br />

Platform Flash und das Device(bits) xcf04s [4M]<br />

auswählen.<br />

– Klick auf Add Storage Device<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 32 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

Das ausgewählte PROM wird in das<br />

Protokollfenster eingetragen.<br />

– Klick auf grünen Pfeil<br />

– Einen Dateinamen im Feld Output File Name<br />

eintragen. Alle anderen Einstellungen beibehalten<br />

bzw. auf die im Bild gezeigte Auswahl stellen.<br />

– Im Fenster PROM File Formatter Klick auf OK.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 33 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

– Im kleinen Fenster Add Device wird angezeigt,<br />

dass die Fileversion Revision: 0 erzeugt wird.<br />

– Klick auf OK<br />

– Auswählen<br />

my_source_entity.bit<br />

– Open<br />

Da in ein EEPROM mehrere unterschiedliche Programmierfiles für das selbe FPGA<br />

untergebracht werden können, wird hier auch<br />

abgefragt, ob ein weiteres bit-File zu der aktiven<br />

Revision hinzugefügt werden soll.<br />

– Klick auf No<br />

Im nächsten Fenster wird angezeigt, dass die Angaben zur Erzeugung des<br />

Programmierfiles für das EEPROM komplett ist.<br />

– Klick auf OK<br />

– Im iMPACT Processes Fenster<br />

Doppelklick auf Generate File …<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 34 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

Es wird das<br />

Programmierfile für<br />

das EEPROM als<br />

my_prom_file.mcs<br />

erzeugt.<br />

Mit Generate<br />

Succeeded wird die<br />

erfolgreiche<br />

Generierung des<br />

Files signalisiert.<br />

– Doppelklick auf<br />

Boundary Scan<br />

– Rechtsklick auf<br />

Right click to Add<br />

Device or Initialize<br />

JTAG chain<br />

– Im folgenden Fenster<br />

Initialize Chain<br />

auswählen.<br />

Es wird die daisy chain<br />

angezeigt.<br />

– Im Fenster Auto Assign<br />

Configuration Files Query<br />

Dialog auf Yes klicken.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 35 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

– Im Fenster Assign New Configuration File<br />

nicht das .bit-File auswählen sondern<br />

Bypass klicken.<br />

– Auswählen my_prom_file.mcs<br />

– Klick auf Open<br />

– Fenster Device Programming Properties<br />

mit OK bestätigen.<br />

– Klick auf IC xcf04s.<br />

Das IC färbt sich grün und ist damit ausgewählt.<br />

– Klick rechte Maustaste auf grünes IC.<br />

– Auswahl Program<br />

Das EEPROM wird mit Daten beschrieben.<br />

Die Meldung Program Succeeded zeigt an,<br />

dass der Vorgang ohne Fehler<br />

abgeschlossen wurde.<br />

Nach der Programmierung des EEPROM<br />

hat das FPGA die Daten aber noch nicht<br />

geladen.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 36 / 37

Sie befinden sich in Schritt 6.<br />

Configure Device (iMPACT)<br />

(ISE)<br />

Zur Übertragung des Designs in das FPGA sind folgende Schritte nötig:<br />

- Das Entwicklungsboard abschalten.<br />

- Am ModSys Targetboard XILINX SPARTAN3E den Schiebeschalter auf PROM stellen.<br />

- Das Board wieder einschalten.<br />

- Das FPGA liest die Daten aus dem EEPROM.<br />

Das Ende des Programmiervorganges, welcher ca. 3-4 Sekunden dauert, wird mit<br />

Aktivierung der gelben DONE LED auf dem Spartan3E Targetboard angezeigt.<br />

Das FPGA befindet sich nun im programmierten Zustand und kann wie<br />

gewünscht benutzt werden.<br />

Achtung!<br />

Bei jedem Einschalten des Systems wird das FPGA vom EEPROM neu programmiert,<br />

wenn der Schiebeschalter auf dem Targetboard XILINX SPARTAN3 auf Stellung PROM<br />

steht. Ist der Schalter versehentlich auf PROM gestellt, kann evtl. ein unbekanntes Design<br />

ins FPGA geladen werden.<br />

<strong>Anleitung</strong> ISE 10.1, ModelSim SE 6.3j / XE III 6.3c,<br />

Vers.:1.2 Stand:07.06.10/Vol<br />

Seite 37 / 37