Computerorientierte Physik VORLESUNG und Übungen

Computerorientierte Physik VORLESUNG und Übungen

Computerorientierte Physik VORLESUNG und Übungen

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Computerorientierte</strong> <strong>Physik</strong><br />

• Vorlesung<br />

<strong>VORLESUNG</strong> <strong>und</strong> <strong>Übungen</strong><br />

Zeit:<br />

Ort:<br />

Mo., 10.15 – 11.45 Uhr<br />

Hörsaal 5.01, Institut für <strong>Physik</strong>,<br />

Universitätsplatz 5, A-8010 Graz<br />

• <strong>Übungen</strong>: als Projektarbeiten in Gruppen (ca. 5 Studierende)<br />

allg. Besprechung nach der Vorlesung (11.45-12.00 Uhr)<br />

detaillierte Projektbesprechungen: wöchentlich ca. 1 St<strong>und</strong>e,<br />

Vereinbarung mit jeder Projektgruppe einzeln.

Gr<strong>und</strong>lagen der Hardware<br />

• Die wichtigsten Hardwaregruppen<br />

• Kommunikation über Daten-, Control- <strong>und</strong><br />

Adressbus<br />

• Aufbau des Memory<br />

• Einige Schnittstellen (parallel, seriel)<br />

• Aufbau der Prozessorbefehle

Gr<strong>und</strong>lagen<br />

Hardwaregruppen <strong>und</strong> ihre Kommunikation<br />

Memory<br />

Peripherie<br />

Clock Interrupt DMA PIA SIA<br />

CPU<br />

Daten Bus<br />

Control Bus<br />

Adress Bus

Memory<br />

RAM: Random Access Memory<br />

statisch: Flip-Flop<br />

dynamisch: (Ladung eines Kondensators) refresh<br />

Datenbreite:<br />

1-Bit<br />

1-Byte (8 Bit), unteres/oberes Halbbyte(4 Bit)<br />

1-Word (16 Bit)<br />

double Word (32 Bit)<br />

quad Word (64 Bit)<br />

Adressierung: Speicherchips unterschiedlicher Organisation<br />

(1Bit x 64k, 8Bit x 8k)<br />

Ansprechen über Adressbus, Chip-Select (CS)<br />

<strong>und</strong> Read-Write (RW) Signale

Memory Organisation 8 x 32k<br />

8-Bit bidirektionaler Datenbus (Tri-State-Buffer)<br />

CS<br />

8 x 8k<br />

8 x 8k<br />

CS<br />

CS<br />

8 x 8k 8 x 8k<br />

A0-A12<br />

Adressbus<br />

Enable, R/W<br />

A0-A12<br />

Enable, R/W<br />

A0-A12<br />

Enable, R/W<br />

A0-A12<br />

Enable, R/W<br />

Codierung<br />

CS<br />

A13-A14<br />

Controlbus

Memory Management<br />

Aufgabe: Verwaltung des Speichers, virtueller Speicher<br />

Speichermodelle: flacher-, segmentierter-, virtueller Adressraum<br />

Einteilung:<br />

Segmente (Selektor, Offset, Descriptor)<br />

abh. ob Real-Mode oder Protected Mode<br />

Code-Segmente<br />

Daten-Segmente<br />

Stack-Segmente<br />

Paging (DIR, TABLE,OFFSET)<br />

DIR: Page Directory<br />

TABLE: Page table<br />

OFFSET: Adresse in der Page (4kB)

Peripherie<br />

Memory mapped:<br />

Vorteil: Adressierung wie Memory<br />

großer Adressierraum<br />

alle Adressierungsarten der CPU<br />

Nachteil: schlechte Strukturierung,<br />

höhere Anforderungen an Systemdesign<br />

(Memory Management)<br />

Eigene I/O Adressierung: (Input/Output)<br />

Vorteil: Übersichtliches Systemdesign<br />

Spezifische Hardwarebehandlung<br />

Nachteil: Mehr Aufwand für CPU<br />

Eigene Befehle, mehr Signalleitungen

Interrupt System<br />

Aufgabe: Beeinflussung des Programmablaufes durch<br />

äußere Ereignisse.<br />

NMI: non maskable Interrupt:<br />

nicht vom Programm ignorierbarer Interrupt<br />

z.B. Reset<br />

MI: maskable Interrupt<br />

vom Programm kann entschieden werden,<br />

ob Interrupt ermöglicht werden soll.<br />

z.B. Tastaturbetätigung<br />

Interrupt Controller: intelligenter Baustein<br />

Maskierung einzelner Interrupts, Prioritäten,<br />

Kaskadierbar

DMA: Direct Memory Access<br />

Aufgabe: Externer schreib-lese-Zugriff aufs Memory<br />

Ablauf: Nach Anforderung Stillstand der CPU<br />

Freigabe von Adress-, Daten- <strong>und</strong> Controlbus<br />

Übernahme der externen Kontrolle<br />

Anwendung: schnellere externe Hardware (früher)<br />

(Multiprozessor Anwendungen)<br />

Controller: Intelligenter Baustein<br />

Maskierbar, Kaskadierbar, ähnlich Interruptcontroller

PIA: Parallel Interface Adapter<br />

Aufgabe: Übergang vom internen Bussystem auf externe<br />

mehr-Bit (8 Bit, 16 Bit) Datenverbindung<br />

z.B. parallele Druckerverbindung<br />

Controller: Intelligenter Baustein<br />

individuelle uni-direktionale <strong>und</strong> bidirektionale<br />

Programmierung einzelner Leitungen<br />

Hand-shake-logik

LPT Ports<br />

(IEEE 1284)<br />

8 bit Data Leitungen (Ausgänge, bidirektional)<br />

5 bit Status Leitungen (Eingänge)<br />

4 bit Control Leitungen (Ausgänge)<br />

LPT Versionen: Standard<br />

PS/2 (bidirektional)<br />

Enhanced Parallel Port (EPP) (neu Control, Adressierung)<br />

Extended Capability Port (ECP) (bis128 Geräte, Kompr.)<br />

25 pin Sub-D Buchsenleiste<br />

2-9 Data, 18-25 gro<strong>und</strong>, ca. 2,5mA<br />

Basis Adresse (Data): 3BC (LPT1:) 378 (LPT2:) 278 (LPT3:)<br />

Status: 3BD 379 279<br />

Control: 3BE 37A 27A

SIA: Seriel Interface Adapter<br />

Aufgabe: Verbindung des internen Busses zu externer<br />

1-Bit serieller Leitung<br />

z.B. RS232 (COM1:, COM2:, etc.)<br />

USB,<br />

Controller: Intelligenter Baustein<br />

Baudrate, Stop-Bits, Synchronisation, Parity<br />

Hand-shake Leitungen (Hardware, Software)

COM Schnittstelle (RS-232)<br />

9 pol. Sub-D Steckerleiste<br />

1: in DCD (Data Carrier Detect)<br />

2: in RxD (Recieve Data<br />

3: out TxD (Transmit Data)<br />

4: out DTR (Data Terminal ready)<br />

5: gro<strong>und</strong><br />

6: in DSR (Data set ready)<br />

7: out RTS (Request to send)<br />

8: in CTS (Clear to send)<br />

9: in RI (Ring indicator)<br />

(25 pol. Sub-D Steckerleiste)<br />

Spannung: -12V ..... +12V<br />

Schwelle: ~ 1,1V<br />

Strombegrenzt:~ 10mA-20mA<br />

Eingangswiderstand: ~ 10kΩ

Central Processor Unit (CPU)<br />

Registers<br />

Arithmetic/Logic<br />

Unit (ALU)<br />

Execution-<br />

Control<br />

Interface<br />

Floating Point<br />

Unit (FPU)

Prozessorarten nach Aufbau<br />

• Auf mehrere elektronische Bauteile (<strong>und</strong> Platinen)<br />

verteilt (Großrechner)<br />

• Integriert auf einem Chip: Microprozessoren,<br />

Microcontroler (+Memory <strong>und</strong> Peripherie),<br />

DSP‘s (Digitale So<strong>und</strong> Prozessoren) (SpezialCPU‘s)

Prozessorbefehle<br />

Rechenbefehle: AND, OR, ADD, TEST, CMP, NOP<br />

Datenverschieben: MOV, POP, PUSH, IN, OUT,<br />

Kontrollbefehle: JMP, CALL, INT, RET, IRET, LOOP<br />

als unbedingte <strong>und</strong> bedingte Verzweigungen<br />

RISC: Reduced instruction set<br />

(besonders schnelle optimierte CPU´s)<br />

(1 Befehl pro Taktzyklus)<br />

DSP: Digitale Signal Prozessoren: besonders schnelle realtime<br />

Verarbeitung von Sprache, Musik, Video (oft nur 1 Bit Daten)<br />

Beispiel: Befehlsaufbau bei Standard Pc: Intel 80xxx<br />

Prefix Code1 Code2 Daten Daten

Adressierungsarten<br />

Register-Adressierung<br />

Memory-Adressierung: direkte, indirekte, indizierte<br />

Indiziert:<br />

Basis<br />

Index<br />

x Skalierung +<br />

Displacement

Register<br />

Rechenregister: AX, BX, CX, (AH, AL, EAX, etc.)<br />

Indexregister: BP, SI, DI, SP<br />

Flagregister: oder Statusregister<br />

Instruction Pointer<br />

Segment Register: für Memory Management<br />

Control Register: z.B. für Paging

ALU-Geschwindigkeit von Prozessoren<br />

CPU - ALU<br />

Intel Celeron 433MHz 128L2/Intel 810E PC100 CL2 SDRAM<br />

Intel Celeron 2.0GHz 128L2 bat./Acer Inc 82845MP PC2100 CL2.5 DDR<br />

Intel Celeron 2.0GHz 128L2 net./Acer Inc 82845MP PC2100 CL2.5 DDR<br />

Intel P4 2.0GHz 256L2/Intel 845D PC2100 CL2.5 DDR<br />

AMD Athlon XP3000+ 2.16GHz 512L2/VIA KT400 PC3200U CL2.5 DDR<br />

Intel P4-B [2 SMT] 3.06GHz 512L2/Intel 865 2xPC3200 CL2 DDR<br />

8000<br />

6000<br />

4000<br />

2000<br />

0<br />

Performance [MIPS]<br />

Konfiguration

FPU Geschwindigkeit von Prozessoren<br />

Intel Celeron 433MHz 128L2/Intel 810E PC100 CL2 SDRAM<br />

Intel Celeron 2.0GHz 128L2 bat./Acer Inc 82845MP PC2100 CL2.5 DDR<br />

Intel Celeron 2.0GHz 128L2 net./Acer Inc 82845MP PC2100 CL2.5 DDR<br />

Intel P4 2.0GHz 256L2/Intel 845D PC2100 CL2.5 DDR<br />

AMD Athlon XP3000+ 2.16GHz 512L2/VIA KT400 PC3200U CL2.5 DDR<br />

Intel P4-B [2 SMT] 3.06GHz 512L2/Intel 865 2xPC3200 CL2 DDR<br />

6000<br />

4000<br />

2000<br />

0<br />

CPU - FPU<br />

Performance [MFLOPS]<br />

Konfiguration

Übertragungsgeschwindigkeit CPU-RAM<br />

heutiger Pc‘s<br />

Intel Celeron 433MHz 128L2/Intel 810E PC100 CL2 SDRAM<br />

Intel Celeron 2.0GHz 128L2 bat./Acer Inc 82845MP PC2100 CL2.5 DDR<br />

Intel Celeron 2.0GHz 128L2 net./Acer Inc 82845MP PC2100 CL2.5 DDR<br />

Intel P4 2.0GHz 256L2/Intel 845D PC2100 CL2.5 DDR<br />

AMD Athlon XP3000+ 2.16GHz 512L2/VIA KT400 PC3200U CL2.5 DDR<br />

Intel P4-B [2 SMT] 3.06GHz 512L2/Intel 865 2xPC3200 CL2 DDR<br />

5000<br />

4000<br />

3000<br />

2000<br />

1000<br />

0<br />

CPU - Memory<br />

Übertragungsgeschwindigkeit [MB/s]<br />

Konfiguration

Übertragungsgeschwindigkeit abhängig von<br />

Blockgröße heutiger Pc‘s<br />

CPU - Memory<br />

Übertragungsgeschwindigkeit [MB/s]<br />

10000<br />

1000<br />

Netzbetrieb<br />

Akkubetrieb<br />

2 1 2 2 2 3 2 4 2 5 2 6 2 7 2 8 2 9 2 10 2 11 2 12 2 13 2 14 2 15 2 16<br />

Blockgröße [kB]

Transferrate heutiger Festplatten<br />

50000<br />

Festplatte<br />

ATA33 5.4kRpm 512kB 10GB FAT16 Win9x<br />

ATA-5 4.2kRpm 40GB FAT32 WinXP bat.<br />

ATA-5 4.2kRpm 40GB FAT32 WinXP net.<br />

ATA150 7.2kRpm 2MB 120GB NTFS WinXP<br />

ATA100 2xRaid 7.2kRpm 8MB 80GNTFS WinXP<br />

SCSI U320 15kRpm 8MB 147GB NTFS WinXP<br />

40000<br />

30000<br />

20000<br />

10000<br />

0<br />

Transferrate [kB/s]<br />

Konfiguration

Preisentwicklung<br />

CPU Celeron 2GHz

Preisentwicklung Memory 256MB

Preisentwicklung Festplatte 40GB

Miniaturisierung in der<br />

Halbleitertechnologie<br />

1. Moore´sche Gesetz (G.Moore, IEDM Tech. Dig.11, 1975)<br />

10 -2<br />

10 -3<br />

10 -4<br />

1. Moore´sches Gesetz<br />

Daten von Prozessoren<br />

Abmessung [m]<br />

10 -5<br />

10 -6<br />

10 -7<br />

10 -8<br />

10 -9<br />

10 -10<br />

10 -11<br />

J.Birnbaum, R.S.Williams in Phys.Today 53, 38(2000)<br />

http://www.aip.org/web2/aiphome/pt/vol-53/iss-1/captions/p38cap3.html<br />

1960 1970 1980 1990 2000 2010 2020 2030 2040<br />

Jahr

Miniaturisierung in der<br />

Halbleitertechnologie<br />

2. Moore´sches Gesetz (G.Moore, 1975)<br />

10 5<br />

10 4<br />

10 3<br />

Markt<br />

Investitionen<br />

2.Moore´sches Gesetz<br />

Milliarden US$<br />

10 2<br />

10 1<br />

10 0<br />

10 -1<br />

10 -2<br />

10 -3<br />

J.Birnbaum, R.S.Williams in Phys.Today 53, 38(2000)<br />

http://www.aip.org/web2/aiphome/pt/vol-53/iss-1/captions/p38cap4.html<br />

1960 1970 1980 1990 2000 2010 2020 2030 2040<br />

Jahr

Wirtschaftliche Grenzen<br />

Erzielbarer Gewinn:<br />

Markt − Invest.<br />

Gewinn[%] =<br />

• 100%<br />

Markt<br />

100<br />

80<br />

Gewinn [%]<br />

60<br />

40<br />

20<br />

0<br />

1960 1970 1980 1990 2000 2010 2020 2030 2040<br />

Jahr

Grenzen konventioneller<br />

Halbleitertechnologie<br />

K.L.Wang, J.Nanosci.Nanotech. 2002, 2, 235

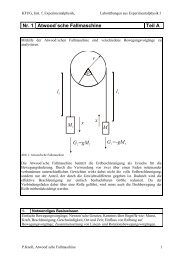

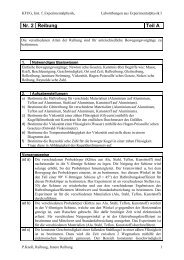

<strong>Übungen</strong>: Projekte<br />

• STM: Bildaufnahme, Mo. 12 - 13 Uhr<br />

• Computersteuerung eines Modellfahrzeuges<br />

Mi. 11 - 12<br />

• Segelboot: Datenerfassung von GPS <strong>und</strong><br />

Echolot, Di. 11 – 13 Uhr<br />

• Automatische Erfassung des Lichteinfalles <strong>und</strong><br />

Kontrastregelung eines Displays,<br />

Mi. 15 – xx Uhr