Paper (PDF) - STS - TUHH

Paper (PDF) - STS - TUHH

Paper (PDF) - STS - TUHH

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Bachelorarbeit<br />

Marcel Heing-Becker<br />

Bitfehlerinjektionen in Register<br />

auf der Basis von FITIn<br />

24. Juni 2013<br />

betreut durch:<br />

Prof. Dr. Sibylle Schupp<br />

Hamburg University of Technology (<strong>TUHH</strong>)<br />

Technische Universität Hamburg-Harburg<br />

Institute for Software Systems<br />

21073 Hamburg

Eidesstattliche Erklärung<br />

Ich, Marcel Heing genannt Becker, versichere an Eides statt, dass ich die vorliegende Bachelorarbeit<br />

mit dem Titel Bitfehlerinjektionen in Register auf der Basis von FITIn selbstständig<br />

verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet<br />

habe. Diese Arbeit wurde in dieser oder ähnlicher Form bisher keiner anderen Prüfungskommission<br />

vorgelegt.<br />

Hamburg, den 24. Juni 2013<br />

(Unterschrift)<br />

Marcel Heing genannt Becker <br />

Matrikelnummer: 21046393<br />

Studiengang: Computational Informatics B. Sc.<br />

iii

Inhaltsangabe<br />

Mit FITIn wurde ein Valgrind-basiertes Werkzeug geschaen, das in einem Zielprogramm<br />

einen Bitfehler vornimmt. Zu diesem Zweck wurden bisher Ladeoperationen aus dem Prozessspeicher<br />

überwacht. Vor einer vom Anwender gewählten Ladeoperation führte FITIn<br />

an der Ladeadresse einen Bit-Flip durch. Dieses Prinzip verhinderte jedoch, dass der Benutzer<br />

vor Lesezugrien auf Registern etwa wenn ein Wert für mehrere Operationen in<br />

einem Register gehalten wird einen Fehler in diese injizieren konnte.<br />

Im Rahmen dieser Arbeit wird FITIn auf die Erweiterbarkeit für diesen Anwendungsfall<br />

untersucht. Dazu wird das Feld der Fehlerinjektion von einem höheren Standpunkt aus<br />

betrachtet, um FITIn in seinen theoretischen Fähigkeiten einordnen zu können. Es wird<br />

eine Implementierung vorgestellt, die einen Bitfehler nicht mehr vor der Ladeoperation<br />

sondern vor der Verwendung eines relevanten Werts vornimmt. Auf diese Weise kann der<br />

Benutzer von einer gröÿeren Transparenz bei der Verwendung von FITIn protieren.<br />

Die erweiterte FITIn-Version wird etlichen Analysen zur Anwendbarkeit und Performance<br />

unterzogen, die die Stärken und Schwächen demonstrieren. Insbesondere die Verwendung<br />

von Valgrind verdient zusätzliche Aufmerksamkeit, da das Framework etliche Vor-,<br />

aber auch Nachteile mit sich führt. Auÿerdem werden andere Konzepte zur Fehlerinjektion<br />

in Register vorgestellt und mit FITIn verglichen.<br />

Abstract<br />

FITIn is a Valgrind-based tool created for performing a bit error in a target application. So<br />

far, loading operations from the memory have been monitored to schedule error injections.<br />

Given a user-selected load operation, FITIn ipped a single bit on the memory at runtime.<br />

Doing it this way, the user faced a limitation if a value was not reloaded from the memory<br />

but remained inside a register. This potentially reduced the granularity for choosing a<br />

time when to perform a bit ip.<br />

This work focuses on extending FITIn to allow such a use case. By a more comprehensive<br />

look at the domain of fault injection, the position of FITIn will be highlighted.<br />

An implementation will be presented that moves the bit error injection from pre-load to<br />

pre-use time. This makes the user gain transparency when working with FITIn.<br />

The new version of FITIn is subject to multiple analyses regarding usability and performance.<br />

These analyses reveal strengths and weaknesses of FITIn. Valgrind deserves<br />

some attention in particular as this framework implies both benets and diculties for<br />

tools on top of it. Other approaches for injecting bit errors into registers will be presented<br />

and compared to FITIn.<br />

v

Inhaltsverzeichnis<br />

1 Einführung 1<br />

1.1 Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1<br />

1.2 Problembeschreibung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1<br />

2 Fehlerinjektion 3<br />

2.1 Methoden . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3<br />

2.2 Anwendungsfälle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5<br />

2.3 Injektionsebenen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6<br />

2.3.1 Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6<br />

2.3.2 Betriebssystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6<br />

2.3.3 Virtuelle Maschine . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6<br />

2.3.4 Kompilierungszeit . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7<br />

2.3.5 Programm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7<br />

3 Erweiterung von FITIn 9<br />

3.1 Dynamische Binärinstrumentierung . . . . . . . . . . . . . . . . . . . . . . . 9<br />

3.2 Valgrind . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10<br />

3.2.1 Allgemeines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10<br />

3.2.2 Instrumentierung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10<br />

3.2.3 VEX IR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12<br />

3.3 FITIn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15<br />

3.4 Registerbehandlung in Valgrind . . . . . . . . . . . . . . . . . . . . . . . . . 16<br />

3.5 Evaluierung von Ansätzen . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17<br />

3.6 Erweiterung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19<br />

3.6.1 Betrachtete Operationen . . . . . . . . . . . . . . . . . . . . . . . . . 20<br />

3.6.2 Instrumentierungszeit . . . . . . . . . . . . . . . . . . . . . . . . . . 21<br />

3.6.3 Ausführungszeit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24<br />

3.6.4 float, double und weitere Datentypen . . . . . . . . . . . . . . . . . 26<br />

3.6.5 Systemaufrufe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28<br />

4 Evaluierung von FITIn 31<br />

4.1 Analyse von Testfällen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31<br />

4.2 FlipSafe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38<br />

4.3 Performance-Strafe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40<br />

4.4 Speicherbedarf . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43<br />

4.5 Zwischenfazit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44<br />

5 Konkurrierende Ansätze 47<br />

5.1 Programme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47<br />

5.2 DBI-Frameworks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48<br />

5.3 Vergleichsfazit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50<br />

vii

6 Abschluss 51<br />

6.1 Zusammenfassung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51<br />

6.2 Ausblick . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52<br />

Literaturverzeichnis 53<br />

Akronyme 55<br />

Abbildungsverzeichnis 57<br />

Anhang A Ergänzendes Material 59<br />

A.1 VEX IR-Spezikation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59<br />

A.2 Instrumentierungsbeispiel . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60<br />

Anhang B FITIn 65<br />

B.1 Benutzung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65<br />

B.2 Problembehandlung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67<br />

viii

1 Einführung<br />

1.1 Motivation<br />

Es existieren Einüsse auf die Ausführung von Software, die nicht durch diese selbst, nicht<br />

durch eine ausführende virtuelle Maschine und nicht durch die Spezikation der darunterliegenden<br />

Hardware bedingt sind: Sowohl ein Defekt der Hardware als auch Ionenstrahlung<br />

oder elektromagnetische Interferenzen, die in Wechselwirkung mit einer Bitrepräsentation<br />

treten, gehören zu diesen Faktoren. Ein mögliches Resultat ist die Umkehrung eines Bits<br />

[1, S.3f]. In einem günstigen Fall wird ein sogenannter Bit-Flip unbemerkt bleiben, im<br />

unglücklichsten Fall einen Systemabsturz herbeiführen.<br />

Gegenmaÿnahmen, einen solchen Bit-Flip im Datenbereich zu erkennen und auch zu<br />

korrigieren, nden sich sowohl in Hardware, etwa bei Arbeitsspeicher mit ECC-Fähigkeit,<br />

als auch in Software, etwa durch redundante Speicherung von Daten. Softwareverfahren zur<br />

Behandlung dieser Fälle werden Softwareimplementierte Hardwarefehlertoleranz (SIHFT)-<br />

Techniken genannt [2, S.841].<br />

Seitens eines Entwicklers mag die Motivation bestehen, Analyse- und Testverfahren zu<br />

verwenden, die Bitfehler in der zu untersuchenden Software verursachen: zum systematischen<br />

Analysieren der Auswirkung auf die Ausführung, zum Testen von SIHFT-Techniken<br />

oder zur Beobachtung der Stabilität von numerischen Algorithmen.<br />

Ein derartiges Testverfahren setzt sich insofern von bekannten Techniken wie Blackund<br />

Whitebox-Tests oder Fuzzing ab, dass der Entwickler einen anderen Weg zur Beein-<br />

ussung der Ausführung einschlagen muss: Etwa durch manuelles Nachstellen eines solchen<br />

Falls im Quell- oder Binärcode, oder durch eine äuÿere Komponente, die auf das Programm<br />

Einuss nehmen kann. Weiterhin mag der Auftritt eines Bit-Flips deterministisch oder stochastisch<br />

gewünscht sein. Andere Anforderungen ergeben sich aus dem Ort, zum Beispiel<br />

ob im Arbeitsspeicher oder in einem CPU-Register, und der Zeit der Manipulation, um<br />

beispielsweise eine bestimmte Iteration oder Rekursionstiefe abzuwarten.<br />

FITIn ist in seiner Ursprungsform ein für das Ausführungs- und Instrumentierungs-<br />

Framework Valgrind entworfenes Plug-In, das dem Benutzer bei Vorlage des Quellcodes<br />

in C/C++ ermöglicht, einen Bit-Flip auf einem gewählten Bit zur Ausführungszeit vor<br />

einem gewählten Lesevorgang auf dem Speicher herbeizuführen. Im Vergleich zum manuellen<br />

Vorgehen macht es FITIn dem Benutzer einfacher, ein anderes Bit und einen anderen<br />

Zeitpunkt zu wählen.<br />

1.2 Problembeschreibung<br />

Die ursprüngliche Fassung von FITIn beschränkt sich darauf, einzig Lesezugrie auf den<br />

Prozessspeicher zu erkennen und zum Abwarten des Flip-Zeitpunkts zu verwenden. Das<br />

grundsätzliche Vorgehen bei der Benutzung sieht dabei wie folgt aus:<br />

Bei Einsicht des Quellcodes entscheidet sich der Benutzer für eine oder mehrere Variablen,<br />

die er für einen Bit-Flip in Betracht ziehen möchte. Dazu setzt er ein vorgegebenes<br />

C-Makro nach der Deklarierung der Variablen. Nach einer erneuten Kompilierung<br />

1

1 Einführung<br />

des Quellcodeabschnitts lässt sich das Programm sowohl wie gewohnt als auch für FITIn<br />

benutzen.<br />

Valgrind erkennt anhand des durch das Makro erweiterten Stacks, dass eine Client-<br />

Anfrage an FITIn gerichtet ist. FITIn erhält von einer Variablen die Startadresse sowie<br />

deren Gröÿe in Bytes und fügt diese Daten der eigenen Erkennungsliste hinzu. Weiterhin<br />

erhält FITIn von Valgrind eine Zwischenrepräsentation des auszuführenden Binärcodes,<br />

aus der sich Zugrie auf den Speicher erkennen lassen und die sich zur Erzeugung von<br />

Bit-Flips manipulieren lässt. Durch Maÿnahmen wird jeder relevante Lesezugri gezählt<br />

und zum gewählten Zeitpunkt das gewählte Bit im Prozessspeicher invertiert, bevor die<br />

Variable im Rahmen des ursprünglichen Programmusses aus dem Prozessspeicher gelesen<br />

wird.<br />

Auf vielen Prozessorarchitekturen werden Daten jedoch nicht vor jeder Benutzung<br />

erneut aus dem Speicher in ein CPU-Register geladen: In Abhängigkeit der Zielplattform<br />

führt der Compiler eine Analyse zur Registerallokation durch. Schlieÿlich verlangen gewisse<br />

CPU-Instruktionen, dass sich die Operanden in einem Register benden. Durch geschickte<br />

Anordnung der Instruktionen lassen sich Daten so lange wie möglich im Register halten,<br />

bevor diese in den Arbeitsspeicher ausgelagert oder zurückgeschrieben werden [3, S.101f].<br />

Dadurch werden nicht nur Lade- und Speicherinstruktionen eingespart, sondern auch der<br />

tatsächliche Transfervorgang in ein deutlich langsameres Speichermedium und der aus diesem<br />

hinaus.<br />

Stellt man FITIn dieser Tatsache entgegen, erkennt man die Lücke, die sich durch<br />

fehlendes Beobachten von Registerallokationen und -zugrien auftut. Im Rahmen dieses<br />

Dokuments wird untersucht, inwieweit das bestehende FITIn für diese Aufgabe erweitert<br />

werden kann. Dabei werden nicht nur verschiedene Ansätze verfolgt und eine Implementierung<br />

vorgestellt (Kapitel 3), sondern auch die Fehlerinjektion im weiteren Sinne betrachtet<br />

(Kapitel 2). Es wird darüber hinaus auf konkurrierende Ansätze eingegangen (Kapitel 5)<br />

um die Vorteile und Grenzen von FITIn und Valgrind auszuloten. In der Evaluierung wird<br />

FITIn verschiedenen Anwendungstests unterzogen und auf Fähigkeiten und Einschränkungen<br />

untersucht. Im Sinne der ursprünglichen Entwicklung wird FITIn erneut dazu benutzt,<br />

eine SIHFT-Bibliothek auf die Probe zu stellen. Auch über die Performance und<br />

über den Speicherverbrauch von FITIn werden Einschätzungen gegeben (Kapitel 4).<br />

2

2 Fehlerinjektion<br />

Das Injizieren von Fehlern in ein Programm ist auf verschiedene Art und Weise möglich und<br />

auf verschiedenen Ebenen der Hard- und Software realisierbar. In diesem Kapitel werden<br />

potentielle Möglichkeiten aufgezeigt und kurz erörtert.<br />

2.1 Methoden<br />

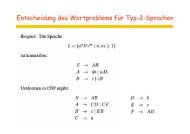

Den Spezialfall der Fehlerinjektion in Register vorerst auÿer Acht gelassen, erönen sich<br />

unterschiedliche Herangehensweisen, Einuss auf die Ausführung eines Programms zu erlangen.<br />

Grundsätzlich sind diese in hard- und softwarebasierte Methoden aufzuteilen. Die<br />

Abbildung 2.1 erlaubt einen Überblick über die Einordnung von Fehlerinjektionsmethoden<br />

[4, S.76].<br />

Hardwarebasiert<br />

Kontaktbasiert<br />

Tastkopf<br />

Sockel<br />

Fehlerinjektion<br />

Kontaktlos<br />

Vor Ausführung<br />

Softwarebasiert<br />

Zeitnehmer<br />

Zur Ausführungszeit<br />

Ausnahme<br />

Abbildung 2.1: Taxonomie der Fehlerinjektion<br />

Instrumentierung<br />

Hardwarebasierte Fehlerinjektion<br />

Die Manipulation von Hardware erfordert zusätzliche Hardware sowie die Fähigkeit, in<br />

ausreichend kurzer Zeit herbeigeführte Fehler und deren Folgen erkennen zu können. Die<br />

hardwarebasierte Fehlerinjektion teilt sich in zwei Untergruppen auf:<br />

• Kontaktbasierte Fehlerinjektion: Eine Möglichkeit besteht darin, einen Hardware-Pin<br />

mit einem aktiven Tastkopf zu berühren. Für die Dauer wird die Spannung an diesem<br />

verändert, sodass die Auösung des Signals auf den gewünschten Wert eingerastet<br />

wird. Komplexere Manipulationen lassen sich durch Sockelung der Hardware vornehmen:<br />

So können zusätzlich mittels integrierter Logikgatter oder Schaltwerke die<br />

Eingangssignale den Manipulationsanforderungen entsprechend angepasst werden.<br />

3

2 Fehlerinjektion<br />

• Kontaktlose Fehlerinjektion: Durch den Beschuss der Hardware mittels Ionen [5] oder<br />

durch elektromagnetische Interferenzen [6] können Bitrepräsentationen umgekehrt<br />

werden. Dieses Vorgehen ist mit Einbuÿen in der Präzision in Bezug auf Zeit und<br />

Ort sowie der Wiederholbarkeit verbunden, es erlaubt jedoch eine Beobachtung der<br />

Funktionsfähigkeit der Hardware in realen Strahlungsverhältnissen und elektrischen<br />

Kongurationen.<br />

Softwarebasierte Fehlerinjektion<br />

Im Vergleich zu hardwarebasierten Fehlerinjektionen stellen softwarebasierte Lösungen<br />

einen geringeren Kostenfaktor dar, und auch die Implementierung einer Fehlerinjektionssemantik<br />

ist exibler realisierbar. Natürliche Grenzen sind der Software im Rahmen dessen<br />

gesetzt, wie diese im Besitz von Hardwarezugrien ist: Eine Manipulation des Arbeitsspeichers<br />

vorbei an einem Paritätsbit, das Teil eines hardwarebasierten elektronischen Korrekturcodes<br />

(ECC) ist, ist daher zum Beispiel unmöglich. Man unterscheidet zwischen zwei<br />

Injektionsszenarien:<br />

• Vor der Ausführungszeit: An einem Zeitpunkt, bevor das Programm zur Ausführung<br />

in den Arbeitsspeicher geladen ist. In Frage kommen manuelle Anpassungen<br />

des Quellcodes, eine Compiler-Direktive oder die Manipulation des generierten Binärcodes.<br />

Letzteres ordnet sich in die statische Binärinstrumentierung ein [7, S.3].<br />

• Zur Ausführungszeit: Ist das Programm bereits als Prozess aktiv, bieten sich andere<br />

Methoden zur Fehlerinjektion an: Die des ablaufenden Zeitnehmers, die der Ausnahmebehandlung<br />

und die der Code-Instrumentierung. Betrachtet man den Ausführungs-<br />

Stack eines Programms, können diese Fehlerinjektoren ab der Betriebssystemebene<br />

sinnvoll implementiert werden.<br />

• Ablaufender Zeitnehmer: Ein hard- oder softwarebasierter Zeitnehmer erzeugt<br />

bei Ablauf einen Interrupt 1 . Eine auf diesen Interrupt gesetzte Callback-Methode<br />

ist daraufhin in der Lage, eine Fehlerinjektion im Programm vorzunehmen. Die<br />

Präzision dieser Methode ist begrenzt, da der Zeitablauf zum Beispiel durch<br />

variable E/A-Operationen, auf die die CPU wartet, unvorhersehbar eintreten<br />

kann.<br />

• Ausnahmebehandlung: Sowohl ein softwarebedingtes Ausnahmeereignis, das vom<br />

Programm vor der Ausführung des nachfolgenden Codeabschnitts ausgelöst<br />

wird, als auch ein Hardwareereignis können dazu verwendet werden, zu ausgewählten<br />

Zeitpunkten eine Fehlerinjektion vorzunehmen, sofern zuvor eine entsprechende<br />

Callback-Prozedur registriert wurde.<br />

• Code-Instrumentierung: Zur Laufzeit des Programms verfügt die fehlerinjizierende<br />

Softwarekomponente über das Wissen, welche Instruktion als nächstes<br />

ausgeführt wird und kann gegebenenfalls Instruktionen hinzufügen, die der Fehlerinjektion<br />

dienlich sind. Der wesentliche Vorteil liegt dabei darin, dass eine Injektionssemantik<br />

ungleich komplexer als in anderen Softwareansätzen gewählt<br />

werden kann. Die Schwierigkeit bei diesem Ansatz ist dagegen, dass das instrumentierende<br />

Programm mit dem ausgeführten Zielprogramm nicht weiter<br />

in Konikt treten darf, etwa durch Blockierung von Ressourcen oder durch<br />

Veränderung der denotationellen Semantik [8, S.266]. Allgemein, also nicht auf<br />

Fehlerinjektionen begrenzt, nennt man dieses Vorgehen dynamische Binärinstrumentierung<br />

(DBI) [7, S.3].<br />

1 Deutsch: Unterbrechung<br />

4

2.2 Anwendungsfälle<br />

2.2 Anwendungsfälle<br />

Binärfehler lassen sich in mehreren Formen und Auftrittsmustern konstruieren. Betrachtet<br />

man ein einzelnes Bit, so ergeben sich folgende Fehlfunktionsszenarien:<br />

• Bit-Flip: Ein Hardwaredefekt oder ein Umwelteinuss kehrt die Bitrepräsentation<br />

temporär um. Ist ein Bit-Flip strahlungsbedingt, so spricht man von einem Single<br />

Event Upset (SEU) [5, S.1].<br />

• Bit-Einrastung: Das Bit lässt sich nicht mehr aktualisieren, es verbleibt im Zustand<br />

0 oder 1. Dies kann einem Hardwaredefekt entsprechen, etwa degeneriertem Arbeitsspeicher.<br />

• Flüchtiges Bit: Ein Speichermedium verliert seine Integrität, sodass zeitlich versetzte<br />

Lesezugrie einen anderen Zustand zurückliefern können, aber nicht müssen [9,<br />

S.116]. Ein solches Verhalten lässt sich mittels einer Veränderungsfrequenz oder einer<br />

Zustandswahrscheinlichkeit bei Lesezugrien beschreiben.<br />

In diesem Dokument werden ausschlieÿlich Binärfehler betrachtet, die im Bezug zur<br />

Zustandsspeicherung stehen, dazu zählen CPU-Register und -Caches, der Arbeitsspeicher<br />

(RAM) und der Sekundärspeicher. Ausdrücklich ausgeschlossen seien Übertragungsfehler<br />

jeglicher Art.<br />

Möchte man die Auswirkung von Bitfehlern auf den Programmuss untersuchen, so<br />

sind die nachfolgenden Fälle von Interesse (basierend auf [10, S.37f]):<br />

• Operanden<br />

• Daten: Verfälschte Operanden, die der numerischen Berechnung dienen, werden<br />

das Berechnungsergebnis trüben.<br />

• Adressen: Abweichungen in Speicheradressen sind vergleichbar mit den Auswirkungen<br />

unbedachter Zeigerverwendung im Quellcode: Falsche Daten werden<br />

geladen, Daten werden unbeabsichtigt überschrieben und Operationen auf ungültigen<br />

Speicherbereichen führen zu Programmabstürzen.<br />

• Sprungkonditionen und -ziele: Einem modizierten Operanden, der als Bedingung<br />

für einen Sprung dient, kann das Einschlagen eines anderen Instruktionspfads<br />

folgen. Bei Sprüngen, die einen relativen oder absoluten Zieloperator besitzen,<br />

ist die möglicherweise drastischere Folge, dass die Ausführung in einem<br />

entfernten Abschnitt fortfährt.<br />

• Flags: Flags halten zusätzliche Informationen über den CPU-Zustand oder über<br />

die zuletzt ausgeführte Instruktion. Auch wenn diese, wie auf der x86-Architektur,<br />

nicht explizit les- und schreibbar sind, so ist der Einuss des manipulierten Flags<br />

entscheidend, wenn die nächste, davon abhängige Instruktion dadurch eine andere<br />

Operation ausführt. Ein Beispiel sei auf x86 die Instruktion JE (Jump If<br />

Equal). Eine zuvor erfolgte CMP-Instruktion (für Compare) setzt das Zero-Flag<br />

(ZF). JE interpretiert ein positives ZF als gleichwertige Operanden und wird in<br />

diesem Fall den Sprung ausführen und andernfalls zur nächstfolgenden Instruktion<br />

fortschreiten. Obwohl die Operanden unangetastet blieben, wird bei der<br />

Bit-Umkehr des Flags dennoch ein anderer Sprungeekt einsetzen.<br />

• Register: Sofern das Bitmuster einer Instruktion einen variablen Zugri auf Register<br />

ermöglicht, müssen auch diese als Operanden betrachtet werden. Verursacht<br />

der Zugri primär keine Zugrisverletzung, tritt sekundär einer der ersten<br />

drei erwähnten Fälle ein, da mit Sicherheit ein falscher Operand herangezogen<br />

wurde.<br />

• Befehle: Die Bitmanipulation einer Instruktion auÿerhalb der Operandenbits kann<br />

5

2 Fehlerinjektion<br />

weitreichende Konsequenzen haben. Ein beinahe wünschenswerter Fall ist der Tausch<br />

des Operatoren, wie es durch einen Programmierfehler plausibel wäre: Wird das Bit<br />

der x86-Instruktion JNE 0xF an der Bitposition zum Zählen sei der Operand gestrichen<br />

0 geippt, und geht dieser sinngemäÿ die Instruktion CMP 1, 1 voraus,<br />

so ergibt sich die Instruktion JE 0xF. C-äquivalent stellt dieser Fall ein irrtümliches<br />

if(1!=1) { } statt des korrekten if(1==1) { } dar. Je nach Position des Bit-Flips<br />

kann aber auch die Operation einer ganz anderen Klasse hervortreten. Auf Plattformen<br />

mit variabler Instruktionslänge kann es sogar dazu kommen, dass ein Bit-Flip<br />

eine Instruktion in mehrere kürzere Instruktionen zerfallen lässt oder die Bytes mehrerer<br />

kurzer Instruktionen nun als eine Instruktion gedeutet werden.<br />

2.3 Injektionsebenen<br />

In diesem Abschnitt wird untersucht, ob und wie ein Bit-Flip auf Registerinhalten grundsätzlich<br />

auf verschiedenen Ebenen der Erstellung und Ausführung eines Programms umsetzbar<br />

ist.<br />

2.3.1 Hardware<br />

Die in Abschnitt 2.1 vorgestellten Hardwareansätze lassen zwar eine theoretische Möglichkeit<br />

oen, Einuss auf Registerbits zu nehmen, in der Umsetzung stellen sich jedoch etliche<br />

Hürden in den Weg: Von der zu untersuchenden Hardware ist eine tiefgehende Kenntnis<br />

über den physikalischen Aufbau notwendig. Bei einer Technologieknotengröÿe im zweistelligen<br />

Nanometerbereich ist nicht nur eine ebenso präzise Positionierung der Werkzeuge<br />

nötig, sondern es ist auch sicherzustellen, dass der Wirkungsgrad auf ein einzelne Registerbits<br />

beschränkt werden kann. Für Benutzer ohne die entsprechende Hardware steht dieser<br />

Weg also auÿer Frage.<br />

Ein anderer Ansatz ermöglicht ein eektiveres Vorgehen bei deutlich weniger Aufwand:<br />

JTAG-normiertes On-Chip Debugging (OCD). Verfügt die Hardware über ein JTAG-<br />

Interface, lässt sich durch eine zusätzliche Steuerkomponente, die als JTAG-Controller fungiert,<br />

OCD durchführen. Der Controller setzt auf der Zielhardware einen Unterbrechungspunkt<br />

und kann bei Erreichen desselben eine Sequenz von JTAG-Instruktionen ausführen,<br />

die auch Lese- und Schreibvorgänge auf Benutzerregistern ermöglichen [11, S.103f]. Für<br />

unwillkürliche Bitmanipulationen sind Kenntnisse zum Adressraum und Binärcode des zu<br />

unterbrechenden Programms nötig.<br />

2.3.2 Betriebssystem<br />

Wann immer ein Wechsel vom Benutzermodus in einen ausreichend privilegierten Kernel-<br />

Modus stattndet seien es Systemaufrufe, Unterbrechungsbehandlungen oder ein Kontextwechsel<br />

, verfügt das Betriebssystem über volle Zugrisrechte auf den Prozesszustand<br />

einschlieÿlich der Registerinhalte. An dieser Stelle ist zum Beispiel in Abhängigkeit der<br />

Prozessidentikation und des Instruktionszeigers ein Bit-Flip ausführbar, sei es durch eine<br />

festgeschriebene Betriebssystemroutine oder ein Kernel-Modul.<br />

2.3.3 Virtuelle Maschine<br />

Der Kernvorteil einer Virtuellen Maschine (VM) liegt darin, dem auszuführenden Programm<br />

eine von der Hardware unabhängige Ausführungsmaschine anzubieten. Eine Rea-<br />

6

2.3 Injektionsebenen<br />

lisierung, die etwa die Java Virtual Machine verfolgt, ist die Verwendung von Operandenstacks,<br />

die für die Instruktionen der VM benutzt werden [12, S.17]. Ein anderer Ansatz ist<br />

die Benutzung von virtuellen Registern, sodass dem Programm eine beliebige Anzahl von<br />

Speicherstellen zur Verfügung steht und jede VM-Instruktion für die Operanden entsprechende<br />

Registerbezeichnungen verlangt.<br />

Aus diesem Grund ist es nicht möglich, innerhalb einer VM die Abbildung eines Programms<br />

auf Register der ausführenden CPU zu betrachten. Viel mehr ist es der virtuellen<br />

Maschine selbst überlassen, an welcher Stelle und unter welchen Bedingungen diese Bitmanipulationen<br />

vornehmen mag. Verfügt die VM über einen Just-In-Time (JIT)-Compiler,<br />

anstatt Bytecode bloÿ zu interpretieren, sollte es dieser jedoch ein Leichtes sein, Bitmanipulationen<br />

auf Registern in entsprechende Plattforminstruktionen zu übersetzen.<br />

2.3.4 Kompilierungszeit<br />

Zum Zeitpunkt des Schreibens des Programmquellcodes weiÿ der Entwickler nicht mit<br />

etwas Erfahrung wird sein Bauchgefühl ihm jedoch eine Vorstellung ermöglichen , zu<br />

welchem Zeitpunkt welche Variable in welches Register geladen und anschlieÿend gehalten<br />

wird. Diese Entscheidungen trit der Compiler in Abhängigkeit von Datentypen, dem<br />

Ergebnis der Registerallokationsoptimierung und anderen Optimierungsstufen. Aggressive<br />

Optimierungsstufen wie etwa -O3 des GNU C Compiler (GCC) können sogar dazu führen,<br />

dass aufgrund von statischer Zwischencodeanalyse ganze Codepassagen zur Kompilierungszeit<br />

auf einen Ausdruck reduziert werden und dadurch nicht die erwartete Übersetzung<br />

erfahren.<br />

Ein erster Ansatz ist der Blick in den vom Compiler erzeugten Assemblercode, wie er<br />

beim GCC mit dem Flag -S ausgegeben werden kann. Ausgestattet mit neuen Erkenntnissen<br />

lieÿe sich der Quellcode mit plattformspezischen asm-Direktiven ausstatten, um<br />

dadurch Bedingungen für die Manipulation von Registerbelegungen im Bereich von Interesse<br />

aufzusetzen. Diese Lösung ist aufgrund der Abhängigkeit von verschiedenen Compilern,<br />

Compiler-Versionen, Kongurationsparametern und Codeanpassungen jedoch zu<br />

fragil. Auÿerdem nimmt sie zusätzlich die Plattformunabhängigkeit, wenn diese ohne asm-<br />

Anweisungen gegeben ist.<br />

Eine denkbare Alternative lieÿe sich mittels eines Compilers umsetzen, der seitens<br />

des Quellcodes mit Makros dazu aufgefordert wird, Registermanipulationen vorzunehmen.<br />

Auf diese Weise lassen sich verschiedene Operationen einstreuen, beispielsweise Bit-Flip im<br />

Register X und Position i oder Bit-Flip beim nächsten Laden der Variable v in ein Register.<br />

Eine Verfeinerungen des Verfahrens erlaubt, dass zusätzlich auf die Rekursionstiefe oder<br />

einen Aufrufzähler Rücksicht genommen wird. Im Umkehrschluss bedeutet das, dass ein<br />

Compiler entweder auf die Optimierung bestimmter Bereiche verzichten muss, oder dass<br />

eine solche Code-Annotation nur bis zu einer gewissen Optimierungsstufe funktionieren<br />

wird.<br />

2.3.5 Programm<br />

Ist ein Programm kompiliert und zusammengelinkt, verbleibt vor der Ausführung die Möglichkeit<br />

zur statischen Binärinstrumentierung. Mit der Hilfe von Werkzeugen für Reverse<br />

Engineering, etwa einem Disassembler und Assembler, kann der Assemblercode manuell<br />

mit zusätzlichen Instruktionen ausgestattet werden. Per Hand ist das Vorgehen jedoch<br />

mühselig, da die Ausgabe hochgradig von der Compiler-Konguration und dem Quellcode<br />

abhängt. Erschwerend kommt hinzu, dass die hinzuzufügenden Instruktionen die bestehende<br />

Funktionalität, insbesondere relative Sprünge und CPU-Flags, berücksichtigen müssen.<br />

7

2 Fehlerinjektion<br />

Mit einem Framework zur Disassemblierung und statischen Binärinstrumentierung, wie in<br />

[13] und [14] vorgestellt, ist jedoch auch ein automatisiertes Vorgehen zu diesem Zweck<br />

denkbar: Bei einem registerorienterten Bit-Flip kann die Codeinjektion auf einfache Weise<br />

durch Zählung oder Zufall vorgenommen werden, wann immer dieses Register als Operand<br />

implizit oder explizit von einer Instruktion benutzt wird. Bei einem belegungsorientierten<br />

Bit-Flip ist zusätzlicher Aufwand nötig: Durch das Suchen von Ladeoperationen, die<br />

Daten von einer gewählten Speicheradresse in ein Register kopieren, und das Finden von<br />

nachfolgenden Instruktionen, die mit dieser Belegung operieren, lassen sich verschiedene<br />

Injektionsbedingungen aufstellen. Sind Daten erst zur Laufzeit auösbar, etwa Adressen<br />

mit einem registerbasierten Versatz, muss die Instrumentierung Code injizieren, der die<br />

Erkennung von Ladequellen und Bitmanipulationen zur Ausführungszeit vornimmt.<br />

Im Gegensatz zur Statischen Binäranalyse (SBA) wird bei der Dynamischen Binäranalyse<br />

(DBA) der Binärcode zur Programmlaufzeit und auch erst kurz vor der Ausführung<br />

durch die CPU analysiert und instrumentiert. Die Voraussetzungen dazu sowie die damit<br />

einhergehenden Vor- und Nachteile werden ausführlicher in Abschnitt 3.1 behandelt.<br />

Das im folgenden Kapitel vorgestellte Programm FITIn macht sich verschiedene Ansätze<br />

zu Nutze, die in diesem Abschnitt vorgestellt wurden: die Kompilierungszeit und<br />

die Anwendung eines DBI-Frameworks, das FITIn Instruktionen einer virtuellen Maschine<br />

bereitstellt.<br />

8

3 Erweiterung von FITIn<br />

Dieses Kapitel stellt die Ausführungsumgebung von FITIn, seine ursprüngliche Fassung,<br />

Erweiterungsansätze sowie die realisierte Implementierung vor.<br />

3.1 Dynamische Binärinstrumentierung<br />

Die dynamische Binäranalyse stellt einzig die Anforderung an das zu untersuchende Programm,<br />

dass dieses in einem unterstützen Binärformat vorliegt. Der wesentliche Unterschied<br />

zur SBA besteht darin, dass ein Programm erst als Prozess initialisiert wird, bevor<br />

die erste Binäranalyse vorgenommen wird, und nicht als Datei auf dem Sekundärspeicher<br />

untersucht und behandelt wird. Die SBA ist nur begrenzt in der Lage, Instruktionen zu<br />

erkennen, die dem Ergebnis von Selbstextraktion, Selbstmodikation oder dynamischem<br />

Erzeugen und Nachladen von Code entspringen, insbesondere dann nicht, wenn die genannten<br />

Vorgänge von externen Eingaben abhängen [7, S.3f].<br />

Gängige Anwendungsfälle sind Programme, die aus Gründen des Platzes oder der Ladeperformance<br />

zum Beispiel UPX-komprimiert ausgeliefert werden, Programme, die Schutzmechanismen<br />

zur Durchsetzung von digitalem Rechtemanagement besitzen, Plug-In-fähige<br />

Programme und Programme, die einen prozessinternen JIT-Compiler benutzen.<br />

Ein DBI-Framework initialisiert das zu untersuchende Programm analog zu einem Betriebssystem<br />

und beginnt mit der DBA an der ersten Instruktion des Programms. Abhängig<br />

vom Framework wird jede nachfolgende Instruktion oder auch ganze Blöcke von Instruktionen<br />

an die DBI-Komponente übergeben und anschlieÿend ausgeführt. Auf diese Weise<br />

wird im Unterschied zur SBA einzig tatsächlich auszuführender Code betrachtet, da sich die<br />

DBA ausschlieÿlich an erreichten Sprüngen und Abzweigungen des Codes entlangbewegt.<br />

Die Konsequenz ist, dass der Sprung in dynamisch erzeugten Binärcode für das DBI-<br />

Framework transparent bleibt. Die Kehrseite des Verfahrens ist verständlicherweise ein<br />

Einbruch in der Ausführungsgeschwindigkeit des Zielprogramms.<br />

Eine weitere Herausforderung, die ein DBI-Framework meistern muss, besteht darin,<br />

mit dem ausgeführten Programm nicht in Konikt zu treten oder solche Fälle angemessen<br />

zu behandeln, seien es Adressräume im virtuellen Speicher, die zwischen Framework und<br />

Prozess kollidieren könnten oder Ressourcen, auf die nur einer von beiden zur Zeit zugreifen<br />

kann. Das DBI-Framework darf weiterhin nicht die Ausführungsgewalt verlieren, wenn<br />

zum Beispiel durch einen Systemaufruf aus dem Kernel-Modus zurück in das Programm<br />

gesprungen wird. In den Kernel-Modus kann das DBI-Framework nicht eingreifen. Legt<br />

das Programm zusätzliche Threads an, sollte das DBI-Framework diese ebenbürtig zum<br />

Hauptthread behandeln können.<br />

Die Verwendung von DBI erfolgt allerdings nicht einzig aus der Motivation, Hindernisse<br />

in der Analyse zu überwinden. Viel mehr erlaubt DBI eine weitere Analyseklasse:<br />

Speicherbeschattung. Speicherbeschattung ist die Fähigkeit, jedes vom untersuchten Programm<br />

verwendete Byte durch zusätzlichen Speicher zu beschatten [15, S.89]. Die Schattenwerte<br />

genannten Daten werden dazu verwendet, Aussagen über das beschattete Byte<br />

zur Laufzeit zu treen. Beispielsweise lassen sich so Daten darüber erheben, wie oft ein<br />

Byte gelesen oder ob und wann es allokiert wurde. Diese Fähigkeit ermöglicht mächtige<br />

9

3 Erweiterung von FITIn<br />

Softwarewerkzeuge zur Laufzeitanalyse von Programmen.<br />

Ein DBI-Framework mit lückenloser Unterstützung zur Speicherbeschattung muss nach<br />

[15, S.90f] folgende Fähigkeiten bieten:<br />

1. Die Beschattung aller Register.<br />

2. Die Beschattung des gesamten Prozessspeichers.<br />

3. Die Instrumentierung von Lese- und Schreiboperationen auf den Prozessspeicher.<br />

4. Die Instrumentierung von Systemaufrufen, die auf den Prozessspeicher lesend oder<br />

schreibend zugreifen.<br />

5. Die Beschattung der initialen Speicherbelegung.<br />

6. Die Instrumentierung von speicherallokierenden und -freigebenden Systemaufrufen.<br />

7. Die Instrumentierung von Veränderungen am Stack-Zeiger.<br />

8. Die Instrumentierung von (De-)Allokationen auf dem Heap-Speicher.<br />

9. Ausgabemechanismen.<br />

Das DBI-Framework Valgrind erfüllt alle der genannten Punkte [15, S.96f].<br />

3.2 Valgrind<br />

3.2.1 Allgemeines<br />

Valgrind wurde im Jahr 2002 in seiner ersten oziellen Version veröentlicht, es steht<br />

unter der GNU Public License (GPL). Bekannt ist dieses DBI-Framework insbesondere<br />

durch das enthaltene Werkzeug Memcheck, das dazu benutzt wird, um Speicherzugrisfehler<br />

und Speicherlecks in einem Programm zu ermitteln. Zur Standarddistribution von<br />

Valgrind [16] gehören jedoch noch weitere DBA-Werkzeuge, zum Beispiel Cachegrind, das<br />

die Cachefreundlichkeit des Programms analysiert, oder Helgrind, das Race Conditions<br />

bei Multithreading erkennt. Zu den unterstützten Umgebungen gehören unterschiedliche<br />

Kombinationen aus den Architekturen x86, AMD64, PowerPC, ARM, S390 und MIPS und<br />

den Betriebssystemen Linux, Darwin und Android.<br />

Die Infrastruktur von Valgrind ist so aufgebaut, dass jedes der genannten Werkzeuge<br />

ein Plug-In darstellt, welches mit dem Parameter -tool= gestartet wird. Jedes Plug-In<br />

fügt sich in den Kompilierungsvorgang der Valgrind-Distribution ein, der Quellcode dabei<br />

ist wie auch für Valgrind in C zu schreiben.<br />

3.2.2 Instrumentierung<br />

Wichtig zu beleuchten, ist das interne Vorgehen von Valgrind, das Verhältnis des Framework-<br />

Kerns zum geladenen Plug-In und auch die Art und Weise, wie Valgrind nicht-triviale<br />

Probleme in Bezug auf die Ausführung und Speicherbeschattung behandelt.<br />

Mit dem Spezizieren des zu untersuchenden Programms als Kommandozeilenargument<br />

initialisiert Valgrind das Programm selbstständig, sodass aus der Sicht des Betriebssystems<br />

nur Valgrind als Prozess erkennbar ist. Beginnend am Einstiegspunkt des Programms<br />

stellt Valgrind sogenannte Superblocks (SB) zusammen, die für das weitere Vorgehen<br />

als isolierte Codeabschnitte behandelt werden. Ein SB ist zusammengestellt, sobald<br />

eine der folgenden Bedingungen erfüllt ist [15, S.93]:<br />

• Eine plattformspezische Anzahl von Instruktionen wurde erreicht.<br />

• Eine Instruktion für eine bedingte Codeabzweigung wurde erreicht.<br />

• Ein Sprung zu einem Bereich, für den noch kein SB existiert, wurde gefunden.<br />

10

3.2 Valgrind<br />

• Es wurden drei Sprünge zu Adressen gezählt, für die bereits SBs angelegt worden<br />

sind.<br />

Ist der aktuell gewählte Block noch nicht dem Plug-In übergeben worden, übersetzt<br />

Valgrind die nativen Instruktionen in eine eigene Repräsentation, die VEX Intermediate<br />

Representation (VEX IR). Im Plug-In wird ein Callback aufgerufen, dem die VEX IR<br />

übergeben wird. Es ist nun die Aufgabe des Plug-Ins, die VEX IR entsprechend seiner<br />

Aufgabe zu analysieren und zu instrumentieren und die instrumentierte VEX IR an Valgrind<br />

zurückzugeben, das die modizierte Fassung in native Instruktionen übersetzen wird.<br />

Der Vorgang, den Binärcode vollständig in eine Zwischenrepräsentation zu übersetzen und<br />

anschlieÿend in nativen Code zurückzuführen, wird Disassemble-and-Resynthesize (D&R)<br />

genannt.<br />

Dieser Vorgang wird je SB nur einmal ausgeführt. Ein Ausnahmefall ist selbstmodi-<br />

zierender Code: Valgrind erkennt Veränderungen am Code und setzt die SBs dafür neu<br />

zusammen.<br />

Beginn<br />

Wähle SB<br />

Weiterer<br />

SB?<br />

ja<br />

SB behandelt,<br />

aktuell?<br />

nein<br />

nein<br />

Disassemblierung<br />

Instrumentierung<br />

ja<br />

Kompilierung<br />

SB Ausführung<br />

Ende<br />

Abbildung 3.1: Programmausführung in Valgrind<br />

Mit der letzten Instruktion eines SB kehrt der Prozess zurück in einen Codebereich<br />

von Valgrind, in welchem der Code für den nächsten auszuführenden Block nachgeschlagen,<br />

zuvor gegebenenfalls instrumentiert, und dann ausgeführt wird. In Abbildung 3.1<br />

11

3 Erweiterung von FITIn<br />

ist die Ausführungsbehandlung von Valgrind zusammengefasst und als Kontrollussgraph<br />

dargestellt, einzig der Vorgang Instrumentierung involviert hier das Plug-In.<br />

In Valgrind wird die Ausführung verschiedener Threads serialisiert. Ein Blockierungsmechanismus<br />

stellt sicher, dass nur ein Thread zur Zeit SBs ausführen kann. So bendet<br />

sich zusätzlich zur Prozesszeiteinteilung des Betriebssystems innerhalb von Valgrind ein<br />

Zeitverwalter, der vorgibt, zu welchem Zeitpunkt ein Thread die Blockierung zugunsten<br />

eines anderen aufgeben muss. Die Entscheidung wird jeweils nach der Ausführung eines<br />

SB getroen [15, S.95f].<br />

Eine weitere erwähnenswerte Eigenschaft von Valgrind ist die Behandlung von Systemaufrufen.<br />

Ein Systemaufruf wird stets als eigenständiger SB behandelt, sodass der Valgrind<br />

den Benutzercode in einen SB davor und in einen danach zerteilt. Zur Instrumentierungszeit<br />

wird der Systemaufruf von Valgrind durch einen Sprung zu einem eigenen, spezischen<br />

Wrapper ersetzt. Für jede unterstützte Architektur und für jedes unterstütze Betriebssystem<br />

verfügt Valgrind Wissen über jeden einzelnen Systemaufruf, einschlieÿlich der Seiteneekte<br />

auf den Prozessspeicher und auf die Benutzerregister. Der spezische Wrapper ruft<br />

nun entsprechende Callbacks vor und nach der tatsächlichen Ausführung auf. Ein Plug-In<br />

kann für die Ereignisse, von denen es abhängt, Callbacks registrieren, beispielsweise auf<br />

die Ereignisse Ein lesender Registerzugri wird stattnden oder Ein Schreibvorgang auf<br />

den Prozessspeicher hat stattgefunden. Geeignete Übergabeparameter im Callback erlauben<br />

dem Plug-In eine lückenlose Verfolgung von Vorgängen, die im Zusammenhang mit<br />

Systemaufrufen stehen.<br />

Weitere Callbacks können bei Valgrind angemeldet werden, um dem Plug-In zum Beispiel<br />

die Veränderung des Stack-Zeigers oder das Verlassen des Benutzercodes zu signalisieren.<br />

3.2.3 VEX IR<br />

Die von Valgrind genutzte Zwischendarstellung ist unabhängig von der Architektur, auf<br />

welcher Valgrind benutzt wird. VEX IR liegt in Static Single Assignment-Form vor, sodass<br />

jede Codevariable nur ein einziges Mal eine Zuweisung erfahren kann.<br />

Das Plug-In erhält mit dem Instrumentierungs-Callback einen Zeiger auf eine IRSB-<br />

Struktur, die die VEX IR eines SB in Form einer Liste enthält. Die für die Beschreibung<br />

der Implementierung von FITIn essentiellen Datentypen der VEX IR sind:<br />

• IRTemp: Eine VEX IR-Variable. Angaben zu dieser bezüglich des Datentyps in Form<br />

von IRType benden sich in der IRSB-Kontextstruktur IRTypeEnv.<br />

• IRExpr: Ein VEX IR-Wrapper für alle Daten, die einen Ausdruck darstellen. Dazu<br />

gehören als Unterstrukturen innerhalb eines union:<br />

• Const: Ein konstanter, numerischer Wert.<br />

• Get: Der Registerinhalt an der angegebenen Position der Registerschattentabelle.<br />

Diese Tabelle dient dazu, dass Valgrind zur Ausführungszeit Speicherbereiche<br />

bereitstellen kann, die ersatzweise dem Datenaustausch über Register dienen.<br />

• Load: Der Inhalt an einer Speicheradresse.<br />

• RdTmp: Der Wert eines IRTemp.<br />

• {Un,Bin,Tri,Q}op: Ausdrücke, die bis zu vier Argumente erwarten, etwa logische<br />

oder mathematische Operatoren.<br />

• IRStmt: Der Typ einer VEX IR-Instruktion und Datentyp der Instruktionsliste von<br />

IRSB. Wichtige Instruktionen sind:<br />

• Dirty: Der Aufruf einer unreinen Hilfsmethode eine Methode, deren Operation<br />

12

3.2 Valgrind<br />

1 MOV EAX , [ EAX -8]<br />

2 ADD EAX , 1<br />

3 IMUL EAX , [ EAX -8]<br />

1 ------ IMark (0 x8048400 , 3, 0) ----<br />

2 t30 = Add32 (t23 ,0 xFFFFFFF8 : I32 )<br />

3 t32 = LDle : I32 ( t30 )<br />

4 ------ IMark (0 x8048403 , 3, 0) ----<br />

5 t8 = Add32 (t32 ,0 x1 : I32 )<br />

6 PUT (68) = 0 x8048406 : I32<br />

7 ------ IMark (0 x8048406 , 4, 0) ----<br />

8 t33 = Add32 (t23 ,0 xFFFFFFF8 : I32 )<br />

9 t11 = LDle : I32 ( t33 )<br />

10 t13 = Mul32 (t11 , t8 )<br />

Abbildung 3.2: Disassemblierung in Valgrind: x86-Programm (li.), VEX IR (re.)<br />

nicht einzig von den Parametern abhängt , der in einem IRDirty konguriert<br />

wurde.<br />

• Mark: Das Vorkommen eines solchen Markers trennt die Übersetzung zweier<br />

nativer Instruktionen voneinander.<br />

• Put: Das Schreiben eines IRExpr an eine angegebene Position in der Registerschattentabelle.<br />

• Store: Das Schreiben eines IRExpr an eine Speicheradresse.<br />

• WrTmp: Die Zuweisung eines IRExpr zu einem IRTemp.<br />

Eine vollständige Spezikation der Sprache bendet sich im Anhang A.1. Nachdem etwa<br />

das Plug-In die VEX IR eines SB instrumentiert hat, führt Valgrind die instrumentierte<br />

VEX IR auf einer virtuellen CPU aus, die Instrumentierungsfehler der VEX IR ermittelt.<br />

Im Fall eines Fehlers wird die Ausführung abgebrochen.<br />

Ein Beispiel für die textuelle Darstellung der VEX IR und für die Übersetzung von<br />

x86-Instruktionen nach VEX IR ist in Abbildung 3.2 gegeben. Die ersten beiden Parameter<br />

eines jeden IMark geben Auskunft über die ursprüngliche Adresse der Instruktion<br />

und über die Originalgröÿe in Bytes. Im Beispiel der VEX IR in Zeile 6 wird die Adresse<br />

der nachfolgenden Instruktion in die Registerschattentabelle an den Index 68 geschrieben:<br />

Auf der x86-Architektur bendet sich für Valgrind an dieser Stelle der Instruktionszeiger<br />

EIP. Die Instruktion der Zeile 6 ist überüssig, jedoch kennt der Optimierungsalgorithmus<br />

von Valgrind diesen Index nicht als Instruktionszeiger. Nicht einmal die Ursprungsplattform<br />

ist ihm bekannt. In der nicht-optimierten Fassung existiert für jede Instruktion eine<br />

vollständige Beschreibung aller für die VEX IR relevanten Prozessoreekte einschlieÿlich<br />

der Adresse der nächstfolgenden Instruktion, auf x86-Computern gesehen als Zuweisung<br />

der Adresse an EIP. Aus diesem Grund können Redundanzen in der VEX IR auftreten,<br />

für deren Beibehaltung aus der Sicht des Optimierers jedoch im Kontext des nicht vollständig<br />

aufgeführten IRSB eine Notwendigkeit besteht. Im Gegensatz dazu werden in<br />

diesem Beispiel die Flag-Eekte komplett eliminiert, etwa das Aktualisieren des ZF nach<br />

der Addition, da keine nachfolgende VEX IR-Operation auf diesen Flag-Zustand zugreift.<br />

Die Abbildung 3.3 erlaubt einen detaillierten Blick auf die D&R-Technik von Valgrind.<br />

Zu den VEX IR-Ausdrücken IRExpr sei angemerkt, dass einige Typen grundsätzlich eine<br />

beliebige Schachtelungstiefe ermöglichen. Aus Gründen der besseren Optimierbarkeit und<br />

einer einfachen Instrumentierung durch das Plug-In linearisiert Valgrind die VEX IR jedoch<br />

so, dass die Ausdruckstiefe nicht gröÿer als 1 ist. Für tiefer gelegene Ausdrücke wird<br />

für den Elternausdruck E i ein eigenes IRTemp t |env|+1 mittels einer WrTmp-Instruktion geschaen<br />

und E i im Ursprungsknoten durch ein RdTmp auf t |env|+1 ersetzt, solange bis die<br />

Ausdruckstiefe normalisiert ist. env sei dabei die Menge von bereits vergebenen IRTemp-<br />

13

3 Erweiterung von FITIn<br />

Indizes innerhalb des aktuellen IRSB.<br />

Die nach der Instrumentierung stattndenden Schritte entsprechen dabei dem klassischen<br />

Compiler-Konzept ab dem Punkt, ab dem der Code in einer Zwischenrepräsentation<br />

vorliegt: Optimierung der Repräsentation, die Wahl der Instruktionen, die Registerallokation<br />

und die Übersetzung in den letztendlichen Binärcode.<br />

Beginn<br />

Disassemblierung<br />

Linearisierung,<br />

Optimierung<br />

Instrumentierung<br />

Optimierung<br />

Baumbildung<br />

Instruktionswahl<br />

Registerwahl Binärcode Ende<br />

Abbildung 3.3: Disassemble-and-Resynthesize in Valgrind<br />

Abschlieÿend zu diesem Unterpunkt seien die wesentlichen Vorteile, die Valgrind aus<br />

der Sicht eines Plug-In-Entwicklers bietet, aufgeführt:<br />

• Abstraktion der Architektur: Der Entwickler steht nicht unter dem Druck, jede einzelne<br />

CPU-Instruktion detailliert kennen zu müssen, um überhaupt eine einzige Plattform<br />

vollständig unterstützen zu können. Diese Arbeit wird komplett von Valgrind<br />

übernommen und ermöglicht die Plattformunabhängigkeit des Plug-Ins.<br />

• Abstraktion des Betriebssystems: Analog muss dem Entwickler nicht jeder einzelne<br />

Systemaufruf aller unterstützten Betriebssysteme vollständig geläug sein. In Valgrind<br />

wird dieses Problem elegant gelöst, da ausschlieÿlich das Framework dieses<br />

Wissen besitzen muss, sodass der Entwickler sich einzig um bestimmte Ereignisklassen<br />

zu kümmern hat.<br />

• Serialisierung der Parallelität: Es ist nicht erforderlich, als Entwickler etwas über<br />

das Multithreading-Verhalten des Programms zu kennen. Ebenso kann sich der Entwickler<br />

der Tatsache sicher sein, dass zu jedem Zeitpunkt stets nur ein SB ausgeführt<br />

wird und Unterbrechungen eektiv nur zum Zeitpunkt von SB-Übergängen stattnden.<br />

Die Rechnung dafür hat der Anwender in der Form zu bezahlen, dass Valgrind<br />

die Interaktivität des Programms einschränkt und Performancegewinne, die durch<br />

echte Parallelausführung bedingt sind, einstreicht.<br />

Umgekehrt betrachtet, zwingt der erstgenannte Punkt den Entwickler dazu, den Benutzercode<br />

nicht weiter als die übergebene VEX IR betrachten zu dürfen. Die Prämisse,<br />

mit der Hilfe von Valgrind ein plattformspezisches oder -optimiertes Werkzeug entwickeln<br />

zu können, muss grundsätzlich verworfen werden. Dadurch ist ein Plug-In für Valgrind vergleichbar<br />

mit einer Instrumentierungskomponente in einer virtuellen Maschine.<br />

Weiterhin darf man nicht die Behauptung aufstellen, dass ein Plug-In von Valgrind<br />

an sich ein reines DBI-Werkzeug sei: Schlieÿlich wird die von Valgrind übergebene Zwischenrepräsentation<br />

lediglich einmal zu einem transparenten Zeitpunkt vor der erstmaligen<br />

Ausführung instrumentiert, und sie zwingt dadurch den Entwickler dazu, streng zwischen<br />

dem Zeitpunkt der Instrumentierung und dem Zeitpunkt der Ausführung zu unterscheiden.<br />

14

3.3 FITIn<br />

3.3 FITIn<br />

FITIn ist ein von Clemens Terasa entwickeltes Plug-In für Valgrind, das dem Zweck dient,<br />

einen Bit-Flip im Prozessspeicherraum zur Ausführungszeit des Programms vorzunehmen.<br />

Die Motivation hinter diesem Programm ist die Evaluierung von SIHFT-Maÿnahmen [17,<br />

S.21]. In diesem Abschnitt wird beschrieben, wie die ursprüngliche Fassung funktioniert.<br />

An erster Stelle steht die Notwendigkeit, dass dem Benutzer der Programmquellcode,<br />

geschrieben in C oder C++, vorliegt. Eine von FITIn erstellte C-Header-Datei<br />

fitin.h, welche sich im Verzeichnis include der Valgrind-Distribution bendet, muss<br />

mittels #include-Makro eingebunden werden. Dadurch stehen dem Entwickler die zur<br />

Instrumentierung benötigten Makros zur Verfügung: FITIN_MONITOR_VARIABLE(var) und<br />

FITIN_MONITOR_MEMORY(mem, size). Diese Makros stellen sogenannte Valgrind Client Requests<br />

dar: Der Compiler erweitert den Stack um einen Identiziererwert und fünf weitere<br />

Werte in Plattformadressbreite, die Ganzzahlen oder Adressen sein dürfen. Valgrind ist in<br />

der Lage, den Identizierer dem Plug-In zuzuordnen und übergibt diesem mittels Callback<br />

die bis zu fünf Argumente. Im Falle von FITIn werden zwei Argumente verwendet: Startadresse<br />

und Gröÿe des Bereichs, nach dem das Plug-In Ausschau halten soll. Intern wird<br />

jede Beobachtungsauorderung als Monitorable-Struktur in eine Liste aller zu beobachtenden<br />

Bereiche abgelegt.<br />

Im nächsten Schritt muss der Compiler eine Debug-Version des Programms erzeugen,<br />

da eventuell Variablen beobachtet werden, die nicht unmittelbar im Stack-Speicher von<br />

main verwendet oder referenziert werden. Selbst bei einem kleinen Programm durchläuft<br />

Valgrind eine drei- bis vierstellige Anzahl von SBs. Aus Gründen der Performance und der<br />

letztendlichen Benutzungsabsicht ist es nicht erforderlich, SBs, die nicht zum Benutzercode<br />

gehören, etwa die der C-Standardbibliothek, zu analysieren. Um dieses Vorgehen zu<br />

erlauben, muss es Valgrind jedoch möglich sein, die Prozedurzugehörigkeit des aktuellen<br />

SB ermitteln zu können. In einer Debug-Version sind Informationen wie der aktuelle Prozedurname<br />

in das Programm eingebettet. Der Benutzer ist in diesem Fall dazu aufgefordert,<br />

bei Prozeduren, die nicht main sind, mit dem Kommandozeilenargument --fnname= die zu<br />

analysierende Prozedur zu bestimmen oder durch --include= Valgrind mitzuteilen, welche<br />

SBs in Angabe des Quellcodeverzeichnisses zum Benutzercode gehören.<br />

Mit der Auorderung, dass Valgrind das Plug-In FITIn laden soll, kann das Programm<br />

im Sinne von FITIn benutzt werden. Zusätzlich sind die Kommandozeilenargumente<br />

--mod-bit= und --mod-load-time= anzugeben. --mod-load-time=n weist FITIn<br />

an, vor dem n-ten Lesezugri auf den Speicher des zutreenden Monitorable am Bit m aus<br />

--mod-bit=m einen Bit-Flip durchzuführen. Zutreend bezeichnet dabei das Monitorable,<br />

das im Rahmen des für alle Monitorable geltenden Zählers getroen wurde. Mit dem Argument<br />

--inst-limit= kann die Anzahl der insgesamt ausgeführten Instruktionen durch das<br />

Programm ohne die der Instrumentierung, der Ausführungshilfsmethoden von FITIn und<br />

des Valgrind-Kerns begrenzt werden, etwa um nach einem Bit-Flip eine Endlosschleife<br />

zu verhindern.<br />

Möchte der Benutzer lediglich einen Eindruck vom Lesezugrisverhalten des Programms<br />

auf Variablen inner- und auÿerhalb eines Monitorable erlangen, kann er einen<br />

Golden Run-Durchlauf ausführen (Kommandozeilenargument --golden-run=yes), der keinen<br />

Bit-Flip vornehmen wird.<br />

Der Instrumentierungsprozess lässt sich wie folgt beschreiben: Vor jedem IMark fügt<br />

FITIn einen IRDirty-Aufruf namens incrInst ein, dessen Aufgabe es ist, die Anzahl<br />

der originalen Instruktionen zu zählen und bei gesetztem Limit und der Überschreitung<br />

dessen die Ausführung abzubrechen. Stöÿt FITIn in einem relevanten SB auf eine Load-<br />

15

3 Erweiterung von FITIn<br />

1 MOV EBX , [ EBP -8]<br />

2 MOV EAX , EBX<br />

3 ADD EAX , 1<br />

4 IMUL EAX , EBX<br />

1 ------ IMark (0 x8048400 , 3, 0) ----<br />

2 t26 = Add32 (t19 ,0 xFFFFFFF8 : I32 )<br />

3 t28 = LDle : I32 ( t26 )<br />

4 PUT (20) = t28<br />

5 ------ IMark (0 x8048403 , 2, 0) ----<br />

6 ------ IMark (0 x8048405 , 3, 0) ----<br />

7 t8 = Add32 (t28 ,0 x1 : I32 )<br />

8 ------ IMark (0 x8048408 , 3, 0) ----<br />

9 PUT (40) = 0 x27 : I32<br />

10 PUT (44) = t28<br />

11 PUT (48) = t8<br />

12 PUT (52) = 0 x0 : I32<br />

13 t13 = Mul32 (t28 , t8 )<br />

14 PUT (68) = 0 x804840B : I32<br />

Abbildung 3.4: Registerübersetzung in Valgrid: x86-Programm (li.), VEX IR (re.)<br />

Instruktion, fügt es einen weiteren Aufruf vor diesem ein: preLoadHelper. Dieser Methode<br />

wird zur Laufzeit die Ladeadresse der nachfolgenden Instruktion übergeben: Sie iteriert<br />

über alle aktiven Monitorable und prüft dabei, ob die gespeicherten Angabe zur Startadresse<br />

der der Ladeinstruktion entspricht. In diesem Fall wird der globale Zugriszähler<br />

um 1 erhöht. Erreicht der Zähler den Wert von --mod-load-time=, führt die Methode auch<br />

den Bit-Flip auf der Speicheradresse aus.<br />

In jedem Programmdurchlauf kann maximal ein einzelner Bit-Flip vorgenommen werden.<br />

3.4 Registerbehandlung in Valgrind<br />

In Abschnitt 3.2.3 wurde bereits ein Einblick in das Übersetzungsverfahren von Instruktionen<br />

in Valgrind gegeben. In Hinblick auf die Erweiterung von FITIn, Bit-Flips auch auf<br />

Registern vornehmen zu können, muss die VEX IR jedoch noch etwas weiter betrachtet<br />

werden.<br />

Im Beispiel 3.4 nden die x86-Operationen nach dem Laden eines Werts vom Stack vollständig<br />

auf den Registern EAX und EBX statt. Die gezeigten IMark-Abschnitte entsprechen<br />

den Ursprungsinstruktionen, wie es sich durch den Vergleich verschiedener D&R-Schritte<br />

von Valgrind ermitteln lässt (Benutzung des Parameters --trace-flags= auf den entsprechenden<br />

SBs). Dieses Beispiel wird im Folgenden genauer erläutert:<br />

• IMark(0x8048400): Die EBP-versetzte (t19) Ladeadresse wird von t26 referenziert,<br />

der Ladewert anschlieÿend nach t28 geladen und an den Index 20 der Registerschattentabelle<br />

geschrieben, welcher korrekt das Register EBX bezeichnet.<br />

• IMark(0x8048403): Dieser Befehl wurde komplett eliminiert, es ist also nicht erkennbar,<br />

dass ein Register in ein anderes kopiert wurde (EBX nach EAX).<br />

• IMark(0x8048405): Die Addition des in t28 referenzierten Wertes um 1 ndet statt,<br />

jedoch wird das Ergebnis t8 nicht zum Aktualisieren eines Registers benutzt.<br />

• IMark(0x8048408): t28 wird mit t8 multipliziert. Es ndet jedoch erneut keine Registeraktualisierung<br />

(durch t13) statt. Die Indizes 40, 44, 48 und 52 werden mit<br />

Werten belegt, die Valgrind zur Behandlung der Flag-Eekte benutzt.<br />

Anhand des Beispiels 3.4 wird deutlich, dass eine ursprungsgetreue Abbildung der<br />

Registerbenutzung nicht gegeben ist. Es ist also nicht möglich, etwa vor Beginn oder am<br />

Ende eines IMark Instruktionen einzufügen, die, in Erwartung eines konsistenten Zustands<br />

16

3.5 Evaluierung von Ansätzen<br />

1 MOV EBX , [ EAX -8]<br />

2 MOV [ EBP +0 x14 ], EBX<br />

3 LEA ECX , [ EBX +0 x1 ]<br />

4 MOV [ EBP +0 x28 ], 0 x27<br />

5 MOV [ EBP +0 x2C ], EBX<br />

6 MOV [ EBP +0 x30 ], ECX<br />

7 MOV [ EBP +0 x34 ], 0 x0<br />

8 MOV [ EBP +0 x44 ], 0 x804840B<br />

9 MUL EBX , ECX<br />

Abbildung 3.5: Ergebnis der x86-Codesynthese<br />

der Registerschattentabelle, einen Bit-Flip auf dem entsprechenden Eintrag vornehmen<br />

können. Die Abbildung 3.5 verdeutlicht weiterhin, wie sehr die operationelle Semantik des<br />

Ursprungscodes in Abbildung 3.4 verändert wird.<br />

Der Optimierer von Valgrind ermittelt beim Disassemble-Vorgang nicht nur, welche<br />

Operationen im aktuellen IRSB eliminiert werden können, sondern es werden darüber hinaus<br />

alle Paare von PUT-GET-Instruktionen auf demselben Oset entfernt, wenn die Belegung<br />

über den IRSB hinaus nicht relevant ist.<br />

Weitere Konsequenzen auf die operationelle Semantik, die durch den Compiler von<br />

Valgrind bedingt sind:<br />

• Valgrind nimmt anhand des Datenussgraphen eine eigenständige Registerallokation<br />

vor.<br />

• Nicht alle CPU-Instruktionen werden für die Kompilierung unterstützt. So kann Valgrind<br />

auf x86-Hosts lediglich SSE- und SSE2-Instruktionen erzeugen.<br />

• PUT- und GET-Instruktionen werden nicht zwangsläug als Registeroperationen umgesetzt.<br />

Wie in Abb. 3.5 zu erkennen ist, wird der Befehl PUT(20) = t28 zu MOV<br />

[EBP+0x14], EBX übersetzt. Tatsächlich werden auf x86 PUT-Instruktionen bei einer<br />

Quellgröÿe von 4 Byte als MOV-Operationen mit einer Zielspeicheradresse realisiert.<br />

In Bezug auf die Registerbehandlung lässt sich zusammenfassend behaupten: Dem<br />

Plug-In wird die ursprüngliche Registerbelegung vorenthalten, es ist für das Plug-In nicht<br />

abzusehen, welche Register zur Ausführung benutzt werden und auch nicht, zu welchem<br />

Zeitpunkt welche Daten überhaupt in Registern gehalten werden.<br />

Im folgenden Abschnitt wird beleuchtet, wie diese und andere Gegebenheiten sich auf<br />

die Wahl einer Strategie für die Erweiterung von FITIn auswirken.<br />

3.5 Evaluierung von Ansätzen<br />

Unabhängig von technischen Rahmenbedingungen, die etwa ein Framework wie Valgrind<br />

vorgibt, kommt eine zentrale Frage dabei auf, wenn man ein Werkzeug zur Bitmanipulation<br />

von Registern konzipieren möchte: Wie soll es benutzbar sein? Insbesondere vor dem Hintergrund,<br />

dass ein Anwender lediglich eine Bedienungsanleitung durchlesen möchte, und<br />

nicht den Quellcode des Instrumentierers, um dessen Anwendung hinreichend zu verstehen.<br />

In diesem Abschnitt werden zwei mögliche Ansätze vorgestellt, die einem Benutzer<br />

bei der Verwendung von FITIn zusätzlich zur bestehenden Funktionalität dazu dienen<br />

könnten, gezielt Bit-Flips auf Registern vorzunehmen.<br />

17

3 Erweiterung von FITIn<br />

1 unsigned char result = 0 x42 ;<br />

2 asm (" movl $7 , % eax ");<br />

3 asm (" movl %% eax , %0 ":"=m"(<br />

result ));<br />

4 printf ("%d\n" , result );<br />

1 MOV [ ESP +31] , 66<br />

2 MOV EAX , 7<br />

3 MOV BYTE PTR [ ESP +31] , EAX<br />

4 MOVZX EAX , BYTE PTR [ ESP +31]<br />

5 MOVZX EAX , AL<br />

6 MOV DWORD PTR [ ESP +4] , EAX<br />

7 MOV DWORD PTR [ ESP ],<br />

OFFSET FLAT : .LC0<br />

8 CALL printf<br />

Abbildung 3.6: Beispiel für Ansatz I, C-Programm (li.), VEX IR (re.)<br />

Ansatz I: Registerorientierter Bit-Flip<br />

Dem Benutzer steht zusätzlich zu den vorhandenen FITIn-Makros das Makro namens<br />

FITIN_FLIP_REG(reg) zur Verfügung. Das Argument ist eine Nummer, die abhängig von<br />

der Ausführungsplattform speziziert ist und auf den Index der Registerschattentabelle<br />

übersetzt wird. Der Benutzer fügt dieses Makro an der gewünschten Stelle im Quellcode seines<br />

Programms ein und wählt die Nummer des Registers, auf welchem zu diesem Zeitpunkt<br />

ein Bit-Flip vorgenommen werden soll. Zusätzlich wird per Kommandozeilenargument das<br />

Bit gewählt, das zu invertieren ist.<br />

Es sei in Abbildung 3.6 ein Minimalprogramm vorgestellt, das mittels Inline-Assembler<br />

sicherstellt, dass die Konstante 7 zuerst in das Register EAX und anschlieÿend in die Variable<br />

result kopiert wird. Die erwartete Ausgabe ist 7.<br />

Es sei folgendes Szenario gegeben: Der Benutzer möchte vor dem Zurückschreiben im<br />

Register EAX ein Bit umkehren. Dazu fügt er nun das Makro FITIN_FLIP_REG(0), wobei 0<br />

für das Register EAX speziziert sei, zwischen die beiden asm-Instruktionen ein. Abbildung<br />

3.7 zeigt den modizierten C-Code und die resultierenden x86-Instruktionen.<br />

1 unsigned char result = 0 x42 ;<br />

2 asm (" movl $7 , % eax ");<br />

3 FITIN_FLIP_REG (0) ;<br />

4 asm (" movl %% eax , %0 ":"=m"(<br />

result ));<br />

5 printf ("%d\n" , result );<br />

1 MOV BYTE PTR [ ESP +19] , 66<br />

2 MOV EAX , 7<br />

3 MOV DWORD PTR [ ESP +24] ,<br />

1179189257<br />

4 MOV DWORD PTR [ ESP +28] , 0<br />

5 MOV DWORD PTR [ ESP +32] , 0<br />

6 MOV DWORD PTR [ ESP +36] , 0<br />

7 MOV DWORD PTR [ ESP +40] , 0<br />

8 MOV DWORD PTR [ ESP +44] , 0<br />

9 LEA EAX , [ ESP +24]<br />

10 [ ... ]<br />

11 MOV EAX , DWORD PTR [ ESP<br />

+20]<br />

12 MOV BYTE PTR [ esp +19] , EAX<br />

13 [ ... ]<br />

Abbildung 3.7: Ansatz I: Zu x86-Programm (re.) kompilierter C-Code (li.)<br />

Die Zeilen 1, 2 und 12 des Assemblercodes gehören zum bewusst erzeugten Code, die<br />

Zeilen 3 bis 8 zeigen die Stack-Erweiterung, die durch den Valgrind Client Request erzeugt<br />

wird. Das Debakel wird deutlich, wenn man die Zeile 9 betrachtet: Ohne eine Sicherung<br />

von EAX wird der Wert 7 überschrieben, folglich wird ein anderer Wert ausgegeben.<br />

18

3.6 Erweiterung<br />

Ein derartiges Vorgehen erfordert, dass der Anwender ständig zu überprüfen hat, ob<br />

das gewählte Register nicht durch ein Valgrind-Makro überschrieben wurde. Schlieÿlich<br />

ist dem Compiler nicht bekannt, dass das Argument 0 des Makros den Registerinhalt von<br />

EAX bewahren soll. Die ganze Anwendung würde damit schon von vornherein ad absurdum<br />

geführt werden. Dieser Ansatz entpuppt sich als untauglich.<br />

Ansatz II: Bit-Flip nach Schreibzugrien auf Register<br />

Ein anderer Ansatz erfordert keine Modikation des Quellcodes. Stattdessen speziziert<br />

der Benutzer mittels Kommandozeile Register, Bit und Zeitpunkt des Schreibens: Die Erweiterung<br />

zählt die Vorkommen der PUT-Instruktionen in den zugelassenen SBs auf das<br />

angegebene Register und führt bei Übereinstimmung des Zählers mit der Spezikation<br />

nach dem Schreiben auf das Register einen Bit-Flip durch. Es sei in Abbildung 3.8 ein Beispiel<br />

gegeben: Der Benutzer möchte ein beliebiges Bit an Register ECX invertieren, nachdem<br />

die Konstante 15 hineingeschrieben wurde.<br />

1 unsigned char result = 0 x42 ;<br />

2 asm (" movl $15 , % ecx ");<br />

3 asm (" movl %% ecx , %0 ":"=m"(<br />

result ));<br />

4 printf ("%u\n , result )<br />

1 ------ IMark (0 x804846C , 5, 0) ----<br />

2 PUT (12) = 0 xF : I32<br />

3 PUT (68) = 0 x8048471 : I32<br />

4 ------ IMark (0 x8048471 , 4, 0) ----<br />

5 t8 = GET : I32 (24)<br />

6 t7 = Add32 (t8 ,0 x1F : I32 )<br />

7 STle ( t7 ) = 0 xF : I32<br />

8 PUT (68) = 0 x8048475 : I32<br />

Abbildung 3.8: Beispiel für Ansatz II, C-Programm (li.), VEX IR (re.)<br />

Erneut fällt ein Problem ins Auge, dieses Mal durch die Optimierung seitens Valgrind:<br />

Selbst wenn nach der Zeile 2 (in VEX IR) die Registerschattentabelle an Index 12 um ein<br />

Bit korrumpiert wurde, ndet der nächste sinngemäÿe Zugri auf Register ECX in Zeile 7<br />

statt, an welcher der Registerwert zurück an eine Speicheradresse geschrieben wird. Anstatt<br />

des Zugris auf das Register durch einen GET-Ausdruck ist an dieser Stelle die propagierte<br />

Konstante 0xF zu nden. Eine Manipulation der Registerschattentabelle bliebe hier somit<br />

ohne Auswirkung und die Ausgabe würde keine Veränderung erkenntlich machen.<br />

So existiert auch für diesen Ansatz ein Fall, der nicht das gewünschte Ergebnis liefert.<br />

Berücksichtigt man die bisher gewonnenen Erkenntnisse und die Tatsache, dass in Valgrind<br />

einzig der Datenussgraph der IRTemp zuverlässig die Programmsemantik abbildet, so muss<br />

man einen anderen Weg einschlagen. Dieser wird im nächsten Abschnitt vorgestellt.<br />

3.6 Erweiterung<br />

Dieser Abschnitt stellt die Implementierung vor, die FITIn dahingehend verändert, dass<br />

Bit-Flips nicht weiter vor dem Lesen des Arbeitsspeichers vorgenommen werden.<br />

Die vorherigen Analysen haben gezeigt, dass registerfokussierte Ansätze in Valgrind<br />

kein konsistentes Vorgehen für einen Bit-Flip auf einem Register ermöglichen. Die x86-<br />

Plattform verfügt darüber hinaus über mathematische Instruktionen, die Operanden nicht<br />

einmal in einem Register erwarten, sondern mittels Adresse direkt auf dem Prozessspeicher<br />

arbeiten. Dadurch fällt zusätzlich die Annahme, dass jede Ladeoperation der VEX IR<br />

ursprünglich die Kopie von Daten in ein Register darstelle.<br />

Es sei in Abbildung 3.9 ein x86-Beispiel gegeben, das das ursprüngliche FITIn an seine<br />

19

3 Erweiterung von FITIn<br />

Grenzen führt: Es sind drei ganzzahlige Variablen auf dem Stack gegeben, seien sie a, b<br />

und c genannt (für die Adressen EBP-12, EBP-8 und EBP-4). Die abgebildeten Operationen<br />

entsprechen in C-Code b += a; und c *= a;.<br />

1 MOV EAX , [ EBP -12]<br />

2 MOV EDX , [ EBP -8]<br />

3 ADD EDX , EAX<br />

4 MOV [ EBP -8] , EDX<br />

5 MOV EDX , [ EBP -4]<br />

6 IMUL EDX , EAX<br />

7 MOV [ EBP -4] , EDX<br />

1 ------ IMark (0 x80483EC , 1, 0) ----<br />

2 t0 = GET : I32 (28)<br />

3 t24 = GET : I32 (24)<br />

4 t23 = Sub32 (t24 ,0 x4 : I32 )<br />

5 [...]<br />

6 ------ IMark (0 x8048407 , 3, 0) ----<br />

7 t32 = Add32 (t23 ,0 xFFFFFFF4 : I32 )<br />

8 t34 = LDle : I32 ( t32 )<br />

9 [...]<br />

10 t10 = Add32 (t37 , t34 )<br />

11 [...]<br />

12 t17 = Mul32 (t34 , t43 )<br />

Abbildung 3.9: Grenzbeispiel für FITIn, x86-Programm (li.), VEX IR (re.)<br />

Zu erkennen ist, dass das Ergebnis des Ladevorgangs von a in das Register EAX mit dem<br />

IRTemp t34 beschrieben ist. t34 wird in diesem IRSB zwei Mal verwendet: als Argument<br />

der Anweisungen zur Addition Add32(t37,t34) und der Multiplikation Mul32(t34,t43)<br />

(analog stehen t37,t43 für a,b).<br />

Sei die Variable a vom Benutzer im Quellcode mit einem Makro versehen und sei der<br />

Fehlerinjektionszeitpunkt zur Operation b += a; gewählt: preLoadHelper wird vor der<br />

WrTmp-Instruktion von t34 eingefügt und nimmt zur Ausführungszeit den Bit-Flip auf dem<br />

Prozessspeicher vor, sodass alle zukünftigen Ladeoperationen auf dieser Adresse ebenfalls<br />

einen modizierten Wert lesen werden.<br />

Diese Implementierung stellt den Benutzer allerdings vor ein Problem, wenn der Bit-<br />

Flip erst vor Ausführung der Operation c *= a; stattnden soll. Auch wenn das Szenario<br />

gegeben sein kann, dass der Compiler a vor der zweiten Operation tatsächlich neu laden<br />

lässt, ist es wie hier bisher unmöglich, den im Register gehaltenen Wert erst bei erneuter<br />

Verwendung zu manipulieren.<br />

Betrachtet man jedoch die Tatsache, dass ein Plug-In in dieser VEX IR feststellen<br />

kann, wo t34 verwendet wird, so erönet sich eine deutlich präzisere Betrachtung des Variablenzugris.<br />

Zusätzlich verringert es die Notwendigkeit, dass der Benutzer zuerst durch<br />

Betrachtung der Assemblerausgabe oder durch Variieren der Quellcode-Annotation und<br />

des Manipulationszeitpunkts selbst ermitteln muss, ob Daten zu einem Zeitpunkt überhaupt<br />

erneut aus dem Speicher ausgelesen werden. Hier wird die Erweiterung von FITIn<br />

ansetzen.<br />

3.6.1 Betrachtete Operationen<br />

In diesem Unterabschnitt werden die technischen Gegebenheiten mit den Erkenntnissen<br />

über die zukünftige Benutzung von FITIn zusammen betrachtet und es wird erläutert,<br />

welche Arbeit notwendig ist, um eine möglichst allumfassende Lösung zu entwickeln.<br />

Die im nachfolgenden genannten Fälle von VEX IR-Vorkommen und Valgrind-Ereignissen<br />

sind für die Erweiterung von FITIn von Relevanz:<br />

• WrTmp-Instruktionen, die ein neues IRTemp durch einen Load-Ausdruck einführen. Das<br />

Plug-In hat zu erkennen, welche Ladeadresse verwendet wird und zu entscheiden, ob<br />

diese zu einer überwachten Speicheradresse gehört.<br />

20

3.6 Erweiterung<br />

• IRTemp-Variablen, auf die in einem RdTmp-Ausdruck zugegrien wird. Es muss zur<br />

Instrumentierung ermittelbar sein, ob ein verwendetes IRTemp einem Ladeausdruck<br />

entstammt. Zur Ausführungszeit muss erkannt werden, ob dabei auf ein Monitorable<br />

zugegrien wird. Im positiven Fall hat bei Erreichen des Zugriszählers der Bit-Flip<br />

vor der Ausführung zu erfolgen.<br />

• PUT-Instruktionen: Belegungen der Registerschattentabelle können über den SB hinaus<br />

verwendet werden, etwa für Systemaufrufe, aber auch intern für Hilfsmethoden<br />

von Valgrind. FITIn muss feststellen, ob eine solche Instruktion Daten, die von Interesse<br />

sind, in der Tabelle ablegt.<br />

• IRDirty-Aufrufe: Valgrind fügt selbstständig Hilfsaufrufe dieser Art ein, um Instruktionen<br />

zu behandeln, die nicht allein durch VEX IR abbildbar sind. Zu ermitteln ist,<br />

ob diese lesend auf die Registerschattentabelle oder den Prozessspeicher zugreifen.<br />

In einem solchen Fall ist zu prüfen, ob es sich dabei um relevante Datenbereiche<br />

handelt, um zuvor gegebenenfalls einen Bit-Flip auszuführen. Dieser Fall blieb von<br />

FITIn bisher unberücksichtigt.<br />

• Systemaufrufe: Systemaufrufe wurden von FITIn bisher ebenso ignoriert. Das Plug-<br />

In muss bei Valgrind entsprechende Callbacks eintragen, die vor dem Lesen eines<br />

Registers oder des Prozessspeichers den Zugri analysieren, um eventuell eine Fehlerinjektion<br />

vorzunehmen.<br />

3.6.2 Instrumentierungszeit<br />

Die Datenstrukturen, die FITIn bereits enthält, können beibehalten werden: Monitorable<br />

als Repräsentation einer Speicheradresse, die überwacht werden soll aber auch deaktiviert<br />

werden kann und toolData, das die gesamte Konguration von FITIn sowie Datenstrukturen<br />

zur Ausführungszeit enthält, beispielsweise eine Liste aller Monitorable, die vom<br />

Typ XArray ist. Es existiert von dieser Struktur innerhalb von fi_main.c eine globale<br />

Variable mit dem Namen tData. Da andere C-Dateien auf diese allerdings keinen Zugri<br />

haben, wird tData vielen Funktionen der Erweiterung als Argument übergeben.<br />

XArray ist eine Datenstruktur, die von Valgrind bereitgestellt und auch für die Erweiterung<br />

von FITIn benutzt wird. Es handelt sich dabei um eine sortierbare Liste, an deren<br />

Ende Elemente eingefügt werden können. Die Operationen addToXA(XArray*, void*) und<br />

indexXA(XArray*, Word), zum Einfügen und indexbasierten Zugri, liegen in O(1). Eine<br />

schlüsselbasierte Nutzung setzt voraus, dass das XArray nach jeder Veränderung sortiert<br />

wird. Der Suchaufwand von lookupXA(XArray *array, void *key, Word *first, Word<br />

*last) beträgt O(log n).<br />

Die Instrumentierung ndet nach wie vor im Aufruf des Callbacks fi_instrument in<br />

fi_main.c statt. Viele Prozeduren, die für die Erweiterung der Instrumentierung erschaen<br />

wurden, benden sich in der Datei fi_reg.c, die Prototypen der öentlichen Methoden in<br />

fi_reg.h.<br />

Der erste Schritt zur Instrumentierung ist das Finden von WrTmp-Instruktionen, deren<br />

IRExpr vom Typ Load ist. Da die Adresse des Ladevorgangs jedoch nicht zwangsläug zur<br />

Instrumentierung ermittelbar ist und, viel wichtiger, die Menge der Monitorable erst zur<br />

Laufzeit bekannt ist, muss die Untersuchung zur Ausführungszeit erfolgen. Dieses Suchmuster<br />

ist von FITIn bereits gegeben und der eingefügte IRDirty-Aufruf preLoadHelper<br />

bleibt beibehalten. Vor der Erweiterung war die Methode preLoadHelper das Herzstück des<br />

Plug-Ins, da diese das Nachschlagen der Ladeadresse der folgenden Instruktion und auch<br />

den Bit-Flip übernahm. Der Erweiterungsansatz sieht jedoch nicht weiter vor, dass zum<br />

Zeitpunkt unmittelbar vor einem Speicherzugri ein Fehler injiziert wird. Die Fehlerinjek-<br />

21

3 Erweiterung von FITIn<br />

1 typedef struct {<br />

2 IRTemp dest_temp ;<br />

3 IRType ty ;<br />

4 IRExpr * addr ;<br />

5 IRTemp state_list_index ;<br />

6 } LoadData ;<br />

Abbildung 3.10: C-Struktur: LoadData<br />

tion wurde daher entfernt. Eine Änderung betrit jedoch den Rückgabewert: preLoadHelper<br />