Technische Grundlagen der Informatik I 3. Poolraumübung

Technische Grundlagen der Informatik I 3. Poolraumübung

Technische Grundlagen der Informatik I 3. Poolraumübung

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Prof. Dr.-Ing. Sorin A. Huss<br />

<strong>Technische</strong> <strong>Grundlagen</strong> <strong>der</strong> <strong>Informatik</strong> I<br />

<strong>3.</strong> Poolraumübung<br />

Wintersemester 2010/11<br />

Aufgabe 1 Multiplexer in VHDL<br />

Diese Aufgabe soll den Unterschied zwischen verhaltensorientierter und funktionaler Beschreibung von Schaltungen in<br />

VHDL anhand eines einfachen Beispiels aufzeigen.<br />

Aufgabe 1.1 M UX 6 mittels verhaltensorientierter Beschreibung<br />

VHDL bietet eine Reihe an Statements, die genutzt werden können, um einen Multiplexer mit nur einem dieser Statements<br />

zu beschreiben. Nennen Sie zwei dieser Statements und erklären Sie, welches Statement Sie zur Beschreibung<br />

eines Multiplexers nutzen würden.<br />

Beschreiben Sie nun einen Multiplexer M UX 6 in VHDL, welcher sechs Eingänge (a bis f), in Abhängigkeit von einem<br />

Selektierungssignal sel einzeln auf einen Ausgang q legt. Nutzen Sie hierzu das Statement, welches Ihrer Meinung nach<br />

am besten geeignet ist.<br />

Welche Breite muss das Selektierungssignal mindestens aufweisen, um alle Eingänge schalten zu können?<br />

Aufgabe 1.2 M UX 6 mittels funktionaler Beschreibung<br />

Ein M UX 2 dessen Eingänge (a,b) mittels eines Selektierungssignals (sel) jeweils einzeln auf den Ausgang q geschaltet<br />

werden können, kann wie folgt funktional Beschrieben werden.<br />

q := (a ∧ ¬sel) ∨ (b ∧ sel) (1)<br />

Entwickeln Sie nun die funktionale Beschreibung eines M UX 6 Multiplexers. Die Eingänge tragen die Bezeichnungen a<br />

bis f, das Selektierungssignal die Bezeichnung sel und das Ausgangssignal die Bezeichnung q.<br />

Implementieren Sie anschließend die funktionale Beschreibung als zweite Architecture für die in Aufgabe 1.1 vorgegebene<br />

Entity.<br />

Aufgabe 1.3 3-Bit-M UX 6<br />

Kombinieren Sie nun mehrere Ihrer M UX 6 Multiplexer zu einem 3-Bit-M UX 6 Multiplexer und zeigen Sie das korrekte<br />

Verhalten anhand einer Simulation auf.<br />

Aufgabe 2 Tasten entprellen in VHDL<br />

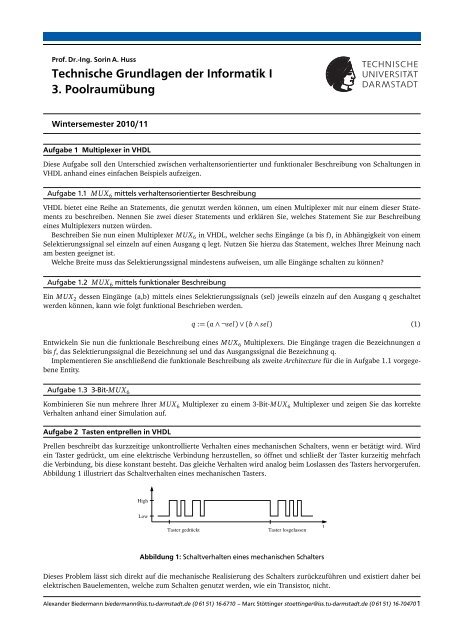

Prellen beschreibt das kurzzeitige unkontrollierte Verhalten eines mechanischen Schalters, wenn er betätigt wird. Wird<br />

ein Taster gedrückt, um eine elektrische Verbindung herzustellen, so öffnet und schließt <strong>der</strong> Taster kurzeitig mehrfach<br />

die Verbindung, bis diese konstant besteht. Das gleiche Verhalten wird analog beim Loslassen des Tasters hervorgerufen.<br />

Abbildung 1 illustriert das Schaltverhalten eines mechanischen Tasters.<br />

High<br />

Low<br />

Taster gedrückt<br />

Taster losgelassen<br />

t<br />

Abbildung 1: Schaltverhalten eines mechanischen Schalters<br />

Dieses Problem lässt sich direkt auf die mechanische Realisierung des Schalters zurückzuführen und existiert daher bei<br />

elektrischen Bauelementen, welche zum Schalten genutzt werden, wie ein Transistor, nicht.<br />

Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de (0 61 51) 16-6710 – Marc Stöttinger stoettinger@iss.tu-darmstadt.de (0 61 51) 16-704701

Eine Möglichkeit, um einen Schalter zu entprellen, ist in Abbildung 2 skizziert. Mittels eines Taktes wird das zu<br />

entprellende Schaltsignal abgetastet und einem n-Bit-Schieberegister zugeführt. Das Schieberegister wird in diesem Fall<br />

als n-Bit-Seriell-Parallel-Wandler genutzt und ermöglicht es somit, jeweils n Bit parallel abzugreifen und einem n-Bit-<br />

UND-Gatter zu übergeben. Wurde <strong>der</strong> Taster gedrückt, um eine elektrische Verbindung zu schließen, so bestätigt diese<br />

Schaltung die geschlossene Verbindung erst, wenn die Verbindung konstant besteht.<br />

clock<br />

n bit shift register<br />

0 0 1 1 0 ...<br />

t<br />

...<br />

0<br />

1<br />

1<br />

0<br />

0<br />

&<br />

Taster gedrückt?<br />

Abbildung 2: Möglichkeit zum entprellen eines Schalters<br />

Aufgabe 2.1 Implementierung in VHDL<br />

Implementieren Sie die in Abbildung 2 skizzierte Schaltung in VHDL. Ihre Schaltung soll in <strong>der</strong> Lage sein, den in <strong>der</strong><br />

beigefügten Testbench simulierten geprellten Taster zu entprellen. Hierbei wurde <strong>der</strong> geprellte Taster jeweils einmal vor<br />

600 ns und jeweils einmal danach betätigt. Damit Ihre Entity kompatibel zu <strong>der</strong> Testbench ist, wird Ihnen die folgende<br />

Entity vorgegeben.<br />

e n t i t y contact_bounce i s<br />

Port ( c l k : in STD_LOGIC ;<br />

r s t : in STD_LOGIC ;<br />

rawdata : in STD_LOGIC ;<br />

ispushed : out STD_LOGIC ) ;<br />

end contact_bounce ;<br />

Die Testbench legt an dem Eingang rawdata das unentprellte Schaltverhalten des Tasters an und Ihre Implementierung<br />

setzt den Ausgang ispushed auf logisch High gdw. ein gedrückter Taster erkannt wurde.<br />

Aufgabe 2.2 Auswertung <strong>der</strong> Implementierung<br />

Aufgabe 2.2.1 Welche Breite muss das eingesetzte Schieberegister haben, um den Taster korrekt zu entprellen?<br />

Aufgabe 2.2.2 Was passiert, wenn das Schieberegister diese Breite unterschreitet?<br />

Aufgabe 2.2.3 Was passiert, wenn das Schieberegister diese Breite überschreitet?<br />

2Alexan<strong>der</strong> Bie<strong>der</strong>mann bie<strong>der</strong>mann@iss.tu-darmstadt.de (0 61 51) 16-6710 – Marc Stöttinger stoettinger@iss.tu-darmstadt.de (0 61 51) 16-70470