Ein zeitkontinuierlicher Sigma-Delta Modulator mit ... - DGBMT

Ein zeitkontinuierlicher Sigma-Delta Modulator mit ... - DGBMT

Ein zeitkontinuierlicher Sigma-Delta Modulator mit ... - DGBMT

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Ein</strong> <strong>zeitkontinuierlicher</strong> <strong>Sigma</strong>-<strong>Delta</strong> <strong>Modulator</strong> <strong>mit</strong><br />

Stromquellen-Rückkopplung und reduzierter Clock-Jitter<br />

Empfindlichkeit<br />

Maurits Ortmanns, Friedel Gerfers, Yiannos Manoli<br />

Albert-Ludwigs-Universität, Lehrstuhl für Mikroelektronik<br />

D-79110 Freiburg. maurits@imtek.uni-freiburg.de<br />

Abstract<br />

In diesem Paper wird eine vorher nicht veröffentlichte Technik für die Reduktion der Clock-Jitter<br />

Empfindlichkeit <strong>zeitkontinuierlicher</strong> <strong>Sigma</strong>-<strong>Delta</strong> <strong>Modulator</strong>en vorgestellt. Hierzu wird die Haupt-Fehlerquelle, der<br />

Rückkopplungs-Digital/Analog Umsetzer durch eine abfallende Pulsform realisiert, die von einer Transistor-Stromquelle<br />

und einer steuernden <strong>Ein</strong>heit erzeugt wird. In dieser ersten Implementierung wurde ein <strong>zeitkontinuierlicher</strong><br />

<strong>Modulator</strong> dritter Ordnung entworfen, der ¼ Dynamikbereich erreicht und dabei nur ¾¼Ï aus einer ½Î<br />

Spannungsversorgung verbraucht; gleichzeitig konnte die Jitter-Empfindlichkeit merklich reduziert werden.<br />

1. <strong>Ein</strong>führung<br />

In abgetasteten Systemen führt ein zeitliches Jitter des<br />

Systemtaktes zu einer uneinheitlichen Abtastung, was in<br />

Rauschquellen unterschiedlichster Art und Form resultiert.<br />

In zeitdiskreten (DT) <strong>Sigma</strong>-<strong>Delta</strong> (¦¡) <strong>Modulator</strong>en,<br />

die üblicherweise in Schalter-Kondensator (SC) Technik<br />

implementiert werden, ist die Variation der übertragenen<br />

Ladungsmenge pro Taktzyklus relativ niedrig, da diese<br />

<strong>Modulator</strong>en <strong>mit</strong> niedriger <strong>Ein</strong>schwingzeit ausgeführt<br />

werden. Dies wiederum führt dazu, dass der größte Teil<br />

der auf den Kapazitäten gespeicherten Ladung zu Beginn<br />

einer Taktperiode verarbeitet, d.h. übertragen wird [1].<br />

Deshalb liegt die Hauptfehlerquelle durch Clock-Jitter in<br />

DT <strong>Modulator</strong>en am Abtasthalteglied des <strong>Ein</strong>gangs, wo<br />

ein zeitlicher Abtastfehler zu einem äquivalenten Amplitudenfehler<br />

des Abtastsignals wird. Für ein unkorreliertes,<br />

Gauss-verteiltes Takt-Jitter <strong>mit</strong> einer Standardabweichung<br />

von Ø ¾ , ist diese dominante Rauschleistung proportional<br />

<br />

zu<br />

¾ <br />

ÇËÊ<br />

, wobei OSR die Überabtastrate des <strong>Modulator</strong>s<br />

¿<br />

ist [1].<br />

Neben diesen zeitdiskreten <strong>Modulator</strong>en ist in den letzten<br />

Jahren die Anzahl der Publikationen über die so genannten<br />

zeitkontinuierlichen ¦¡ <strong>Modulator</strong>en stetig angestiegen,<br />

wobei gleichzeitig auch das industrielle Interesse<br />

wächst. Dies ist vor allem durch die wesentlichen Vorteile<br />

gegenüber den DT Implementierungen begründet:<br />

ein implizites Anti-Aliasing-Filter, die Verlagerung des<br />

Abtastprozesses ins Innere des <strong>Modulator</strong>s, sowie Geschwindigkeitsvorteile<br />

bezüglich der aktiven Elemente,<br />

was schließlich auch zu extrem niedrigen Verlustleistungen<br />

führt [2] [3] [4].<br />

Diese Vorteile werden jedoch erkauft <strong>mit</strong> einer schlechteren<br />

Synthesisierbarkeit und vor allem <strong>mit</strong> einer erhöhten<br />

Empfindlichkeit gegenüber nichtidealen Eigenschaften,<br />

insbesondere dem erwähnten Takt-Jitter.<br />

Im Gegensatz zu den DT <strong>Modulator</strong>en ist bei den<br />

Ë<br />

ٴص Ê <br />

ܴص<br />

Ü´Òµ Ý´Òµ<br />

Ê<br />

ݴص<br />

¦Î Ö<br />

<br />

ݴص<br />

Ì Ë<br />

Ø<br />

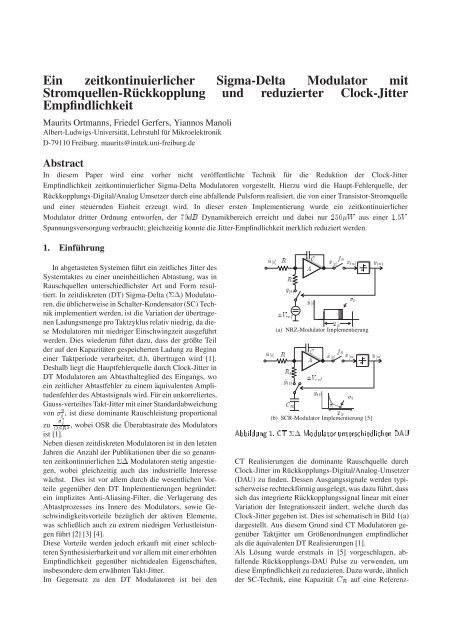

(a) NRZ-<strong>Modulator</strong> Implementierung<br />

ٴص Ê<br />

<br />

Ë<br />

ܴص ܴҵ ݴҵ<br />

Ê Ê<br />

ݴص<br />

Ê<br />

<br />

¦Î Ö<br />

ݴص<br />

<br />

Ì Ë<br />

Ø<br />

(b) SCR-<strong>Modulator</strong> Implementierung [5]<br />

ÐÙÒ ½º Ì ¦¡ ÅÓÙÐØÓÖ ÙÒØÖ×ÐÒ Í<br />

CT Realisierungen die dominante Rauschquelle durch<br />

Clock-Jitter im Rückkopplungs-Digital/Analog-Umsetzer<br />

(DAU) zu finden. Dessen Ausgangssignale werden typischerweise<br />

rechteckförmig ausgelegt, was dazu führt, dass<br />

sich das integrierte Rückkopplungssignal linear <strong>mit</strong> einer<br />

Variation der Integrationszeit ändert, welche durch das<br />

Clock-Jitter gegeben ist. Dies ist schematisch in Bild 1(a)<br />

dargestellt. Aus diesem Grund sind CT <strong>Modulator</strong>en gegenüber<br />

Taktjitter um Größenordnungen empfindlicher<br />

als die äquivalenten DT Realisierungen [1].<br />

Als Lösung wurde erstmals in [5] vorgeschlagen, abfallende<br />

Rückkopplungs-DAU Pulse zu verwenden, um<br />

diese Empfindlichkeit zu reduzieren. Dazu wurde, ähnlich<br />

der SC-Technik, eine Kapazität Ê auf eine Referenz-

Ï<br />

Ä Ô½<br />

Ï<br />

Ä Ò½<br />

Ï<br />

Ä<br />

ËÊ Ï<br />

Ô¾<br />

Ä<br />

Ô½ ËÊ Ô¿<br />

Ô¾ ËÊ Ô¿<br />

¾ ½<br />

¿<br />

ÁÒ Ô<br />

Ê ½ ÁÒØ ½ Ê ¾ ÁÒØ ¾ Ê ¿ ÁÒØ ¿<br />

ÁÒ Ò<br />

½<br />

¾<br />

¿<br />

ËÊ Ò½ ËÊ Ò¾ ËÊ Ò¿<br />

Ï<br />

Ä Ï<br />

Ò¾<br />

Ä Ò¿<br />

(a) Architektur des voll-differentiellen <strong>Modulator</strong>s<br />

ÃÓÑÔ<br />

² <br />

ÐÓ<br />

ÇÙØ<br />

¨<br />

Ê<br />

Î <br />

¨<br />

Î ÐÓÛ<br />

¨<br />

¨<br />

ÇÔÑÔ ÁÒÔÙØ <br />

Î Å ¼ÑÎ<br />

Ê Ê<br />

(b) SCR-I - Schaltung<br />

ÐÙÒ ¾º ÖØØÙÖ × ÅÓÙÐØÓÖ× ¿ Ö ÇÖÒÙÒ ÑØ ËʹÁ ÊĐÙÓÔÔÐÙÒ<br />

Á Ò <br />

Î ÐÓÛ Ò<br />

spannung aufgeladen, um dann im Rückkopplungszeitraum<br />

über einen zusätzlich integrierten Widerstand Ê Ê<br />

auf den Integrator-<strong>Ein</strong>gang entladen zu werden. Da<strong>mit</strong><br />

wird ein exponentiell abfallender Rückkopplungspuls exakt<br />

bestimmt, und zwar einmal durch die Zeitkonstante<br />

Ê Ê Ê und zum zweiten durch den begrenzenden<br />

Widerstand Ê Ê , der zusammen <strong>mit</strong> der Referenzspannung<br />

den Maximalwert des Strompulses bestimmt. Die<br />

entsprechende Schaltung wurde SCR-Rückkopplung benannt<br />

und ist im Bild 1(b) dargestellt. <strong>Ein</strong>e weiterführende<br />

theoretische Betrachtung zur Synthese wird in [6] gegeben,<br />

während in [7] die erste implementierte Schaltung<br />

vorgestellt wurde.<br />

Nichtsdestotrotz wird diese Technik von einigen<br />

Nichtidealitäten begleitet: <strong>Ein</strong> endliches Verstäkungs-<br />

Bandbreite-Produkt der Operationsverstärker (ÇÔÑÔ)<br />

verursacht eine Verlangsamung des Entladeprozesses, da<br />

der Integrator-Ausgang dem schnellen <strong>Ein</strong>gangspuls nicht<br />

folgen kann [8]. Deshalb erscheint die Pulsflanke langsamer<br />

als berechnet und die Empfindlichkeit gegenüber dem<br />

Takt-Jitter erhöht sich.<br />

Darüberhinaus erschwert sich die Implementierung eines<br />

<strong>Modulator</strong>s <strong>mit</strong> interner Multi-Bit Quantisierung durch<br />

die Verwendung der SCR-Technik: Multi-Bit Quantisierung<br />

wird eingesetzt, um die Auflösung und Stabilität<br />

eines <strong>Modulator</strong>s zu erhöhen, erfordert jedoch einen sehr<br />

linearen Rückkopplungs-DAU, was üblicherweise durch<br />

Linearisierungstechniken wie das ÝÒÑ ÐÑÒØ<br />

ÅØÒ (DEM) erreicht wird. Diese Technik ist jedoch<br />

nicht einfach auf den SCR-DAU übertragbar, da in<br />

diesem Fall 2 unterschiedliche Elemente in der Rückkopplung<br />

verwendet werden ( Ê ² Ê Ê ), die beide im<br />

Bereich der Auflösung des <strong>Modulator</strong>s abgestimmt, d.h.<br />

linearisiert werden müßten. Die DEM-Techniken basieren<br />

jedoch auf nur einem Rückkopplungselement.<br />

Dementsprechend wird in diesem Paper eine Alternative<br />

zur SCR-Technik vorgeschlagen, die auf der Implementierung<br />

des Rückkopplungs-DAU durch Transistorstromquellen<br />

basiert, die von einer abfallenden Spannungsflanke<br />

gesteuert werden. Da<strong>mit</strong> wird es möglich, die genannten<br />

Nachteile der SCR-Technik zu umgehen. In diesem<br />

Paper wird die prinzipielle Funktionalität dieser neuen<br />

Technik präsentiert.<br />

In Kapitel 2 wird ein Überblick über den vorgschlagenen<br />

Strom-DAU <strong>mit</strong> abfallender Flanke gegeben. Die Synthese<br />

und Implementierung des hier vorgestellten <strong>Modulator</strong>s<br />

¿ Ö Ordnung wird in Kapitel 3 gezeigt, während Kapitel 4<br />

die erhaltenen Messergebnisse präsentiert. Kapitel 5 behandelt<br />

die auftretenden Nichtidealitäten und Kapitel 6<br />

enthält eine kurze Zusammenfassung.<br />

2. Die SCR-I Rückkopplungstechnik<br />

Wie schon einleitend erwähnt, birgt der <strong>Ein</strong>satz der<br />

SCR-Technik, also die Generierung eines abfallenden<br />

DAU-Spannungpulses durch Entladung einer Kapazität<br />

über einen Widerstand auf den Integratoreingang einige<br />

nichtideale Eigenschaften, darunter die Abhängigkeit<br />

des Entladungsprozesses vom virtuellen Masseknoten am<br />

<strong>Ein</strong>gang der OpAmp [8] und zusätzlich die umständliche<br />

oder gar unmögliche Implementierung einer DEM-<br />

Technik für die nun 2 vorhandenen Rückkopplungselemente.<br />

Deshalb wird hier vorgeschlagen eine Stromquellen-<br />

Rückkopplung zu verwenden, deren Steuerspannung als<br />

abfallende Flanke ausgebildet ist, wobei diese Flanke linear,<br />

exponentiell oder andersartig sein kann. Da<strong>mit</strong> wird<br />

das Rückkopplungssignal unabhängig vom <strong>Ein</strong>gangsknoten<br />

des Integrators, die Jitterempfindlichkeit unabhängig<br />

vom OpAmp und zusätzlich wird die Implementierung<br />

eines Multi-Bit Rückkopplungs-DAC sehr einfach, da nur<br />

noch ein Stromquellenarray linear abzustimmen ist.<br />

<strong>Ein</strong>e schematische Darstellung der vorgeschlagenen Technik<br />

ist in Abb. 2(a) für den hier präsentierten <strong>Modulator</strong><br />

¿ Ö Ordnung gezeigt: die Rückkopplungssignale werden<br />

von Transistor-Stromquellen generiert, deren Gate-<br />

Steuerspannung als abfallende Spannungen anliegen.<br />

Um einen zu [7] vergleichbaren <strong>Modulator</strong> zu erhalten<br />

werden diese Steuerspannungen ähnlich der ursprünglichen<br />

SCR-Technik exponentiell von einer Kapazitäts-<br />

Widerstands-Anordnung gebildet, die in Abb. 2(b) gezeigt<br />

ist. Hier wird die Kapaztität in der ersten Takthälfte<br />

(¨) auf eine Anfangsspannung Î aufgeladen, welche<br />

den anfänglichen Strompeak erzeugen soll. In der zweiten

Takthälfte (¨) wird die Kapazität über den Widerstand exponentiell<br />

auf eine Endspannung Î ÐÓÛ entladen, und zwar<br />

<strong>mit</strong> einer Zeitkonstanten Î Ê Ê Ê . In Anlehnung an<br />

[7] wurde die resultierende Rückkopplungsstruktur SCR-I<br />

Technik benannt.<br />

3. <strong>Modulator</strong> Synthese<br />

Üblicherweise wird die Synthese eines zeitkontinuierlichen<br />

¦¡ <strong>Modulator</strong>s auf Grundlage einer DT-to-<br />

CT Transformation durchgeführt, wodurch CT Integrator-<br />

Skalierungskoeffizienten so berechnet werden, dass eine<br />

CT-DT <strong>Modulator</strong>-Äquivalenz erreicht wird [3]. Dies<br />

wurde in [7] unter Zuhilfenahme der Berechnungen in [6]<br />

für einen SCR-<strong>Modulator</strong> durchgeführt. Durch die ähnliche<br />

Form der Rückkopplungspulse kann diese Methode<br />

auch für den hier vorgestellten <strong>Modulator</strong> genutzt werden.<br />

Um eine spürbare Verminderung der Empfindlichkeit gegenüber<br />

Takt-Jitter zu erreichen wurden die Zeitkonstanten<br />

der Rückkopplungspulse wie folgt gewählt:<br />

Á½ ± Ì Ë Á¾ ½¼± Ì Ë Á¿ ½¼± Ì Ë (1)<br />

wobei Ì Ë die Abtastzeit des <strong>Modulator</strong>s ist. Da<strong>mit</strong> können<br />

wie in [7] und [6] die Skalierungskoeffizienten der Integratoren<br />

bestimmt werden:<br />

Ëʽ ½ Ëʾ ¿ ËÊ¿ (2)<br />

Die Aufgabe besteht nun darin, aus diesen Skalierungskoeffizienten<br />

die Dimensionierung der Rückkopplungselemente<br />

zu bestimmen, was im Fall der abfallenden<br />

Stromquellen-Rückkopplung schwieriger ist, als für die<br />

reine SCR-Technik in [7]. Der Grund hierfür ist, dass der<br />

Transformationsprozess in [6] für exponentiell abfallende<br />

Rückkopplungspulse entwickelt wurde, deren Endwert<br />

gegen Null tendiert. Im Fall der SCR-I Rückkopplung<br />

werden diese Pulse aber von Stromquellen erzeugt, deren<br />

unterer Grenzwert von der Referenzspannung Î ÐÓÛ in<br />

Abb. 2(b) abhängt.<br />

Deshalb stellt sich die Frage, wie die Größe dieses Endspannungswertes<br />

gewählt werden kann, der nach obigen<br />

Überlegungen die Stromquelle vollständig abschalten<br />

sollte. Dies ist prinzipiell nur durch eine vollständige<br />

’Abschaltung’ der Transistor-Gates möglich, was jedoch<br />

gewöhnlich vermieden wird, weil es die Stromquelle sehr<br />

weit in die schwache Inversion führt. Dabei würde der<br />

Rückkopplungsstrom nicht mehr rein exponentiell verlaufen<br />

und da<strong>mit</strong> der Transformation nach [6] widersprechen.<br />

Der <strong>Ein</strong>fachheit halber wurde deshalb das einfachste Transistormodel<br />

der starken Inversion angenommen, nach dem<br />

der Transistorstrom versiegt, wenn die effektive Gate-<br />

Source-Spannung Î × ¼ ist. Dann kann die ’untere’<br />

Referenzspannung Î ÐÓÛ in Abb. 2(b) als Threshold-<br />

Spannung Î Ø des entsprechenden Rückkopplungstransistors<br />

gewählt werden.<br />

Da<strong>mit</strong> erhält man für den Rückkopplungsstrompuls:<br />

Á ¬ ¼ Ï<br />

ÐÓÛ <br />

¾ Ä Î ¡ ¾<br />

× ÐÓÛ Î Ø (3)<br />

Î × ÐÓÛ Î × ¡ ÜÔ ØÈ Î (4)<br />

worin Î × die Gate-Source Spannungen der Stromquellen<br />

und Á ÐÓÛ die obere und untere Grenze des Rückkopplungsstroms<br />

sind. Ø È Ì Ë ¾ entspricht der Dauer<br />

des Pulses. Durch die quadratische Abhängigkeit des<br />

Transistorstroms von der entsprechenden Gatespannung<br />

halbiert sich die Zeitkonstante des Strompulses im Vergleich<br />

zur Zeitkonstante der Steuerspannung und da<strong>mit</strong><br />

der RC-Schaltung in Abb. 2(b), weshalb diese gegenüber<br />

dem gewünschten Designziel in Gl. 1 verdoppelt werden<br />

muss.<br />

Á Î<br />

¾<br />

Ê<br />

¾<br />

(5)<br />

Î × ÐÓÛ Î × ¡ ÜÔ Ì Ë ¾<br />

¾ Á (6)<br />

Unter Berücksichtigung der Verhältnisse der Widerstände,<br />

Kapazitäten und Skalierungskoeffizienten an jedem Integrator,<br />

¡ Ë ½<br />

Ê <br />

, sowie <strong>mit</strong> der Umformung<br />

Á Î Ê<br />

Ê <br />

, wobei Á der Rückkopplungsstrom-Peak und<br />

Î Ê die Referenzspannung des <strong>Modulator</strong>s ist, können<br />

die Rückkopplungsstromquellen folgendermassen skaliert<br />

werden:<br />

Á ¡ Î Ê ¡ Ë ¡ (7)<br />

Ï<br />

Ä ¾ Î Ê Ë <br />

¬ ¼ Î × <br />

(8)<br />

Mit <strong>Modulator</strong>-Spezifikationen wie in [4] und [7]:<br />

½ Ô ¾ ¿ ½Ô (9)<br />

Î Ê ¼ÑÎ Ë ¾ÅÀÞ<br />

und einer gewählten Peak-Steuerspannung in Abb. 2(b)<br />

Î Ò ¿¼¼ÑÎ · Î Ø Ò und Î Ô Î <br />

¿¼¼ÑÎ · Î Ø Ô , wobei Î ÐÓÛ Ò Î Ø Ò und Î ÐÓÛ Ô <br />

Î Î Ø Ô , erhält man für die Transistorskalierung in<br />

Abb. 2(a):<br />

Ï<br />

Ä Ò½ ½<br />

Ï<br />

Ä Ò¾ ½<br />

Ï<br />

Ä Ò¿ ¾¿ (10)<br />

wobei die p-Kanal-Transistoren um einen Faktor ¬Ò<br />

¬ Ô<br />

<br />

breiter gewählt werden müssen.<br />

Nach diesen Spezifikationen und einer Architektur wie<br />

in Abb. 2(a) wurde ein <strong>Modulator</strong> ¿ Ö Ordnung in einer<br />

¿¿Î ¼Ñ Standard CMOS Technologie entworfen.<br />

Das Signalbasisband wurde zu ¾ÀÞ, die<br />

Überabtastung zu ÇËÊ gewählt [4] [7]. Das Chip-<br />

Photo der Schaltung ist in Abb. 3 gezeigt. Der entworfene<br />

<strong>Modulator</strong> verbraucht nur ¾¼Ï aus einer ½Î<br />

Spannungsversorgung. Die Kern-Chipfläche beträgt weniger<br />

als ½¾ÑÑ ¾ .

×Ö ÅÓÙÐØÓÖ<br />

ËÆÊ ËÆÊ ℄<br />

¼<br />

¼<br />

¼<br />

¼<br />

¿¼<br />

¾¼<br />

Ñ××ÒÖ ËÆÊ<br />

Ñ××ÒÖ ËÆÊ<br />

ÖÛØÖØÖ È ÐÓØ<br />

4. Messergebnise<br />

ÐÙÒ ¿º Ô¹ÈÓØÓ<br />

Der so implementierte <strong>Modulator</strong> <strong>mit</strong> SCR-I Rückkopplung<br />

wurde sowohl bezüglich seiner generellen Performance<br />

vermessen, um die Funktionalität des ¦¡ <strong>Modulator</strong>s<br />

¿ Ö Ordnung <strong>mit</strong> der neuen Rückkopplungstechnik<br />

zu zeigen, als auch bezüglich der Empfindlichkeit<br />

gegenüber Takt-Jitter, was das eigentliche Ziel der Struktur<br />

ist. Für alle Messungen wurde der 1-bit Ausgangsdatenstrom<br />

<strong>mit</strong> Hilfe eines Logic-Analyzers (ÀȽ¼¼)<br />

aufgenommen. Daraus wurde dann eine Ì <strong>mit</strong>tels<br />

ÅÌÄ berechnet. Der Clock-Jitter Messaufbau<br />

wurde gewählt, wie in [7] beschrieben.<br />

Abb. 4 zeigt ein so erhaltenes Leistungsdichtespektrum<br />

(LDS) des <strong>Modulator</strong>s <strong>mit</strong> SCR-I Rückkopplung für ein<br />

<strong>Ein</strong>gangssignal bei ÀÞ. Zusätzlich ist das integrierte<br />

Inband-Rauschen (ÁÆ) gegeben. Es ist offensichtlich,<br />

dass der Pegel des weissen Rauschens den dynamischen<br />

Bereich bestimmt, was in einem Inband-Rauschen von etwa<br />

ÁÆ ¼ resultiert. In [4] waren dies <br />

für eine Non-Return-to-Zero Implementierung und in [7]<br />

¼ für die SCR Implementierung. Der Grund für die-<br />

ÄË ℄<br />

¼<br />

¼<br />

½¼¼<br />

½¼<br />

ÄË × ËÊ Á<br />

ÁÒØÖ ÁÒÒ ÊÙ×Ò<br />

½¼ ¾ ½¼ ½¼ <br />

ÖÕÙÒÞ ÀÞ℄<br />

<br />

<br />

ÐÙÒ º Ä×ØÙÒ×عËÔØÖÙÑ<br />

sen Anstieg des IBN kann durch eine grobe Abschätzung<br />

des weissen Rauschstroms der Stromquellen der ersten<br />

Rückkopplungsschleife gefunden werden:<br />

¾ ÒØ ¿ Ì<br />

½<br />

ÑÒ<br />

<br />

¾<br />

¾<br />

ÀÞ<br />

(11)<br />

wobei Ì ¿¼¼Ã sowie die Boltzman Konstante<br />

ist, und die Trankonduktanz ÑÒ aus den Gleichungen<br />

2, 7 und 10 berechnet werden kann. Dabei gilt für<br />

½¼<br />

¼<br />

¼<br />

¼<br />

¼<br />

Î Ò<br />

Î<br />

℄<br />

Ö<br />

ÐÙÒ º ËÒйÊÙ×¹´×ØÓÖØÓÒµ¹×ØÒ<br />

¬ Ò ½¼¼ <br />

Î ¾ . Durch Multiplikation der Rauschstromdichte<br />

<strong>mit</strong> dem Skalierungwiderstand des <strong>Ein</strong>gangssignals<br />

Ê ½ ¾Å Å [4], erhält man die eingangsbezogene<br />

Rausch-Spannungsdichte:<br />

ÚÒØ ¾ ¾<br />

ʾ ½ ¡ ¾ ½¾ Î<br />

ÒØ ¾¿ (12)<br />

ÀÞ<br />

welche sich zu einem ½½ Rauschpegel übertragen<br />

läßt. Wenn man zusätzlich das Rauschen des p-Kanal-<br />

Transistors hizunimmt, ergibt sich ein weiterer Anstieg<br />

um ¿. In Abb. 4 ist diese überschlägige Abschätzung<br />

klar bestätigt.<br />

Abb. 5 zeigt den gemessenen Signal-Rausch-Abstand,<br />

gemessen bei Ë ¾À sowie den Signal-Rausch<br />

und Distortion-Abstand, gemessen bei Ë À, des<br />

<strong>Modulator</strong>s <strong>mit</strong> SCR-I Rückkopplung. Hierbei wurde das<br />

Inband-Rauschen abzüglich des dc-Signals ab ca. 100Hz<br />

bis zur Bandkante ¾ÀÞ aufsummiert. Wie oben<br />

gezeigt wird der dynamische Bereich durch das weisse<br />

Rauschen der Transistor-Stromquellen begrenzt, erreicht<br />

jedoch nichtsdestotrotz einen Wert von Ê ¼ <strong>mit</strong><br />

klaren 10 Bit Auflösung.<br />

Bezüglich der Empfindlichkeit gegenüber Takt-Jitter ist<br />

bekannt, dass die zeitliche Modulation dem Ausgangsspektrum<br />

eines zeitkontinuierlichen <strong>Modulator</strong>s über die<br />

Rückkopplungspfade weisses Rauschen hinzufügt [1].<br />

Durch die Implementierung des DAU <strong>mit</strong> abfallenden<br />

Flanken ist zu erwarten, dass dieses weisse Rauschen im<br />

Vergleich zu einem <strong>Modulator</strong> <strong>mit</strong> NRZ Rückkopplung<br />

abnimmt [6]. Dies wird in Abb. 6 gezeigt, wo das LDS des<br />

hier vorgestellten <strong>Modulator</strong>s <strong>mit</strong> SCR-I Rückkopplung<br />

unter dem <strong>Ein</strong>fluss von Ø ½¼±ÌË Takt-Jitter gezeigt<br />

ist. Zum Vergleich wurde zusätzlich ein <strong>Modulator</strong> <strong>mit</strong><br />

rechteckförmiger, NRZ-Rückkopplung vermessen [4].<br />

Hier wird deutlich, dass der Rauschpegel beim <strong>Modulator</strong><br />

<strong>mit</strong> SCR-I Rückkopplung um fast ¾¼ unter dem des<br />

’gewöhnlichen’ <strong>Modulator</strong>s liegt. Als zusätzliches Resultat<br />

dieser Messung konnten zum ersten Mal die in der<br />

Literatur erwähnten nicht-weissen Rauschschürzen um<br />

den Signalpeak nachgewiesen werden, die das so genannte<br />

akkumulierte VCO-Takt-Jitter verursacht [3][9].<br />

In Abb.7 ist das gemessene Inband Rauschen des hier vorgestellten<br />

<strong>Modulator</strong>s <strong>mit</strong> SCR-I Rückkopplung über dem<br />

¾¼<br />

½¼<br />

¼

ÄË ℄<br />

ÄË ℄<br />

¼<br />

¼<br />

½¾¼<br />

½¼ ½ ½¼ ¾ ÖÕÙÒÞ ÀÞ℄ ½¼ ½¼ <br />

(a) NRZ-<strong>Modulator</strong><br />

¼<br />

¼<br />

½¾¼<br />

½¼ ½ ½¼ ¾ ÖÕÙÒÞ ÀÞ℄ ½¼ ½¼ <br />

(b) SCR-I-<strong>Modulator</strong><br />

ÐÙÒ º ÄË Ò× ÆÊ ÙÒ ×× ËʹÁ ÅÓÙ¹<br />

ÐØÓÖ× ÙÒØÖ ÐÓ¹ÂØØÖ ÒÙ×׸ Ø ½¼±Ì Ë<br />

ÁÆ ℄<br />

<br />

¼<br />

<br />

¼<br />

<br />

¼<br />

ËÊ Á ÅÓÙÐØÓÖ<br />

ÆÊ ÅÓÙÐØÓÖ 7℄<br />

ÁÐ× ÁÆ <br />

ÔÔÖÓÜ ÂØØÖ ÁÆ<br />

<br />

¼¼½ ¼½ ½ ½¼<br />

Ø ± Ì Ë ℄<br />

ÐÙÒ º Ñ××Ò× ÁÆ ÙÒØÖ ÐÓ¹ÂØØÖ Ò¹<br />

Ù××<br />

Clock-Jitter des Systems aufgetragen und <strong>mit</strong> dem Verhalten<br />

eines NRZ-<strong>Modulator</strong>s [7] [4] verglichen. An dieser<br />

Stelle wird die Funktionalität des vorgestellten Konzepts<br />

besonders deutlich, da in dieser ersten Implementierung<br />

und trotz der groben Annäherung des Transistorverhaltens<br />

im Model in Gl. 3 eine deutliche Absenkung der Empfindlichkeit<br />

gegenüber Takt-Jitter erreicht werden konnte, die<br />

mehr als ½¼ für grosse Werte von Ø beträgt.<br />

In Tabelle 1 sind die Ergebnisse und Eigenschaften der<br />

implementierten Schaltung <strong>mit</strong> SCR-I Rückkopplung zusammengestellt<br />

und <strong>mit</strong> einer älteren Schaltung <strong>mit</strong> rechteckförmiger<br />

Rückkopplung verglichen[7, 4].<br />

5. Nicht-Idealitäten und<br />

Verbesserungsmöglichkeiten<br />

Neben den erreichten Ergebnissen sind zwei Ursachen<br />

nicht-idealen Verhaltens besonders zu benennen: Zum<br />

einen reduziert das weisse Transistor-Stromrauschen den<br />

dynamischen Bereich des <strong>Modulator</strong>s, was die Auflösung<br />

hinter die theoretisch möglichen Werte zurückfallen läßt.<br />

Jedoch ist dieses Verhalten stark von der jeweiligen Im-<br />

ÌÐÐ ½º Ù×ÑÑÒ××ÙÒ Ö Ò×ØÒ<br />

Ì ÒÓÐÓ<br />

Î<br />

ËÒÐ ÖÕ<br />

Ø×Ø ÖÕ<br />

Ä×ØÙÒ×ÚÖÖ<br />

ÆÊ<br />

ËÊ Á<br />

¼ Ñ ¿¿ Î ÅÇË<br />

½ Î<br />

¾ ÀÞ<br />

¾ ÅÀÞ<br />

¾¼ Ï<br />

ÝÒ Ö ½ <br />

ÑÜ ËÒ ÊÙ× ×Ø ¼ ¿<br />

ÅÜ Ì ÓÐÖÖÖ×Ø Ø ½±ÌË Ø ±ÌË<br />

ÁÆ ¼<br />

plementierung abhängig, und zwar betreffend der Architektur,<br />

der Abtastfrequenz und anderer Faktoren, was eine<br />

Vermeidung in zukünftigen Entwürfen leicht möglich<br />

macht.<br />

Die weitaus grössere Aufgabe, die noch näherer Aufmerksamkeit<br />

bedarf, ist die unzureichende Abschaltung der<br />

Stromquelle am Ende der abfallenden Flanke, was durch<br />

das nicht-zutreffende Model in Gl. 3 begründet ist und zu<br />

einem Reststromfluss im Moment der Abschaltung durch<br />

den verjitterten Takt führt. Dieser lag nur um einen Faktor<br />

3-4 unter dem Rückkopplungsstrom des ursprünglichen<br />

NRZ-<strong>Modulator</strong>s [4] und ist da<strong>mit</strong> der Grund für die<br />

nicht-ideale Clock-Jitter-Unterdrückung in Abb. 7, wenn<br />

man diese <strong>mit</strong> den idealen Ergebnissen in [6] vergleicht.<br />

<strong>Ein</strong>e mögliche Lösung wäre die Absenkung der unteren<br />

Referenz-Spannung Î ÐÓÛ der Steuerspannung, um die<br />

Stromquelle weiter in den Sperrbereich zu bringen. Andererseits<br />

führte dies sicherlich zu einem Auflösungverlust<br />

durch die folgende Abweichung vom idealen, exponentiellen<br />

Verlauf des Rückkopplungsstroms.<br />

Deshalb bedarf dieser Punkt weiterer theoretischer Betrachtung<br />

oder muss durch Simulation gelöst werden.<br />

6. Zusammenfassung<br />

In diesem Paper wird erstmalig ein <strong>zeitkontinuierlicher</strong><br />

¦¡ <strong>Modulator</strong> <strong>mit</strong> Stromrückkopplung und reduzierter<br />

Empfindlichkeit gegenüber Takt-Jitter vorgestellt. Dazu<br />

wird der Rückkopplungs-Digital/Analog Umsetzer durch<br />

Stromquellen implementiert, deren Steuerspannung als<br />

exponentiell abfallender Puls ausgebildet ist. Im Gegensatz<br />

zu vorangegangenen Techniken wird der Rückkopplungspuls<br />

hierdurch unabhängig vom Integratoreingangspotential<br />

und gleichzeitig wird ein zukünftiger Multi-Bit<br />

Entwurf ermöglicht.<br />

Die vorgeschlagene Schaltungstechnik wurde beispielhaft<br />

in einem verlustleistungsarmen, 1.5V <strong>Modulator</strong> ¿ Ö Ordnung<br />

implementiert. Sowohl die erfolgreiche Synthese als<br />

auch viel versprechende Messergebnisse konnten gezeigt<br />

werden. Trotz zweier dominanter, nicht-idealer Eigenschaften<br />

erreicht der gezeigte <strong>Modulator</strong> einen Dynamik-<br />

Bereich von ¼, wobei die Empfindlichkeit gegenüber<br />

Takt-Jitter um mehr als ½¼ reduziert werden konnte.

7. References<br />

[1] H. Tao, L. Toth, J.M. Khoury, “Analysis of timing jitter in<br />

bandpass sigma-delta modulators,” IEEE Trans. on Cir. and<br />

Sys. -II, 1999, vol. 46, pp. 991–1001.<br />

[2] E.J. van der Zwan, E. C. Dijkmans, “A 0.2-mW CMOS ¦¡<br />

modulator for speech coding with 80 dB dynamic range”,<br />

IEEE J. Solid-State Circuits, 1996, Vol.31, pp. 1873-1880.<br />

[3] J.A. Cherry, W.M. Snelgrove, “Continuous-time <strong>Delta</strong>-<br />

<strong>Sigma</strong> <strong>Modulator</strong>s for High-Speed A/D Conversion”, Kluwer<br />

Academic Pub., 1999.<br />

[4] F. Gerfers, M. Ortmanns, Y. Manoli, “A 12 bit power efficient<br />

continuous-time ¦¡ modulator with ¾¼Ï power<br />

consumption”, Proc. ESSCirC, 2001, pp. 536-539.<br />

[5] M. Ortmanns, X. Huang, and Y. Manoli, “Neue DAU-rückkopplung<br />

für zeitkontinuierliche ¦¡ <strong>Modulator</strong>en”, ITG-<br />

Fachbericht 162, Mikroelektronik für die Informationstechnik,<br />

pp. 221-226, 2000.<br />

[6] M. Ortmanns, F. Gerfers, and Y. Manoli, “Jitter insensitive<br />

Feedback DAC for Continuous-Time ¦¡ <strong>Modulator</strong>s”,<br />

Proc. ICECS, 2001, pp. 1049-1053.<br />

[7] M. Ortmanns, F. Gerfers, Y. Manoli, “A continuous-time<br />

¦¡ modulator with reduced jitter sensitivity”, Proc. ES-<br />

SCirC, 2002, pp. 287-290.<br />

[8] M. Ortmanns, F. Gerfers, Y. Manoli, “The implementation<br />

of a continuous-time sigma-delta modulator with reduced<br />

jitter sensitivity”, GMM/GI/ITG-Fachtagung - Entwurf Integrierter<br />

Schaltungen und Systeme, E.I.S.-Workshop, Erlangen,<br />

2003, accepted on.<br />

[9] A. Berkowitz, I. Rusnak, “FFT processing of randomly sampled<br />

harmonic signals”, IEEE Trans. Signal Processing,<br />

1992, vol. 40, pp. 2816-2819.