Versuchsaufbau und Durchführung 1. Bedienungsanleitung ...

Versuchsaufbau und Durchführung 1. Bedienungsanleitung ...

Versuchsaufbau und Durchführung 1. Bedienungsanleitung ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

nimmt einige Zeit in Anspruch. Manchmal ist mehr als einmaligen „probieren“ nötig bis dies erfolgreichwar. Sollte nach mehr als 2-3 Versuchen die Initialisierung wiederholt nicht erfolgreichsein trennen Sie ihr Board vom Strom, starten Sie die HWP Anwendung neu <strong>und</strong> verbinden Siedas Board erneut mit dem Strom <strong>und</strong> beginnen den Initialisierungsvorgang von vorn . MehrfachesInitialisieren schadet nicht.<strong>1.</strong>5. Testen einer SchaltungDer Aufbau der Schaltung (<strong>und</strong> alle späteren Änderungen) auf dem Breadboard DBB2 erfolgtgr<strong>und</strong>sätzlich im stromlosen Zustand des Breadboards (Schalter auf dem Pegelwandler AUS).Nach Abschluss des Aufbaus der Schaltung <strong>und</strong> sorgfältiger Sichtprüfung kann die Versorgungsspannungdes Breadboards eingeschaltet werden (Schalter auf dem Pegelwandler EIN).Für die Durchführung des Tests muss dem Steuerprogramm die Stimulusdatei bekannt gemachtwerden (hier: stim_<strong>1.</strong>txt).Klick auf Run startet den Test. Die Ausgabe ist so aufgebaut, wie Sie es aus der Simulationkennen.<strong>1.</strong>6. Beenden der ArbeitStromversorgung DBB2 AUS (Schalter auf dem Pegelwandler)AbmeldenDie weiteren Handgriffe wird in der Regel der für das Praktikum verantwortliche Assistent vornehmen.Stromversorgung D2E AUS (Steckernetzgerät gezogen)Stromversorgung Pegelwandler AUS (Steckernetzgerät gezogen)Rechner HerunterfahrenMonitorAUS2

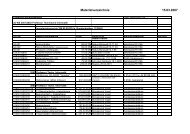

2.2. Hinweise zum Aufbau der UUT2.2.<strong>1.</strong> DBB1Für den Aufbau der UUT stehen zur Verfügung:32 Quellen PB 1 bis 3232 Senken PA 1 bis 3282 interne Leitungen ABCDE 1 bis 41FGHIJ 1 bis 4112 nicht belegte Anschlüsse PA 33 bis 36, 38 <strong>und</strong> 40 nicht beschalten!PB 33 bis 36, 38 <strong>und</strong> 40 nicht beschalten!2 Anschlüsse „0 V“ PA 39, PB 392 Anschlüsse „+ 5 V“ PA 37, PB 37 nicht beschalten!1 Leitung „0 V“ X1 Leitung „+ 5 V“ Y nicht beschalten!2.2.2. DBB2Für den Aufbau der UUT stehen zur Verfügung:16 Quellen X_FGHIJ 5 bis 2016 Senken Z_ABCDE 5 bis 20336 interne Leitungen X_FGHIJ 21 bis 63X_ABCDE 1 bis 63Y_FGHIJ 1 bis 63Y_ABCDE 1 bis 63Z_FGHIJ 1 bis 63Z_ABCDE 21 bis 634 nicht belegte Anschlüsse X_FGHIJ 3 <strong>und</strong> 4 nicht beschalten!Z_ABCDE 3 <strong>und</strong> 4 nicht beschalten!1 Leitung „0 V“ X_FGHIJ 1, Z_ABCDE 1<strong>und</strong> alle blauen Leitungen1 Leitung „+ 5 V“ X_FGHIJ 2, Z_ABCDE 2 nicht beschalten!<strong>und</strong> alle roten LeitungenIm Hardwarepraktikum kommt aus heutiger Sicht ausschließlich das Breadboard DBB2 zum Einsatz.Außerdem werden nur maximal 8 Quellen <strong>und</strong> maximal 8 Senken benötigt. Genutzt werdendie Quellen X_FGHIJ 13, 14, 15, 16, 17, 18, 19 <strong>und</strong> 20 sowie die Senken Z_ABCDE 13, 14, 15,16, 17, 18, 19 <strong>und</strong> 20. Die weiteren Ausführungen beziehen sich auf diese eingeschränkte Nutzung.Falls eine umfassendere Nutzung in Frage kommt, wird das in der betreffenden Versuchsanleitungbesprochen.2.2.3. BOOLEsche KonstantenGelegentlich werden BOOLEsche Konstanten ’0’ oder ’1’ benötigt. Abbildung 3 fasst die Möglichkeitenzusammen. Die Konstante ’1’ darf nicht aus der Versorgungsspannung bezogen werden!Der direkte´Anschluss eines TTL-Eingangs an die Versorgungsspannung kann zur Zerstörung desSchaltkreises führen.Konstante ’0’Konstante ’1’aus der Stimulusfolge: Eine der Quellen wird konstant auf ’0’ gelegt (s. u.)Anschlüsse <strong>und</strong> Leitungen „0 V“ der Breadboardsaus der Stimulusfolge: Eine der Quellen wird konstant auf ’1’ gelegt (s. u.)vom Ausgang eines Negators, dessen Eingang konstant auf ’0’ gelegt istein offener (d. h. nichtbeschalteter) Eingang wird bei TTL wie ’1’ gelesen, nur für kombinato6

2.2.4. TTLEs gelten die üblichen TTL-Spielregeln:• Ausgänge dürfen nicht direkt mit „0 V“ oder „+ 5 V“ verb<strong>und</strong>en werden!• Im Hardwarepraktikum kommen ausschließlich Schaltkreise mit sog. Totem-Pole-Ausgängenzum Einsatz. Das Zusammenschalten mehrerer Totem-Pole-Ausgänge ist verboten!• Die Lastverhältnisse sind zu beachten!Anm.: Da im Hardwarepraktikum verschiedene TTL-Familien gemischt verwendet werden,soll hier keine allgemein gültige Regel angegeben werden. Die Testschaltungen des Hardwarepraktikumssind so beschaffen, dass keine Probleme zu erwarten sind. Andernfalls wirdin den Versuchsanleitungen darauf hingewiesen.2.3. StimulusfolgenEine Stimulusfolge ist eine ASCII-Datei aus einer beliebigen Anzahl gleichartig aufgebauter Zeilen.Jede Zeile entspricht einem Stimulus.Pos. Länge Inhalt Bedeutung1 7 ’stimmap’ Schlüssel für Stimulus8 1 ’SP’ Leerzeichen als Trennzeichen9 2 ’dbb2_08’ Auswahl des Breadboards DBB2 <strong>und</strong> Auswahl von 8 Quellen <strong>und</strong> 8 Senken16 1 ’SP’ Leerzeichen als Trennzeichen17 8 xxxxxxxx Eingangspegel der UUT (Quellen)Position 17 18 19 20 21 22 23 24Kanal X_FGHIJ 20 19 18 17 16 15 14 13x Bedeutung0 Pegel 01 Pegel 1- nicht belegtX Pegel X (nur für Simulation!)25 1 ’|’ Trennzeichen26 8 yyyyyyyy Sollausgangspegel der UUT (Senken)Position 26 27 28 29 30 31 32 33Kanal Z_ABCDE 20 19 18 17 16 15 14 13y Bedeutung0 Sollpegel 01 Sollpegel 1- Sollpegel nicht bestimmtX Sollpegel X (nur für Simulation!)34 1 SP Leerzeichen als Trennzeichen35 40 kkkkk... Kommentar (optional)stimmap dbb2_08 xxxxxxxx|yyyyyyyy kkkkkkkkkkkkkkkkkkkk...Stimulus, Kurzdarstellung7

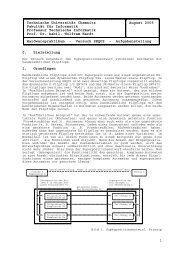

Zur Verdeutlichung soll ein Beispiel dienen. Ein Adder sei mit seinen Eingängen an die KanäleX_FGHIJ 20 (Operand a), X_FGHIJ 19 (Operand b) <strong>und</strong> X_FGHIJ 18 (einlaufender Übertragc) <strong>und</strong> seinen Ausgängen an die Kanäle Z_ABCDE 20 (auslaufender Übertrag cc) <strong>und</strong>Z_ABCED 19 (Summe s) angeschlossen.X_FGHIJ 20X_FGHIJ 19X_FGHIJ 18abcADDsccZ_ABCDE 19Z_ABCDE 20Abbildung 5: Beispiel Adder, UUTEine vollständige binäre Stimulusfolge könnte so aussehen:stimmap dbb2_08 000− − − − − 00− − − − −− 0+0+0=0stimmap dbb2_08 001− − − − − 01− − − − −− 0+0+1=1stimmap dbb2_08 010− − − − − 01− − − − −− 0+1+0=1stimmap dbb2_08 011− − − − − 10− − − − −− 0+1+1=2stimmap dbb2_08 100− − − − − 01− − − − −− 1+0+0=1stimmap dbb2_08 101− − − − − 10− − − − −− 1+0+1=2stimmap dbb2_08 110− − − − − 10− − − − −− 1+1+0=2stimmap dbb2_08 111− − − − − 11− − − − −− 1+1+1=3Diese binäre Stimulusfolge ist sowohl für die Simulation (s. u.) als auch für die Verwendung inder Testeinrichtung geeignet.Die ternäre Simulation nach EICHELBERGER (s. „Konstruktion hasardresistenter Stimulusfolgen“)ist hier nicht angebracht. Übungshalber soll aber gezeigt werden, wie die aus eben gezeigterStimulusfolge abgeleitete ternäre Stimulusfolge aussähe:stimmap dbb2_08 0 0 0 − − − − − 0 0 − − − − −− 0 + 0 + 0 = 0stimmap dbb2_08 0 0 X − − − − − − − − − − − −− 0 + 0 + 0|1 = 0|1stimmap dbb2_08 0 0 1 − − − − − 0 1 − − − − −− 0 + 0 + 1 = 1stimmap dbb2_08 0 X X − − − − − − − − − − − −− 0 + 0|1 + 0|1 = 0|1|2stimmap dbb2_08 0 1 0 − − − − − 0 1 − − − − −− 0 + 1 + 0 = 1stimmap dbb2_08 0 1 X − − − − − − − − − − − −− 0 + 1 + 0|1 = 1|2stimmap dbb2_08 0 1 1 − − − − − 1 0 − − − − −− 0 + 1 + 1 = 2stimmap dbb2_08 X X X − − − − − − − − − − − −− 0|1 + 0|1 + 0|1 = 0|1|2|3stimmap dbb2_08 1 0 0 − − − − − 0 1 − − − − −− 1 + 0 + 0 = 1stimmap dbb2_08 1 0 X − − − − − − − − − − − −− 1 + 0 + 0|1 = 1|2stimmap dbb2_08 1 0 1 − − − − − 1 0 − − − − −− 1 + 0 + 1 = 2stimmap dbb2_08 1 X X − − − − − − − − − − − −− 1 + 0|1 + 0|1 = 1|2|3stimmap dbb2_08 1 1 0 − − − − − 1 0 − − − − −− 1 + 1 + 0 = 2stimmap dbb2_08 1 1 X − − − − − − − − − − − −− 1 + 1 + 0|1 = 2|3stimmap dbb2_08 1 1 1 − − − − − 1 1 − − − − −− 1 + 1 + 1 = 3Diese Stimulusfolge ist nur für die Simulation geeignet.8

2.4. SimulationUm sich in Vorbereitung auf die Versuche des Hardwarepraktikums von der Korrektheit desEntwurfs eines binären Systems <strong>und</strong> der Korrektheit der dafür konstruierten Stimulusfolge(n)überzeugen zu können, stellen wir eine VHDL-Testbench zur Verfügung. Die Testbench verhältsich exakt so wie die Testeinrichtung, die Sie im Hardwarepraktikum vorfinden. Außerdem „versteht“die Testbench die ternäre Algebra T = {0,1,X}. Somit besteht die Möglichkeit, mit ein <strong>und</strong>derselben Testbench <strong>und</strong> ternären VHDL-Modellen der zu entwerfenden binären Systeme, binäre<strong>und</strong> ternäre Stimulusfolgen zu verarbeiten (s. „Konstruktion hasardresistenter Stimulusfolgen“).Für das Verständnis der nachfolgend abgedruckten Quelltexte sind nur einige wenige Erläuterungennötig.In Teil 1 werden der Datentyp x01_vector <strong>und</strong> zwei Konvertierungsfunktionen vereinbart. DerDatentyp x01_vector ist aus „Konstruktion hasardresistenter Stimulusfolgen“ bekannt. Die Konvertierungmacht sich erforderlich, da die Stimulusdateien den Datentyp string verwenden, dieSimulation jedoch den Datentyp x01_vector.1 library i e e e ;2 use i e e e . std_logic_1164 . a l l ;34 package pack_2 i s5 type x01_vector i s array ( n a t u r a l range ) of x01 ;6 function to_x01 ( x : in s t r i n g ) return x01_vector ;7 function to_char ( x : in x01_vector ) return s t r i n g ;8 end pack_2 ;910 package body pack_2 i s11 function to_x01 ( x : in s t r i n g ) return x01_vector i s12 a l i a s temp1 : s t r i n g (1 to x ’ l e n g t h ) i s x ;13 variable temp2 : x01_vector (1 to x ’ l e n g t h ) ;14 begin15 for i in temp1’range loop16 case temp1 ( i ) i s17 when ’ 0 ’ => temp2 ( i ) := ’ 0 ’ ;18 when ’ 1 ’ => temp2 ( i ) := ’ 1 ’ ;19 when others => temp2 ( i ) := ’ X ’ ;20 end case ;21 end loop ;22 return temp2 ;23 end to_x01 ;2425 function to_char ( x : in x01_vector ) return s t r i n g i s26 a l i a s temp1 : x01_vector (1 to x ’ l e n g t h ) i s x ;27 variable temp2 : s t r i n g (1 to x ’ l e n g t h ) ;28 begin29 for i in temp1’range loop30 case temp1 ( i ) i s31 when ’ 0 ’ => temp2 ( i ) := ’ 0 ’ ;32 when ’ 1 ’ => temp2 ( i ) := ’ 1 ’ ;33 when ’ X ’ => temp2 ( i ) := ’ X ’ ;34 end case ;35 end loop ;36 return temp2 ;37 end to_char ;38 end pack_2 ;9

In Teil 2 wird die Testeinrichtung ohne die UUT beschrieben. Die Stimulusdatei wird eingelesen.Nach dem Einlesen eines Stimulus wird dieser auf die Kanäle x_fghij(20 downto 13) derTesteinrichtung gelegt. Anschließend wird 100 ns gewartet bis die Ausgangssignale der UUT aufden Kanälen z_abcde(20 downto 13) stabil sind <strong>und</strong> eingelesen <strong>und</strong> mit den Sollpegeln aus demStimulus verglichen werden können. Abweichungen werden markiert.1 library i e e e ; use i e e e . std_logic_1164 . a l l ;2 use work . pack_2 . a l l ; use std . t e x t i o . a l l ;34 entity dbb2_08 i s5 port ( x_fghij : out x01_vector (20 downto 1 3 ) ;6 z_abcde : in x01_vector (20 downto 1 3 ) ) ;7 end dbb2_08 ;89 architecture behavior of dbb2_08 i s10 f i l e f_in : t e x t i s in " f_in " ;11 f i l e f_out : t e x t i s out " f_out " ;12 signal e o f : boolean := f a l s e ;13 signal c l o c k : x01 := ’ 0 ’ ;14 signal number : i n t e g e r ;15 signal stim_x01 : x01_vector (8 downto 1 ) ;16 signal stim_char , s o l l _ c h a r : s t r i n g (1 to 8 ) ;17 signal comment : s t r i n g (1 to 4 0 ) ;18 begin19 process ( c l o c k ) begin20 i f not e o f or c l o c k = ’ 1 ’ then21 c l o c k

55 w r i t e ( z e i l e , " "&stim_char&" −> "&ist_char&" "&comment ) ;56 w r i t e l i n e ( f_out , z e i l e ) ;57 w r i t e ( z e i l e , soll_char , r i g h t , 2 4 ) ;58 w r i t e l i n e ( f_out , z e i l e ) ;59 mark := ( others => ’ ’ ) ;60 for i in mark’range loop61 i f s o l l _ c h a r ( i ) /= ’ −’ then62 i f ist_char ( i ) /= s o l l _ c h a r ( i ) then63 mark ( i ) := ’ ^ ’ ;64 end i f ;65 end i f ;66 end loop ;67 w r i t e ( z e i l e , mark , r i g h t , 2 4 ) ;68 w r i t e l i n e ( f_out , z e i l e ) ;69 end process ;70 end behavior ;In Teil 3 wird die UUT beschrieben. Es ist zunächst nur erforderlich, die Entity-Deklarationanzugeben, die unabhängig von der konkreten UUT ist <strong>und</strong> für die Beschreibung der Kopplungzwischen der Testeinrichtung <strong>und</strong> der UUT gebraucht wird.1 library i e e e ;2 use i e e e . std_logic_1164 . a l l ;3 use work . pack_2 . a l l ;45 entity uut i s6 port ( x_fghij : in x01_vector (20 downto 1 3 ) ;7 z_abcde : out x01_vector (20 downto 1 3 ) ) ;8 end uut ;In Teil 4 wird schließlich die Kopplung zwischen Testeinrichtung <strong>und</strong> UUT beschrieben. Die so beschriebeneTestbench bleibt unabhängig von der konkreten UUT. Die Architektur-Beschreibungder UUT kann später hinzugefügt <strong>und</strong> nach der Kompilation der Testbench kompiliert werden.Diese Vorgehensweise ist eine Folge des bei VHDL realisierten ßpäten Bindens", was u. a. für diearbeitsteilige Entwicklung großer Systeme von Bedeutung ist.1 library i e e e ;2 use i e e e . std_logic_1164 . a l l ;3 use work . pack_2 . a l l ;45 entity t e s t i s6 end t e s t ;78 architecture t e s t of t e s t i s9 component dbb2_0810 port ( x_fghij : out x01_vector (20 downto 1 3 ) ;11 z_abcde : in x01_vector (20 downto 1 3 ) ) ;12 end component ;13 component uut14 port ( x_fghij : in x01_vector (20 downto 1 3 ) ;15 z_abcde : out x01_vector (20 downto 1 3 ) ) ;16 end component ;17 signal x_fghij , z_abcde : x01_vector (20 downto 13) := ( others => ’ 0 ’ ) ;18 begin19 u1 : dbb2_08 port map( x_fghij , z_abcde ) ;20 u2 : uut port map( x_fghij , z_abcde ) ;21 end t e s t ;Die Teile 1 bis 4 er Testbench sind unabhängig von der konkreten UUT <strong>und</strong> sollten in der angegebenenReihenfolge in einer Datei zusammen abgespeichert werden, die nur einmal kompiliertwerden muss. Die konkrete UUT sollte in einer zweiten Datei abgelegt werden, die anschließend11

(<strong>und</strong> bei jeder Änderung der UUT erneut) zu kompilieren ist.Für die UUT geben wir hier eine Datenflussbeschreibung an. Die nochmalige Angabe der ENTITY-Deklaration ist eigentlich überflüssig. Sie erlaubt aber die getrennte Behandlung (insbesonderedie Kompilation) der Datei, in der die UUT abgelegt ist, <strong>und</strong> ist deshalb außerordentlich sinnvoll!Im Praktikum selbst kommen Strukturbeschreibungen mit Gattern aus einer ternären Gatterbibliothekzum Einsatz. Diese Vorgehensweise ist an anderer Stelle in einem ausführlichen Beispielerläutert.1 library i e e e ;2 use i e e e . std_logic_1164 . a l l ;3 use work . pack_2 . a l l ;45 entity uut i s6 port ( x_fghij : in x01_vector (20 downto 1 3 ) ;7 z_abcde : out x01_vector (20 downto 1 3 ) ) ;8 end uut ;910 architecture dataflow of uut i s11 a l i a s a : x01 i s x_fghij ( 2 0 ) ;12 a l i a s b : x01 i s x_fghij ( 1 9 ) ;13 a l i a s c : x01 i s x_fghij ( 1 8 ) ;14 a l i a s cc : x01 i s z_abcde ( 2 0 ) ;15 a l i a s s : x01 i s z_abcde ( 1 9 ) ;16 begin17 cc

<strong>1.</strong> 0 0 0 − − − − − −→ 0 0 0 0 0 0 0 0 0 + 0 + 0 = 00 0 − − − − −−2. 0 0 X − − − − − −→ 0 X 0 0 0 0 0 0 0 + 0 + 0|1 = 0|1− − − − − − −−3. 0 0 1 − − − − − −→ 0 1 0 0 0 0 0 0 0 + 0 + 1 = 10 1 − − − − −−4. 0 X X − − − − − −→ X X 0 0 0 0 0 0 0 + 0|1 + 0|1 = 0|1|2− − − − − − −−5. 0 1 0 − − − − − −→ 0 1 0 0 0 0 0 0 0 + 1 + 0 = 10 1 − − − − −−6. 0 1 X − − − − − −→ X X 0 0 0 0 0 0 0 + 1 + 0|1 = 1|2− − − − − − −−7. 0 1 1 − − − − − −→ 1 0 0 0 0 0 0 0 0 + 1 + 1 = 21 0 − − − − −−8. X X X − − − − − −→ X X 0 0 0 0 0 0 0|1 + 0|1 + 0|1 = 0|1|2|3− − − − − − −−9. 1 0 0 − − − − − −→ 0 1 0 0 0 0 0 0 1 + 0 + 0 = 10 1 − − − − −−10. 1 0 X − − − − − −→ X X 0 0 0 0 0 0 1 + 0 + 0|1 = 1|2− − − − − − −−1<strong>1.</strong> 1 0 1 − − − − − −→ 1 0 0 0 0 0 0 0 1 + 0 + 1 = 21 0 − − − − −−12. 1 X X − − − − − −→ X X 0 0 0 0 0 0 1 + 0|1 + 0|1 = 1|2|3− − − − − − −−13. 1 1 0 − − − − − −→ 1 0 0 0 0 0 0 0 1 + 1 + 0 = 21 0 − − − − −−14. 1 1 X − − − − − −→ 1 X 0 0 0 0 0 0 1 + 1 + 0|1 = 2|3− − − − − − −−15. 1 1 1 − − − − − −→ 1 1 0 0 0 0 0 0 1 + 1 + 1 = 31 1 − − − − −−Ausgabe bei ternärer Simulation (Antwort auf die ternäre Stimulusfolge)In der Ausgabe der ternären Simulation wird das Prinzip der Simulation nach Eichelbergerdeutlich. Die eingefügten Stimuli weisen einen oder mehrere Eingangspegel ’X’ auf. Das ternäreModell der UUT kann darauf mit der Ausgabe von Pegeln ’X’ reagieren. Das ist dann <strong>und</strong>nur dann bedeutungslos, wenn in den Stimuli, die unverändert aus der binären Stimulusfolgeübernommen worden sind, keine Ausgangspegel ’X’ auftreten. Deshalb gibt man für die eingefügtenStimuli keine Sollausgangspegel vor <strong>und</strong> bezieht damit die eingefügten Stimuli nicht inden Soll-/Ist-Vergleich ein. Der Soll-/Ist-Vergleich wird nur für die unverändert aus der binärenStimulusfolge übernommenen Stimuli durchgeführt. Wenn dabei kein Pegel ’X’ auftritt, ist diebinäre Stimulusfolge hasardresistent, d. h. sie „läuft“ problemlos auf der Testeinrichtung <strong>und</strong>liefert reproduzierbare Testergebnisse.14