3 Arbeitsspeicher- und Bussysteme

3 Arbeitsspeicher- und Bussysteme

3 Arbeitsspeicher- und Bussysteme

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

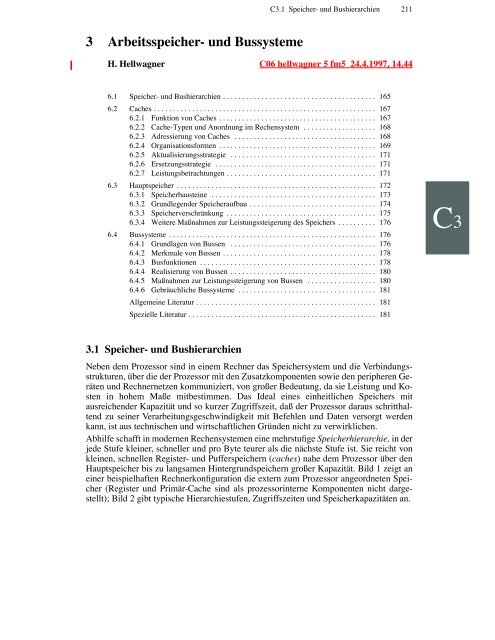

3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

C<br />

C3.1 Speicher- <strong>und</strong> Bushierarchien 211<br />

H. Hellwagner C06 hellwagner 5 fm5 24.4.1997, 14.44<br />

6.1 Speicher- <strong>und</strong> Bushierarchien . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165<br />

6.2 Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167<br />

6.2.1 Funktion von Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167<br />

6.2.2 Cache-Typen <strong>und</strong> Anordnung im Rechensystem . . . . . . . . . . . . . . . . . . . 168<br />

6.2.3 Adressierung von Caches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168<br />

6.2.4 Organisationsformen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169<br />

6.2.5 Aktualisierungsstrategie . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171<br />

6.2.6 Ersetzungsstrategie . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171<br />

6.2.7 Leistungsbetrachtungen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171<br />

6.3 Hauptspeicher . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172<br />

6.3.1 Speicherbausteine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173<br />

6.3.2 Gr<strong>und</strong>legender Speicheraufbau . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174<br />

6.3.3 Speicherverschränkung . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175<br />

6.3.4 Weitere Maßnahmen zur Leistungssteigerung des Speichers . . . . . . . . . . 176<br />

6.4 <strong>Bussysteme</strong> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176<br />

6.4.1 Gr<strong>und</strong>lagen von Bussen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176<br />

6.4.2 Merkmale von Bussen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178<br />

6.4.3 Busfunktionen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178<br />

6.4.4 Realisierung von Bussen . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180<br />

6.4.5 Maßnahmen zur Leistungssteigerung von Bussen . . . . . . . . . . . . . . . . . . 180<br />

6.4.6 Gebräuchliche <strong>Bussysteme</strong> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181<br />

Allgemeine Literatur . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181<br />

Spezielle Literatur . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181<br />

3.1 Speicher- <strong>und</strong> Bushierarchien<br />

Neben dem Prozessor sind in einem Rechner das Speichersystem <strong>und</strong> die Verbindungsstrukturen,<br />

über die der Prozessor mit den Zusatzkomponenten sowie den peripheren Geräten<br />

<strong>und</strong> Rechnernetzen kommuniziert, von großer Bedeutung, da sie Leistung <strong>und</strong> Kosten<br />

in hohem Maße mitbestimmen. Das Ideal eines einheitlichen Speichers mit<br />

ausreichender Kapazität <strong>und</strong> so kurzer Zugriffszeit, daß der Prozessor daraus schritthaltend<br />

zu seiner Verarbeitungsgeschwindigkeit mit Befehlen <strong>und</strong> Daten versorgt werden<br />

kann, ist aus technischen <strong>und</strong> wirtschaftlichen Gründen nicht zu verwirklichen.<br />

Abhilfe schafft in modernen Rechensystemen eine mehrstufige Speicherhierarchie, in der<br />

jede Stufe kleiner, schneller <strong>und</strong> pro Byte teurer als die nächste Stufe ist. Sie reicht von<br />

kleinen, schnellen Register- <strong>und</strong> Pufferspeichern (caches) nahe dem Prozessor über den<br />

Hauptspeicher bis zu langsamen Hintergr<strong>und</strong>speichern großer Kapazität. Bild 1 zeigt an<br />

einer beispielhaften Rechnerkonfiguration die extern zum Prozessor angeordneten Speicher<br />

(Register <strong>und</strong> Primär-Cache sind als prozessorinterne Komponenten nicht dargestellt);<br />

Bild 2 gibt typische Hierarchiestufen, Zugriffszeiten <strong>und</strong> Speicherkapazitäten an.<br />

C3

212 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

Prozessor<br />

Sek<strong>und</strong>är-<br />

Cache<br />

Bussteuerung<br />

Hauptspeicher<br />

Prozessor-/<br />

Speicherbus<br />

E/A-<br />

Steuerung<br />

Busbrücke<br />

Bild 1 Beispiel für Speicher- <strong>und</strong> Bushierarchien in einem Rechensystem<br />

Jeder Speicher der Hierarchie enthält stets einen aktuellen Ausschnitt des größeren Speichers<br />

der nächsten Stufe (Inklusionseigenschaft). Die Einlagerung von Daten in prozessornahe<br />

Speicher wird durch die Zugriffe des Prozessors veranlaßt <strong>und</strong> durch Hardware<br />

(von Hauptspeicher in Caches <strong>und</strong> Register) oder Software (von Hintergr<strong>und</strong>- in Hauptspeicher)<br />

durchgeführt. Durch die bekannte Programmeigenschaft der räumlichen <strong>und</strong><br />

zeitlichen Lokalität von Referenzen auf Befehle <strong>und</strong> Daten [Denning 68] erfolgt der<br />

weitaus überwiegende Teil der Speicherzugriffe des Prozessors auf die schnelleren Speicher.<br />

Für den Prozessor entsteht dadurch der Eindruck, das Speichersystem habe eine<br />

mittlere Zugriffszeit im Bereich der Cache-Zugriffszeiten, verfüge jedoch über eine wesentlich<br />

höhere Kapazität.<br />

Ebenfalls aus Leistungs- <strong>und</strong> Kostenüberlegungen werden hierarchische <strong>Bussysteme</strong> eingesetzt.<br />

Ein Bus ist ein gemeinsamer Datenweg (mit zugehöriger Steuerlogik), an den<br />

mehrere Funktionseinheiten angeschlossen sein können, den aber zu jedem Zeitpunkt nur<br />

eine Einheit zur Übermittlung von Adressen, Daten oder Anweisungen nutzen kann. Ein<br />

Bus ist eine kostengünstige <strong>und</strong> daher die gebräuchlichste Verbindungsstruktur in konventionellen<br />

Rechensystemen, stellt aber durch die gemeinsame Nutzung bei vielen Teilnehmern<br />

einen möglichen Engpaß dar.<br />

Speicher<br />

Zugriffszeit<br />

(bei Prozessortakt von 5 ns)<br />

Speicherkapazität<br />

Prozessorregister < 5 ns 256 - 1024 Bytes<br />

Primär-Cache (prozessorintern) 5 - 20 ns 1 - 128 KBytes<br />

Sek<strong>und</strong>är-Cache (prozessorextern) 10 - 100 ns 256 kB - 4 MBytes<br />

Hauptspeicher 50 - 500 ns bis 1 GByte<br />

Hintergr<strong>und</strong>speicher (Magnetplatten) 5 - 15 ms bis 100 GBytes<br />

Archivspeicher (Magnetbänder, opt. Platten) >> 50 ms bis mehrere TBytes<br />

Bild 2 Speicherhierarchie mit typischen Eigenschaften<br />

Langsame periphere Geräte<br />

(z.B. Magnetbänder)<br />

Peripheriebus<br />

Systembus<br />

E/A-<br />

Schnittstelle<br />

Schnelle Peripherie<br />

(z.B. Magnetplatten)<br />

<strong>und</strong> Netzwerke<br />

Wie im Beispiel von Bild 1 gezeigt, werden daher auf den verschiedenen Ebenen eines<br />

Rechners verschiedene Busse verwendet, mit spezifisch für den Einsatzbereich zuge-

C3.2 Caches 213<br />

schnittenen Eigenschaften. Typische Hierarchiestufen, geordnet nach abnehmenden Datenübertragungsraten<br />

<strong>und</strong> Kosten der Busse, sind:<br />

• Prozessorinterne Busse zur Verbindung von Leit- <strong>und</strong> Rechenwerken, Registern,<br />

Primär-Caches <strong>und</strong> Schnittstelle zum externen Bus auf dem Prozessorbaustein.<br />

• Prozessorbus zur engen Kopplung des Sek<strong>und</strong>är-Caches <strong>und</strong> gegebenenfalls von Koprozessoren<br />

an den Hauptprozessor.<br />

• Prozessor-/Speicherbus für die schnelle Datenübertragung zwischen Prozessor(en)<br />

<strong>und</strong> Speicher. Dieser wird auch als lokaler Bus bezeichnet.<br />

• Systembus zum Anschluß von peripheren Geräten mit hoher Datenrate (z. B. Grafikeinheiten)<br />

<strong>und</strong> von Peripheriebussen, für den Zugang zu schnellen Rechnernetzen oder<br />

für die Kopplung mehrerer Prozessoren. Eine Variante sind sog. Rückwandbusse<br />

(backplane busses), die häufig genormt <strong>und</strong> so ausgeführt sind, daß ein System in modularer<br />

Weise aus Komponenten verschiedener Hersteller aufgebaut werden kann.<br />

• Peripherie- oder E/A-Bus, der weitere periphere Geräte zusammenfaßt <strong>und</strong> sie mit dem<br />

Systembus verbindet.<br />

• Zusatzbusse wie ein Interrupt- oder ein Nachrichtenbus, über die zwischen mehreren<br />

eigenständigen Prozessoren Unterbrechungen oder Nachrichten vermittelt werden.<br />

Diese Hierarchie <strong>und</strong> Terminologie sind in der Literatur <strong>und</strong> in Produkten nicht einheitlich.<br />

In Arbeitsplatzrechnern <strong>und</strong> Personal-Computern sind aus Kostengründen meist nur<br />

ein Prozessor-/Speicherbus <strong>und</strong> ein Peripheriebus zu finden. Funktionen von Systembussen<br />

werden zunehmend zum Prozessor-/Speicherbus verlagert, so daß schnelle Peripherie<br />

enger an Prozessor <strong>und</strong> Hauptspeicher gekoppelt ist.<br />

3.2 Caches<br />

3.2.1 Funktion von Caches<br />

Ein Cache ist ein schneller Pufferspeicher (wörtlich: Depot, Versteck) zwischen Prozessorregistern<br />

<strong>und</strong> Hauptspeicher. Darin sind die Programmteile <strong>und</strong> Daten, die während<br />

einer Programmausführung aktuell sind, als Kopien abgelegt <strong>und</strong> für den Prozessor<br />

schnell zugänglich. Bei jedem Zugriff des Prozessors auf ein Speicherwort überprüft die<br />

Steuerlogik des Caches an Hand der anliegenden Adresse, ob das Wort im Cache vorliegt<br />

oder nicht. Im Falle eines Treffers (hit) wird das Wort unmittelbar aus dem Cache in den<br />

Prozessor geladen bzw. im Cache verändert, möglichst mit der Zykluszeit des Prozessors.<br />

Bei einem Fehlzugriff (miss) wird aus dem Hauptspeicher ein Block von Worten in den<br />

Cache übertragen <strong>und</strong> daraus das angeforderte Wort dem Prozessor zur Verfügung gestellt<br />

bzw. darin modifiziert. Hauptspeicher <strong>und</strong> Cache sind also in Blöcken organisiert; man<br />

spricht von Cache-Blöcken oder Cache-Zeilen (cache blocks oder cache lines).<br />

Wegen der hohen Geschwindigkeitsanforderungen werden Caches durch Hardware verwaltet.<br />

Programmierer, Übersetzer <strong>und</strong> Betriebssystem haben Caches vorwiegend unter<br />

dem Gesichtspunkt ihrer effizienten Nutzung <strong>und</strong> der dadurch erreichbaren Leistungssteigerung<br />

zu beachten. Das heißt, Programme sind im Hauptspeicher so abzulegen <strong>und</strong> im<br />

Mehrprozeßbetrieb so auszuführen, daß möglichst viele ihrer Code- <strong>und</strong> Datenanteile mit<br />

Blockzugriffen vorausgreifend in den Cache geladen (read ahead) <strong>und</strong> darin möglichst<br />

lange gehalten <strong>und</strong> wiederverwendet werden können (reuse). Für Situationen, in denen<br />

Caching die Korrektheit der Programmausführung gefährdet, stehen der Software spezi-<br />

C3

214 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

elle Befehle zur Kontrolle der Cache-Inhalte zur Verfügung (siehe z. B. 3.2.3 Adressierung<br />

von Caches)<br />

3.2.2 Cache-Typen <strong>und</strong> Anordnung im Rechensystem<br />

Primär-Caches (first-level caches) sind heute Bestandteil aller modernen Mikroprozessorbausteine<br />

<strong>und</strong> meist getrennt als zwei Caches zur Speicherung von Befehlen <strong>und</strong> von<br />

Daten ausgeführt (split cache). Primär-Caches sind auf dem Prozessor-Chip integriert. Sie<br />

sind deshalb schnell, aber auch teuer <strong>und</strong> in ihrer Kapazität auf einige Dutzend KBytes<br />

beschränkt (siehe z. B. Bild 2). Cache-Zeilen sind im allgemeinen nicht länger als 32<br />

Bytes <strong>und</strong> damit in wenigen Zyklen nachladbar.<br />

Sek<strong>und</strong>är-Caches (second-level caches) werden gegenwärtig überwiegend außerhalb des<br />

Prozessors mit SRAM-Bausteinen realisiert (siehe Unterabschnitt 3.3.1). Dadurch unterliegen<br />

sie keinen engen Kapazitätsbeschränkungen <strong>und</strong> können einige MBytes groß gebaut<br />

werden. Bedingt durch die SRAM-Geschwindigkeiten dauert ein Zugriff aber einige<br />

bis einige Dutzend Takte (Bild 2). In Sek<strong>und</strong>är-Caches werden Befehle <strong>und</strong> Daten meist<br />

gemeinsam gespeichert (unified cache) <strong>und</strong> längere Blöcke als bei Primär-Caches verwendet,<br />

bis zu 128 Bytes. Dies dient dem Zweck, bei den unumgänglichen, langsamen<br />

Hauptspeicherzugriffen viele Worte schon vorausgreifend in den Cache einzulagern.<br />

Viele heute gängige Mikroprozessoren haben bereits die Steuerlogik für den Sek<strong>und</strong>är-<br />

Cache mit auf dem Chip integriert. Nun gehen erste Hersteller dazu über, den Sek<strong>und</strong>är-<br />

Cache selbst auf dem Prozessorbaustein zu realisieren (Beispiel: DEC Alpha 21164, 96<br />

KBytes) bzw. mittels spezieller Aufbautechnik sehr eng an diesen zu koppeln (Beispiel:<br />

Intel Pentium Pro, bis zu 512 KBytes im gleichen Gehäuse). In diesen Fällen, aber auch<br />

sonst bei kleinen Caches zweiter Stufe, ist es für den Aufbau von Hochleistungssystemen<br />

sinnvoll, einen Tertiär-Cache (third-level cache) vorzusehen.<br />

3.2.3 Adressierung von Caches<br />

Caches werden danach unterschieden, ob der Prozessor darauf mit virtuellen oder realen<br />

(physischen) Adressen zugreift (Verweise auf Bode <strong>und</strong> Borrmann).<br />

Ein großer Vorteil von sog. virtuellen Caches besteht darin, daß sie schneller sind: Cache-<br />

Zugriff <strong>und</strong> Adreßübersetzung durch die Speicherverwaltungseinheit (MMU; Verweis auf<br />

Bode) können nebenläufig stattfinden. Virtuelle Caches haben allerdings bei Mehrprozeßbetrieb<br />

einige Nachteile:<br />

• Dieselbe virtuelle Adresse kann (in verschiedenen Prozessen) auf unterschiedliche<br />

Speicherbereiche verweisen. Eine Lösung für dieses Problem liegt darin, daß das Betriebssystem<br />

bei jedem Prozeßwechsel den Cache-Inhalt mittels eines speziellen Maschinenbefehls<br />

löscht (cache flush).<br />

• Unterschiedliche virtuelle Adressen können (im Falle gemeinsamer Variablen) dieselbe<br />

Speicherstelle bezeichnen (address aliasing). Dadurch kann dieselbe Variable an<br />

mehreren Stellen im Cache gespeichert sein. Wird einer der Einträge modifiziert, ist<br />

Dateninkonsistenz die Folge. Es liegt daher nahe, gemeinsame Daten von einer Speicherung<br />

im Cache auszuschließen (non-cacheable zu setzen).<br />

• Werden Daten z. B. bei einem Eingabevorgang von einem DMA-Werk (Verweis auf<br />

Bode) im (real adressierten) Hauptspeicher verändert, sind deren gegebenenfalls im<br />

Cache existierende Kopien veraltet; wieder liegt eine Dateninkonsistenz vor. Im Falle<br />

eines virtuellen Caches besteht keine Möglichkeit, diese gezielt aufzuheben, da dazu<br />

die virtuelle Adresse aus der Hauptspeicheradresse rückermittelt werden müßte.

C3.2 Caches 215<br />

Virtuelle Adressierung wird aus diesen Überlegungen überwiegend bei prozessorinternen<br />

Befehls-Caches eingesetzt.<br />

Bei sog. physischen Caches muß erst der Vorgang der Adreßumsetzung abgewartet<br />

werden, bis das Vorliegen des referenzierten Wortes im Cache an Hand der realen Adresse<br />

geprüft werden kann. Allerdings sind physische Caches bezüglich der Dateninkonsistenz<br />

wesentlich günstiger. Beispielsweise kann eine DMA-Einheit für die Konsistenz zwischen<br />

Haupt- <strong>und</strong> Cache-Speicher sorgen, da beide real adressiert sind. Ebenso kann in<br />

einem Multiprozessorsystem die Kohärenz mehrerer Caches sichergestellt werden (Verweis<br />

auf Volkert). Reale Adressierung ist daher meist bei prozessorexternen Caches vorzufinden.<br />

3.2.4 Organisationsformen<br />

Die Organisationsform eines Caches legt fest, in welchem Cache-Block ein Hauptspeicherblock<br />

abgelegt wird (Plazierungsproblem; mapping problem) <strong>und</strong> wie ein gewünschter<br />

Block im Cache aufzufinden ist (Identifikationsproblem; identification problem).<br />

Drei Organisationsformen sind gebräuchlich: direkte Abbildung (direct mapped), voll assoziative<br />

Abbildung (fully associative) <strong>und</strong> n-fach assoziative Abbildung (n-way set associative<br />

cache). Bild 3 verdeutlicht für diese Möglichkeiten beispielhaft, wo ein Hauptspeicherblock<br />

im Cache gespeichert werden kann.<br />

Blocknummern<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

Direkte<br />

Abbildung<br />

Vollassoziative<br />

Abbildung<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

Caches<br />

2-fach assoziative<br />

Abbildung<br />

0<br />

1<br />

Satz 0<br />

2<br />

3<br />

Satz 1<br />

4<br />

5<br />

Satz 2<br />

6<br />

Satz 3<br />

7<br />

Bild 3 Plazierung eines Hauptspeicherblocks für die drei Cache-Organisationsformen<br />

. . . . .<br />

. . . . .<br />

Hauptspeicher<br />

In einem direkt abbildenden Cache mit einer Kapazität von N Blöcken wird ein Hauptspeicherblock<br />

B im Cache-Block B mod N gespeichert. In einem voll assoziativen Cache<br />

kann ein Hauptspeicherblock in jede Cache-Zeile übernommen werden. Ein n-fach assoziativer<br />

Cache ist in M = N/n sog. Sätze (sets) mit jeweils n Blöcken untergliedert; Block<br />

B kann im Satz B mod M in jeder der darin enthaltenen n Cache-Zeilen abgelegt werden.<br />

Damit ist die n-fach assoziative Abbildung die allgemeine Organisationsform, die mit<br />

n=N (nur ein Satz) zur vollassoziativen <strong>und</strong> mit n=1 (M=N Sätze) zur direkten (auch: einfach<br />

assoziativen) Form wird.<br />

Jeder Cache-Zeile ist eine große Anzahl von Hauptspeicherblöcken zugeordnet, d.h., es<br />

können verschiedene Hauptspeicherblöcke in einer Cache-Zeile gespeichert werden.<br />

Daher wird ein Mechanismus benötigt, der einen Hauptspeicherblock eindeutig kennzeichnet<br />

<strong>und</strong> seine Identifikation im Cache erlaubt. Dies wird im weiteren für den allgemeinen<br />

Fall eines n-fach assoziativen Caches erläutert.<br />

13<br />

14<br />

15<br />

16<br />

17<br />

18<br />

C3

216 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

a<br />

b<br />

c<br />

2<br />

Satz 0<br />

Kennung (tag) V D Daten<br />

Blockadresse<br />

Kennung (tag) Index<br />

1<br />

63<br />

31<br />

Kennung (tag)<br />

Offset<br />

0<br />

Kennung (tag) Index Byte 1<br />

22<br />

6 4<br />

3<br />

V Daten (16 Bytes)<br />

4<br />

K ≥1 Treffer<br />

K<br />

K ... Komparator<br />

Bild 4 Identifikation eines Blocks in einem zweifach assoziativen Cache.<br />

a Inhalt einer Cache-Zeile; b Aufbau der Adresse; c schematische Darstellung der Adressierung<br />

Bild 4 a zeigt, daß für jeden Hauptspeicherblock im Cache neben der eigentlichen Dateninformation<br />

<strong>und</strong> einigen Verwaltungsbits eine Kennung (tag) gehalten wird. Das Gültigkeitsbit<br />

V (valid bit) sagt aus, ob diese Zeile überhaupt aktuelle Daten enthält. Die Kennung<br />

wird der an den Cache angelegten Adresse entnommen. Bild 4 b verdeutlicht dazu<br />

die Interpretation einer Adresse. Sie ist unterteilt in eine Blockadresse <strong>und</strong> einen Offset,<br />

der das gewünschte Datum (z. B. Byte) innerhalb des Blocks anwählt. Die Blockadresse<br />

setzt sich zusammen aus der Kennung, das sind die zur eindeutigen Identifikation des<br />

Blocks erforderlichen höchstwertigen Adreßbits, <strong>und</strong> dem sog. Index. Dieser selektiert bei<br />

einem Cache-Zugriff den Satz, in dem der gewünschte Block plaziert sein kann. Daraufhin<br />

wird die in der angelegten Adresse vorhandene Kennung mit allen im Satz gespeicherten<br />

Kennungen assoziativ verglichen, um das Vorhandensein oder Fehlen des gewünschten<br />

Blocks im Cache zu erkennen. Bild 4 c veranschaulicht die Schritte dieses<br />

Adressierungsvorgangs für einen zweifach assoziativen Cache mit 128 Blöcken (64<br />

Sätze) der Größe 16 Bytes. Schritt 1 bezeichnet die Adreßinterpretation, Schritt 2 die Satzanwahl,<br />

Schritt 3 das Auslesen <strong>und</strong> die Vergleiche der Kennungen, was nur für gültige<br />

Cache-Einträge nötig <strong>und</strong> sinnvoll ist. In Schritt 4 schließlich wird das Zugriffsergebnis<br />

ermittelt <strong>und</strong> an den Prozessor geleitet. Die Ansteuerung der richtigen Cache-Zeile <strong>und</strong><br />

das Auslesen bzw. Verändern des gewünschten Datenbytes oder -wortes sind der Übersichtlichkeit<br />

halber nicht gezeigt.<br />

Für einen n-fach assoziativen Cache werden n Vergleicher (Komparatoren) benötigt. Ein<br />

direkt abbildender Cache erfordert daher mit nur einem Vergleicher den geringsten Hardware-Aufwand,<br />

da für jeden Speicherblock die aufnehmende Cache-Zeile eindeutig feststeht.<br />

Dies führt aber zu dem Problem, daß schon zwei Blöcke, die auf dieselbe Cache-

C3.2 Caches 217<br />

Zeile abgebildet werden, bei gleichzeitiger Nutzung einander aus dem Cache verdrängen.<br />

Häufiges Umladen der Inhalte ist die Folge; die Wirksamkeit des Caches sinkt. Abhilfe<br />

schaffen größere Caches, weil bei ihnen die Wahrscheinlichkeit solcher Konfliktsituationen<br />

geringer ist. Das Problem wird aber auch mit steigendem Assoziativitätsgrad entschärft,<br />

da für jeden Block die Anzahl der in Frage kommenden Cache-Zeilen steigt. Vollassoziative<br />

Caches sind also am effektivsten, aber sehr teuer <strong>und</strong> langsamer als direkt<br />

abbildende Caches. Heute werden Caches mit Assoziativitätsgrad 2, 4 oder 8 bevorzugt.<br />

Sie bieten einen guten Kompromiß zwischen Realisierungsaufwand, Geschwindigkeit<br />

<strong>und</strong> Wirksamkeit.<br />

3.2.5 Aktualisierungsstrategie<br />

Wenn Daten in einem Cache verändert werden, stellt sich das Problem, wie <strong>und</strong> wann der<br />

korrespondierende Hauptspeicherinhalt aktualisiert <strong>und</strong> so Konsistenz zwischen Cache<br />

<strong>und</strong> Hauptspeicher hergestellt wird (Datenkonsistenzproblem; consistency problem).<br />

Zwei gr<strong>und</strong>sätzliche Strategien existieren: Durchschreiben (write through) <strong>und</strong> Zurückschreiben<br />

(write back, copy back). Durchschreiben bedeutet, daß jede Änderung im<br />

Cache sofort auch im Hauptspeicher vollzogen wird. Damit ist jederzeit Datenkonsistenz<br />

gegeben. Das ist in einem Mehrprozessorsystem <strong>und</strong> bei autonomen Ein-/Ausgabeeinheiten<br />

von Vorteil, führt aber zu einer hohen Belastung des Prozessor-/Speicherbusses.<br />

Primär-Caches arbeiten in der Regel nach diesem Prinzip. Zurückschreiben vermeidet<br />

diesen Nachteil, indem Änderungen zunächst auf den Cache beschränkt bleiben. Sie<br />

werden erst dann auch im Hauptspeicher durchgeführt, wenn ein beschriebener Block aus<br />

dem Cache verdrängt wird oder ein Zugriff eines anderen Prozessors oder eine Ausgabeoperation<br />

die Aktualisierung veranlaßt (Verweis auf Volkert <strong>und</strong> 3.2.3). Um bei dieser<br />

Strategie das Zurückschreiben nicht modifizierter Blöcke zu vermeiden, wird in jeder<br />

Cache-Zeile ein Modifikationsbit D (dirty bit) mitgeführt (Bild 4). Sek<strong>und</strong>är-Caches verwenden<br />

häufig Zurückschreiben.<br />

3.2.6 Ersetzungsstrategie<br />

Die Ersetzungsstrategie bestimmt beim Laden eines neuen Speicherblocks in den Cache,<br />

welche Cache-Zeile überschrieben wird, wenn keine in Frage kommende Zeile mehr frei<br />

ist (Ersetzungsproblem; replacement problem).<br />

Bei einem direkt abbildenden Cache stellt sich diese Frage nicht: Der zu verdrängende<br />

Block ist eindeutig bestimmt. Bei den assoziativen Cache-Speichern sind verschiedene<br />

Strategien möglich. Die beiden gebräuchlisten sind eine LRU-Strategie (least recently<br />

used) <strong>und</strong> ein (pseudo-)zufälliges Auswahlverfahren (random).<br />

Beim Ersetzen nach dem LRU-Prinzip wird jener Block ausgewählt, auf den am längsten<br />

nicht mehr zugegriffen wurde. Dazu wird in den Verwaltungsbits der Cache-Zeilen eine<br />

Alterungsinformation gespeichert <strong>und</strong> bei jedem Zugriff fortgeschrieben.<br />

Sehr geringen Hardware-Aufwand verursacht eine Ersetzungsstrategie auf Basis eines<br />

Pseudozufallsgenerators. Sie liefert auch überraschend gute Ergebnisse [Smith 82], da in<br />

jedem Satz die zu verdrängenden Blöcke gleichverteilt ausgewählt werden, unter denen<br />

mit einiger Wahrscheinlichkeit auch nicht mehr benötigte Blöcke sind.<br />

3.2.7 Leistungsbetrachtungen<br />

Caches sollen die mittlere Speicherzugriffszeit eines Prozessors minimieren. Ihr Entwurf<br />

<strong>und</strong> ihre effiziente Implementierung sind hochkomplexe Aufgaben. Aus der Fülle der Li-<br />

C3

218 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

teratur zu Entwurf <strong>und</strong> Leistung von Caches seien hier nur [Smith 82] <strong>und</strong> [Przybylski 90]<br />

herausgegriffen. In der allgemeinen Literatur sind die Leistungsaspekte systematisch <strong>und</strong><br />

umfassend dargestellt.<br />

Leistungsbetrachtungen zu Caches können sich an folgender Formel für die mittlere<br />

(auch: effektive) Speicherzugriffszeit Te für eine zweistufige <strong>Arbeitsspeicher</strong>hierarchie<br />

(Cache <strong>und</strong> Hauptspeicher) orientieren:<br />

Te = h⋅Th + m⋅Tm (1)<br />

Dabei bezeichnen h <strong>und</strong> m = 1−h die Treffer- bzw. Fehlzugriffsraten im Cache (hit rate,<br />

miss rate), Th die Cache-Zugriffszeit (hit time) <strong>und</strong> Tm die Cache-Ladezeit (miss time).<br />

Die mittlere Speicherzugriffszeit Te kann somit durch die im weiteren beschriebenen drei<br />

Maßnahmen reduziert werden. Optimierung an einer Größe bewirkt dabei aber meist eine<br />

Verschlechterung einer oder der beiden anderen. Es gilt, einen guten Kompromiß zwischen<br />

den Einflußfaktoren zu finden.<br />

Reduktion der Fehlzugriffsrate m. Dies gelingt durch Vergrößerung des Caches oder<br />

höheren Assoziativitätsgrad. Beides macht ihn teurer <strong>und</strong> erhöht auch, wie erwähnt, die<br />

Zugriffszeit Th. Größere Blöcke sind eine weitere Möglichkeit, da sie verstärkt räumliche<br />

Lokalität nutzen; dadurch wird aber die Nachladezeit Tm erhöht. In assoziativen Caches<br />

kann auch eine verbesserte Ersetzungsstrategie Vorteile ergeben. Speziell für direkt abbildende<br />

Caches wurde jüngst der Einsatz eines kleinen „Neben“-Caches (engl. victim<br />

cache) vorgeschlagen: In ihnen werden die zuletzt verdrängten Blöcke zwischengespeichert,<br />

so daß der erneute Zugriff auf sie viel schneller ist, als wenn sie im Hauptspeicher<br />

wären. Eine weitere wirksame Technik ist explizites vorausgreifendes Laden (prefetching)<br />

von Blöcken in den Cache. Dies kann durch Hardware erfolgen oder durch spezielle<br />

Befehle durch den Übersetzer veranlaßt werden.<br />

Reduktion der Cache-Zugriffszeit Th. Die Zugriffszeit zu einem Primär-Cache im Falle<br />

eines Treffers ist heute vielfach entscheidend für die Prozessortaktrate; bei einem Sek<strong>und</strong>är-Cache<br />

bestimmt sie die Anzahl der Wartezyklen für den Prozessor. Kurze Zugriffszeiten<br />

erhält man bei kleinen <strong>und</strong> einfach organisierten Caches, was der ersten Optimierung<br />

zuwiderläuft. Einen zusätzlichen Vorteil bieten hier direkt abbildende Caches,<br />

da sich die Vergleiche der Kennungen (tags) <strong>und</strong> Anwahl <strong>und</strong> Übertragung der gewünschten<br />

Daten überlappen können.<br />

Reduktion der Cache-Ladezeit Tm . Bereits angesprochen wurde die Möglichkeit, bei<br />

einem Fehlzugriff nicht direkt auf den Hauptspeicher zugreifen zu müssen, sondern einen<br />

Sek<strong>und</strong>är-Cache zwischenzuschalten. In diesem Fall ergibt sich Tm selbst gemäß einer zu<br />

(1) analogen Formel. In den letzten Jahren wurden zur Unterstützung schneller Prozessoren<br />

aufwendige sog. nichtblockierende Caches eingeführt (non-blocking caches). Sie<br />

ermöglichen mehrere ausstehende Speicherzugriffe <strong>und</strong> können bei Treffern Daten an den<br />

Prozessor liefern, selbst wenn das Nachladen eines Blocks im Gange ist. Schließlich ist<br />

Tm maßgeblich durch die Geschwindigkeit des Prozessor-/Speicherbusses <strong>und</strong> des Hauptspeichers<br />

bestimmt. Maßnahmen zur Leistungssteigerung dieser Komponenten <strong>und</strong> zur<br />

Abstimmung mit den Caches werden in den folgenden Abschnitten besprochen.<br />

3.3 Hauptspeicher<br />

In diesem Abschnitt werden Komponenten <strong>und</strong> Organisationsformen des Hauptspeichers<br />

moderner Rechensysteme behandelt. Der Hauptspeicher ist ein großer, flüchtiger Halbleiterspeicher<br />

mit wahlfreiem Zugriff <strong>und</strong> Lese- <strong>und</strong> Schreibmöglichkeit (random access<br />

memory, RAM), in dem Programme <strong>und</strong> Daten von Benutzern <strong>und</strong> Betriebssystem wäh-

C3.3 Hauptspeicher 219<br />

rend der Ausführung gehalten werden. Daneben kommen in heutigen Rechnern nichtflüchtige<br />

Halbleiterspeicher zum Einsatz, auf die nur oder vorwiegend lesend zugegriffen<br />

wird. Sie dienen zum Beispiel dazu, System-, Mikro- oder sonstige Steuerprogramme,<br />

Funktionstabellen oder Geräteinformation zu speichern. Auf diese ROM-Speicher (read<br />

only memory) <strong>und</strong> ihre programmierbaren <strong>und</strong> auch beschreibbaren Varianten (read<br />

mostly memory) wird hier nicht eingegangen.<br />

Die Strukturierung des <strong>Arbeitsspeicher</strong>s in Segmente <strong>und</strong> Seiten, Adressierung <strong>und</strong><br />

Adreßübersetzung sowie die Prinzipien des virtuellen Speichers bilden ein Grenzgebiet<br />

zwischen Rechnerarchitektur <strong>und</strong> Betriebssystemen. Diese Themen werden bei Betriebssystemen<br />

besprochen (Verweis auf Borrmann). Im weiteren wird das Anliegen einer<br />

realen Adresse am Hauptspeicher zugr<strong>und</strong>egelegt.<br />

3.3.1 Speicherbausteine<br />

Der Hauptspeicher heutiger Computer wird fast immer aus DRAM-Bausteinen aufgebaut<br />

(dynamic RAM). Nur in Höchstleistungsrechnern <strong>und</strong> für Cache-Speicher kommen die<br />

schnelleren, aber wesentlich teureren SRAM-Bausteine zum Einsatz (static RAM).<br />

DRAM-Chips enthalten im Kern eine Speichermatrix, an deren Knotenpunkten eine oder<br />

einige 1-Bit-Speicherzellen liegen. Bild 5 zeigt einen DRAM-Baustein der Größe 4M×1<br />

Bits. Eine Speicherzelle besteht aus nur einem Transistor <strong>und</strong> einem Kondensator. Die<br />

Zellen werden über eine Zeilen- <strong>und</strong> eine Spaltenadresse angesprochen. Um Adreßanschlüsse<br />

zu sparen, wird die Adresse im Zeitmultiplexbetrieb angelegt. Die Gültigkeit der<br />

Adreßteile wird mittels der Signale RAS (row address select) bzw. CAS (column address<br />

select) bekanntgegeben. Die Signale WE <strong>und</strong> OE dienen der Lese-/Schreib- <strong>und</strong> Bausteinanwahl.<br />

Mit der Zeilenadresse wird zuerst eine gesamte Zeile aus der Speichermatrix entnommen<br />

<strong>und</strong> gepuffert, mit der Spaltenadresse das bzw. die gewünschten Bits gelesen<br />

oder geschrieben. Ein Nachteil der kompakten Realisierung der Speicherzellen ist, daß<br />

das Lesen (Entnehmen einer Zeile bei RAS) zerstörend wirkt. Um Informationsverlust zu<br />

verhindern, muß die Zeile vom Lese-/Schreibverstärker wieder zurückgeschrieben<br />

werden. Durch Leckströme droht ebenfalls die Zerstörung der Speicherinhalte. Daher<br />

muß innerhalb einer bestimmten Zeit (typisch alle 8 ms) jede Zeile regeneriert werden.<br />

Häufig übernimmt die externe Speichersteuereinheit die Kontrolle über diesen Vorgang<br />

des periodischen Auffrischens (refresh).<br />

SRAM-Bausteine sind ähnlich aufgebaut. Unterschiede bestehen darin, daß jede 1-Bit-<br />

Zelle ein vollständiges Flipflop enthält (häufig sechs Transistoren), die Regeneration der<br />

Speicherinhalte damit entfällt <strong>und</strong> alle Adreßleitungen zugleich angelegt werden.<br />

C3

220 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

RAS<br />

A 0 ...A 10<br />

CAS<br />

D in<br />

WE<br />

OE<br />

Z<br />

A<br />

R<br />

S<br />

A<br />

R<br />

LSS<br />

Speichermatrix 2048×2048 Bits<br />

Z<br />

A<br />

D<br />

.<br />

.<br />

.<br />

1-Bit-Zelle<br />

. . .<br />

LSV<br />

. . .<br />

SAD<br />

ZAR ... Zeilenadreßregister<br />

SAR ... Spaltenadreßregister<br />

ZAD ... Zeilenadreßdecodierer<br />

SAD ... Spaltenadreßdecodierer<br />

LSV ... Lese-/Schreibverstärker<br />

LSS ... Lese-/Schreibsteuerung<br />

Bild 5 Schematische Darstellung eines DRAM-Bausteins mit 4M×1 Bits (ohne Refresh-Logik)<br />

Wichtige Attribute von Speichern sind ihre Kapazität, die Datenbreite, die Zugriffszeit<br />

(auch Latenz genannt) <strong>und</strong> die Zykluszeit. Bei DRAMs ermöglicht der Minimalaufwand<br />

pro Zelle sehr hohe Integrationsdichten <strong>und</strong> Kapazitäten von bis zu 64 MBits je Chip. Datenbreiten<br />

(Organisationsformen) von 1, 4 oder 8 je Zugriff parallel übertragenen Bits sind<br />

gebräuchlich. Die Zugriffszeit, also die Zeit zwischen Anlegen der Adresse <strong>und</strong> Verfügbarkeit<br />

der Daten beim Lesen, liegt heute bei etwa 60 ns (wobei beispielsweise 50 ns auf<br />

die RAS- <strong>und</strong> 10 ns auf die CAS-Zeit entfallen). Die Zykluszeit – die Mindestzeit, die<br />

zwischen zwei aufeinanderfolgenden Zugriffen verstreichen muß – beträgt etwa 90 ns. Sie<br />

ist höher als die Zugriffszeit, weil sich der Baustein vom Auslesen einer Speicherzeile<br />

durch das Rückschreiben erst erholen muß. SRAM-Bausteine haben grob um den Faktor<br />

8 geringere Kapazität <strong>und</strong> Zugriffszeit <strong>und</strong> höhere Kosten als DRAM-Komponenten; Zykluszeit<br />

<strong>und</strong> Zugriffszeit sind bei ihnen gleich.<br />

3.3.2 Gr<strong>und</strong>legender Speicheraufbau<br />

Für den Aufbau von wortbreiten Speicherstrukturen müssen mehrere Speicherbausteine<br />

parallel angeordnet <strong>und</strong> angesteuert werden. In Bild 6 ist dies am Beispiel des Aufbaus<br />

eines byteadressierbaren 16 MByte-Speichers mit 32-Bit-Worten aus 4M×1-Bit-DRAMs<br />

skizziert.<br />

a<br />

b<br />

16M−4<br />

31<br />

16M−3<br />

Bild 6 Beispiel eines Speicheraufbaus <strong>und</strong> zugehörige Adreßinterpretation.<br />

a 16-MByte-Speicherbank mit 32-Bit-Worten aus 4M×1-Bit-DRAM-Chips; b Aufteilung der<br />

D out<br />

RAS ... Row Address Select<br />

CAS ... Column Address Select<br />

WE ... Write Enable<br />

OE ... Output Enable<br />

Ai ... Adresse<br />

Din , Dout ... Ein-, Ausgangsdaten<br />

4M×1-Bit-DRAM 4−MByte-Block Byteadresse Bitnummer<br />

31<br />

0<br />

4<br />

. . . 24 23<br />

1<br />

5<br />

. . . 16 15<br />

2<br />

6<br />

. . . 8 7<br />

3<br />

7<br />

. . .<br />

im Wort<br />

0<br />

Wort<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

23<br />

Wortadresse<br />

2 1 0<br />

16M−2<br />

16M−1<br />

Blockanwahl (=Byteanwahl im Wort)

Adresse<br />

C3.3 Hauptspeicher 221<br />

Eine (nicht dargestellte) Speichersteuereinheit (memory controller) sorgt für Adreßinterpretation,<br />

Wortadressierung <strong>und</strong> Anwahl eines oder mehrerer Byte-Blöcke so, daß das geforderte<br />

Byte, Halbwort oder Wort gelesen oder geschrieben wird. Die Adresse wird in<br />

einem Speicheradreßregister SAR abgelegt, das Datum in einem Speicherdatenregister<br />

SDR (Verweis auf Bild 1 bei Bode). Eine solche Anordnung mit eigener Ansteuerlogik<br />

heißt Speicherbank (memory bank). [Rhein 1992] behandelt dieses Thema näher.<br />

3.3.3 Speicherverschränkung<br />

Ein moderner Prozessor (mit z. B. 200 MHz Taktfrequenz) wird bei aufeinanderfolgenden<br />

Zugriffen auf eine Speicherbank durch ihre Zykluszeit (z. B. 100 ns) gebremst <strong>und</strong> muß<br />

Wartezyklen einlegen. In diesem Fall reicht die Bandbreite des Hauptspeichers, das ist die<br />

Rate in Bytes/s, mit der Daten vom bzw. zum Speicher übertragen werden können, nicht<br />

aus. Im Beispiel kann der Prozessor nur in jedem 20. Takt auf den Speicher zugreifen.<br />

Eine erprobte Maßnahme zur Erhöhung der Speicherbandbreite ist die Speicherverschränkung<br />

(memory interleaving). Nach diesem Konzept werden mehrere Speicherbänke<br />

so angeordnet, daß benachbarte Worte in unterschiedlichen Bänken zu liegen<br />

kommen. Die Speicherbanknummer wird dabei meist durch niedrigwertige Adreßbits bestimmt<br />

(low-order interleaving). Bild 7 zeigt einen derart organisierten Speicher mit dem<br />

Verschränkungsgrad 4. Aufeinanderfolgende Worte liegen in benachbarten Speichereinheiten,<br />

mehrere Speicherzugriffe auf unterschiedliche Bänke können einander überlappen.<br />

Die Speichererholungszeit wird somit zum Teil vor dem Prozessor verborgen.<br />

Eine derartige Struktur unterstützt wirksam das Nachladen bzw. Rückschreiben von<br />

Cache-Zeilen. Verschränkungsgrad, Größe der Cache-Zeilen, Datenbusbreite sowie Busgeschwindigkeit<br />

<strong>und</strong> -protokoll (siehe Unterabschnitt 3.4.1) sind aber sorgfältig aufeinander<br />

abzustimmen.<br />

a<br />

b<br />

64M−16<br />

31<br />

Byte<br />

0<br />

16<br />

. .<br />

.<br />

Bank<br />

.<br />

0<br />

. .<br />

16−MByte-Speicherbank Byteadresse<br />

4<br />

20<br />

.<br />

.<br />

.<br />

64M−12<br />

25<br />

Wortanwahl in Bank<br />

Bild 7 Beispiel eines vierfach verschränkten Speichers.<br />

a 64-MByte-Speicher mit 16-MByte-Speicherbänken aus Bild 6; b Adreßinterpretation<br />

Probleme bereiten Zugriffsmuster, die Speicherbankkonflikte verursachen. Ein Beispiel<br />

ist das Durchlaufen einer linear im Speicher abgelegten Datenstruktur mit einer Schrittweite,<br />

die sich mit dem Verschränkungsgrad deckt; hier wird nur eine Speicherbank benutzt.<br />

Eine übergeordnete Steuereinheit (interleave controller) muß vermerken, auf<br />

welche Speicherbänke gerade zugegriffen wird <strong>und</strong> im Konfliktfall Wartezyklen für den<br />

8<br />

24<br />

.<br />

.<br />

.<br />

64M−8<br />

3 2 1 0<br />

Byteanwahl im Wort<br />

Bankanwahl<br />

12<br />

28<br />

.<br />

.<br />

.<br />

Bank 1 Bank 2 Bank 3<br />

64M−4<br />

C3

222 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

Prozessor erzeugen; die effektive Speicherbandbreite sinkt dadurch. Schwierig bei Speichern<br />

mit verschränkter Adressierung sind nachträgliche Speichererweiterungen.<br />

3.3.4 Weitere Maßnahmen zur Leistungssteigerung des Speichers<br />

Mit steigender Leistung der Mikroprozessoren wächst die Kluft zwischen der Arbeitsgeschwindigkeit<br />

der Prozessoren <strong>und</strong> der Zugriffsgeschwindigkeit (Latenz) <strong>und</strong> Bandbreite<br />

des Hauptspeichers, so daß trotz des Einsatzes von Caches der Speicherzugang den<br />

Engpaß in heutigen Rechensystemen bildet. Mit verschiedenen Architekturmaßnahmen<br />

versucht man, dieser Entwicklung entgegenzuwirken.<br />

Zur Verringerung der Latenz, die sich allein durch Weiterentwicklung der DRAM-Technologie<br />

nur mit etwa 10 % pro Jahr verringert, tragen spezielle Betriebsarten <strong>und</strong> neue Organisationsformen<br />

von DRAM-Bausteinen bei. Zugriffsarten, die heute bereits vielfach<br />

genutzt werden, sind Nibble-, Page- <strong>und</strong> Static Column-Modus. In diesen Modi entfällt<br />

bei Folgezugriffen zu einer von einem normalen Zugriff ausgelesenen Speicherzeile die<br />

RAS-Zeit; in verkürzten Zyklen (von z. B. 30 ns) wird auf drei Folgebits bzw. beliebige<br />

Teile in der aktiven Zeile zugegriffen. Neue DRAM-Chip-Architekturen wie Enhanced<br />

DRAM (EDRAM) <strong>und</strong> Cache DRAM (CDRAM) treiben diese Entwicklung weiter <strong>und</strong><br />

führen einen Cache auf dem Speicherbaustein ein, in dem die zuletzt benutzten Speicherzeilen<br />

vollständig oder teilweise gehalten werden <strong>und</strong> schnell verfügbar sind. An Bedeutung<br />

gewinnen synchrone DRAMs (SDRAMs), die im Gegensatz zu konventionellen Bausteinen<br />

synchronisiert mit dem Prozessor-/Speicherbus <strong>und</strong> dadurch schneller betrieben<br />

werden. Zusätzliche Merkmale sind der Einsatz von zwei Speichermatrizen auf dem Chip<br />

<strong>und</strong> ein Burst-Modus zur schnellen Übertragung von Datenblöcken aus derselben Speicherzeile.<br />

Diese neuen Bausteine sind etwa in [CompCon 94] beschrieben.<br />

Die Bandbreite eines Speichers kann durch Änderungen an der Architektur eines Rechners<br />

gesteigert werden. Neben verschränkter Adressierung sind geeignete Maßnahmen<br />

eine breite Organisation des Speichersystems <strong>und</strong> des Datenbusses (heute bis zu 256 Bits)<br />

sowie die Überlappung von Buszyklen <strong>und</strong> die Nutzung von Blocktransfers des Busses<br />

(siehe Unterabschnitt 3.4.5), die auf seiten des Hauptspeichers die oben angegebenen speziellen<br />

Zugriffsarten nutzen. Caches, Hauptspeicher <strong>und</strong> Bussystem müssen gut aufeinander<br />

abgestimmt sein, damit diese Maßnahmen leistungssteigernd zur Wirkung<br />

kommen. In den letzten Jahren wurden neuartige Prinzipien zur speziellen Kopplung von<br />

Prozessor <strong>und</strong> Speicherbausteinen vorgeschlagen. Beispiele sind Rambus [CompCon 94]<br />

<strong>und</strong> RamLink [Gjessing 92]. Die Integration von Prozessoren <strong>und</strong> DRAMs auf gemeinsamen<br />

Halbleiterbausteinen wird derzeit erforscht.<br />

3.4 <strong>Bussysteme</strong><br />

3.4.1 Gr<strong>und</strong>lagen von Bussen<br />

Da spezielle Kommunikationspfade zwischen den Funktionseinheiten eines Rechensystems<br />

aus Leistungsgründen zwar wünschenswert, für die meisten Systeme aber zu<br />

teuer <strong>und</strong> für Erweiterungen zu unflexibel sind, werden heute vornehmlich gemeinsam benutzte<br />

Kommunikationswege, d. h. Busstrukturen, eingesetzt. Ein Bus ist ein Bündel von<br />

funktional zusammengehörigen Signalleitungen, das Komponenten eines digitalen Systems<br />

zum Informationsaustausch miteinander verbindet. Sendet ein Teilnehmer Informationen<br />

über den Bus, können alle anderen sie empfangen. Um Informationsverfälschung

C3.4 <strong>Bussysteme</strong> 223<br />

auszuschließen, muß aber sichergestellt werden, daß zu jedem Zeitpunkt nur ein Teilnehmer<br />

die Kontrolle über den Bus <strong>und</strong> damit Senderechte innehat.<br />

Damit wird ein prinzipieller Nachteil einer Busstruktur deutlich: Weitere sendebereite<br />

Teilnehmer müssen warten, der Bus wird zu einer knappen Ressource <strong>und</strong> damit zu einem<br />

potentiellen Engpaß. Die Vorteile sind der im Verhältnis zu speziellen Verbindungen geringe<br />

Hardware-Aufwand <strong>und</strong> die Flexibilität bei Systemerweiterungen.<br />

Ein Bus wird nach der Art der übertragenen Informationen in drei Gruppen von Leitungen<br />

(Teilbusse) unterteilt: Daten-, Adreß- <strong>und</strong> Steuerbus. (Der Versorgungsbus, der Leitungen<br />

z. B. zur Strom- <strong>und</strong> Taktversorgung, Systeminitialisierung oder Anzeige von Hardware-<br />

Fehlern enthält, wird im weiteren nicht betrachtet.) Wie in Bild 8 angedeutet, werden die<br />

Datenleitungen bidirektional betrieben, die Adreßleitungen meist unidirektional, ebenso<br />

die meisten Steuersignale. Die Signale können prozessorspezifisch (für prozessornahe<br />

Hochleistungsbusse) oder prozessorunabhängig sein (z. B. bei Standardbussen).<br />

Versorgungsbus<br />

Steuerbus<br />

Adreßbus<br />

Datenbus<br />

Prozessorkarte<br />

Bus-SS<br />

Speicherkarte<br />

Bus-SS<br />

Speicherkarte<br />

Bus-SS<br />

E/A-<br />

Einheit<br />

Bus-SS<br />

Bussteuereinheit<br />

Bus-SS<br />

Bild 8 Gr<strong>und</strong>legender Aufbau von Bussen <strong>und</strong> Ankopplung von Busteilnehmern<br />

SS ...<br />

Schnittstelle<br />

Auf die verschiedenen Typen <strong>und</strong> Hierarchiestufen von Bussen sowie die darüber verb<strong>und</strong>enen<br />

Komponenten wurde bereits am Anfang dieses Kapitels hingewiesen. Einheiten,<br />

die eigenständig auf dem Bus aktiv werden <strong>und</strong> ihn steuern können, z. B. ein Prozessor<br />

oder DMA-Werk, werden als Master bezeichnet, rein passive Komponenten, z. B. Speicherkarten,<br />

als Slaves. Bei mehreren Bus-Mastern muß über die Zuteilung der Kontrolle<br />

über den Bus entschieden werden. Dieser Vorgang heißt Buszuteilung oder Busarbitrierung<br />

(bus arbitration). Die Funktionseinheiten sind über eigene Busschnittstellen (bus interface<br />

unit) mechanisch <strong>und</strong> elektrisch an den Bus angekoppelt. Sie gleichen z. B. Signale,<br />

Abläufe <strong>und</strong> Geschwindigkeiten an die Gegebenheiten auf dem Bus an <strong>und</strong> stellen<br />

Pufferplatz bereit. Zentrale Versorgungsdienste <strong>und</strong> Funktionen werden von der Bussteuereinheit<br />

(bus controller) wahrgenommen. Jeder Komponente am Bus, auch E/A-Einheiten,<br />

sind Adreßbereiche (im physischen Adreßraum) zugeordnet. Die Einheiten<br />

können damit über Adressen angesprochen werden, gegebenenfalls zusammen mit<br />

Steuersignalen.<br />

Alle Eigenschaften eines Bussystems sind detailliert in einer sog. Busspezifikation festgelegt.<br />

Sie definiert die Signale, die mechanischen <strong>und</strong> elektrischen Merkmale <strong>und</strong> vor allem<br />

die Busfunktionen <strong>und</strong> Busprotokolle. Dies sind Regeln für die Kommunikationsabläufe<br />

zwischen Busteilnehmern zur Erbringung der Busfunktionen. Sie legen insbesondere Art,<br />

Form <strong>und</strong> Zeitverhalten der auszutauschenden Signale fest. Busspezifikationen werden<br />

häufig von Standardisierungsgremien erarbeitet oder von Firmen offengelegt. Dadurch<br />

können verschiedene Hersteller unterschiedliche Komponenten entwickeln, die über den<br />

Bus zusammenarbeiten.<br />

C3

224 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

3.4.2 Merkmale von Bussen<br />

Je nach Einsatzbereich <strong>und</strong> Leistungsanforderungen unterscheiden sich <strong>Bussysteme</strong> in<br />

einer Reihe von Merkmalen. Wesentliche funktionale Unterscheidungsmerkmale sind:<br />

• Busbreite, vor allem der Daten- <strong>und</strong> Adreßbusse. Gr<strong>und</strong>sätzlich unterscheidet man hier<br />

serielle <strong>und</strong> parallele Busse. Serielle Busse dienen häufig zum Anschluß langsamer peripherer<br />

Geräte oder/<strong>und</strong> zur Überbrückung großer Entfernungen. Parallele Busse verfügen<br />

über mehrere Adreß- <strong>und</strong> Datenleitungen für größere Übertragungsleistungen.<br />

Gebräuchlich sind heute 16, 32 oder bis zu 64 Adreß- <strong>und</strong> 8 bis 64 Datenleitungen, bei<br />

Multiprozessorbussen bis zu 256.<br />

• Betrieb von Adreß- <strong>und</strong> Datenleitungen. Sie stehen entweder als spezielle Leitungen<br />

für diesen Zweck zur Verfügung, oder es werden für Adresse <strong>und</strong> Daten im Zeitmultiplexbetrieb<br />

dieselben Leitungen benutzt, da sie bei einfachen Transaktionen zu verschiedenen<br />

Zeiten benötigt werden. Letzteres ist weniger aufwendig, erlaubt aber<br />

kaum beschleunigende Maßnahmen, z. B. Überlappung von Buszyklen.<br />

• Zeitsteuerung <strong>und</strong> Taktrate. Synchrone Busse arbeiten unter einem zentralen Taktgeber,<br />

der sämtliche Transaktionen steuert. Von Vorteil ist hier, daß die Abläufe auf<br />

dem Bus einfach sind <strong>und</strong> durch hohe Taktfrequenzen beschleunigt werden können;<br />

von Nachteil, daß alle Busteilnehmer an die vorgegebene Busgeschwindigkeit angepaßt<br />

sein müssen, <strong>und</strong> daß der Bus wegen der Taktsignallaufzeiten <strong>und</strong> -verzerrungen<br />

(clock skew) nur kurz sein kann. Prozessor-/Speicherbusse arbeiten üblicherweise synchron.<br />

Bei asynchronen Bussen geschieht die Steuerung der Bustransaktionen über den<br />

Austausch von speziellen Signalen zwischen den beteiligten Teilnehmern (handshaking).<br />

Der Vorteil ist, daß Geräte unterschiedlicher Geschwindigkeit zusammenarbeiten<br />

können, der Nachteil, daß die Transaktionen komplex sind. Manche Peripheriebusse<br />

sind asynchron.<br />

• Busfunktionen, einschließlich Arbitrierung. Siehe Unterabschnitt 3.4.3.<br />

3.4.3 Busfunktionen<br />

Busse transferieren vornehmlich Daten. Dazu wickeln sie sog. Bustransaktionen ab, die<br />

wiederum aus mehreren Buszyklen bestehen. Bustransaktionen sind unteilbare Abläufe;<br />

sie bestehen aus den Phasen Busarbitrierung, Adreß- <strong>und</strong> Datenübertragung <strong>und</strong> Busfreigabe.<br />

Die dabei <strong>und</strong> darüber hinaus vom Bus zu erfüllenden Funktionen werden im folgenden<br />

kurz beschrieben.<br />

Arbitrierung. Mit der Arbitrierung erwirbt ein Master das Recht, auf den Bus zuzugreifen;<br />

er wird zum Bus-Master. Gibt es nur einen Master am Bus, entfällt diese Phase.<br />

Da die Buszuteilung für jede Transaktion anfällt, soll sie schnell, zudem auch flexibel <strong>und</strong><br />

kostengünstig zu realisieren sein. Zahlreiche Varianten wurden entwickelt <strong>und</strong> implementiert:<br />

Strategien mit zentraler Arbitrierungseinheit (arbiter) oder dezentralen Einheiten in<br />

den Busschnittstellen der Master, prioritätengesteuerte oder faire Verfahren. Zur Vertiefung<br />

dieses Gebietes wird auf die allgemeine Literatur <strong>und</strong> [Färber 87] verwiesen.<br />

Datentransfers. Diese werden von einem Master angestoßen <strong>und</strong> gesteuert. Sie bestehen<br />

aus Adreßübertragung (Anwahl des Kommunikationspartners <strong>und</strong> der auszuführenden<br />

Operation) <strong>und</strong> eigentlicher Datenübertragung. Der Slave hat untergeordnete Funktion:<br />

Zum Steuerungsablauf trägt er nur durch Quittieren der Datenübernahme bzw. Signalisierung<br />

der Datenbereitstellung bei. Die wichtigsten Datentransportfunktionen sind Lesen<br />

(read) <strong>und</strong> Schreiben (write) eines Datenwortes. Eine atomar auszuführende Operation<br />

Lesen, Modifizieren <strong>und</strong> Zurückschreiben des geänderten Datums (read-modify-write)<br />

wird z. B. zur Realisierung von Semaphoren benötigt <strong>und</strong> ist insbesondere in Mehrpro-

C3.4 <strong>Bussysteme</strong> 225<br />

zessorsystemen vom Bus zu unterstützen. Die Übertragung von größeren Datenblöcken<br />

wird in Unterabschnitt 3.4.5 behandelt.<br />

Bild 9 verdeutlicht am einfachen Beispiel einer Leseoperation die Abläufe bei Datentransfers<br />

<strong>und</strong> die Unterschiede zwischen synchronen <strong>und</strong> asynchronen Bussen. Die verwendete<br />

Darstellungsmethode für Busprotokolle heißt Impulsdiagramm. Im synchronen Fall<br />

werden die Abläufe vom zentralen Bustakt gesteuert, wobei Signale bei aufsteigender<br />

Taktflanke gesetzt, bei absteigender abgefragt werden. Das Beispiel zeigt zudem, wie der<br />

Slave (z. B. ein Speicher) den Lesezyklus von zwei Takten um einen Wartezyklus verlängert<br />

(an der gestrichelten Linie), da seine Daten noch nicht gültig sind. Für den asynchronen<br />

Fall ist mit Pfeilen das Handshaking zwischen den Teilnehmern angedeutet.<br />

a Bustakt<br />

b<br />

Adresse<br />

Daten<br />

READ<br />

WAIT<br />

Lesezyklus mit<br />

1 Wartezyklus<br />

. . . Gültige Adresse bzw. Daten<br />

Überstrichene Signale sind 0-aktiv.<br />

Adresse<br />

READ<br />

Bild 9 Leseoperationen bei a synchronem <strong>und</strong> b asynchronem Bus (ohne Busarbitrierung)<br />

Vermittlung von Unterbrechungen (Interrupts). Unterbrechungen werden überwiegend<br />

von E/A-Geräten (Slaves) ausgelöst <strong>und</strong> sind vom Bus an den Prozessor weiterzuleiten.<br />

Viele Busse verfügen dazu über eigene Signalleitungen, über die Interrupts vermittelt<br />

werden. In diesem Fall wird keine Arbitrierung <strong>und</strong> kein aufwendiges Übertragungsprotokoll<br />

benötigt. Die Interrupt-Quellen sind meist nach verschiedenen Anordnungen<br />

<strong>und</strong> Verfahren priorisiert. Manche neueren Busse sparen Leitungen ein, indem sie Interrupts<br />

<strong>und</strong> zugehörige Statusinformation als Nachrichten hoher Priorität über den Datenbus<br />

in bestimmte Adreßbereiche übertragen. Dazu werden aber Buszyklen benötigt.<br />

Fehlerbehandlung. Bustransaktionen können scheitern, etwa durch Adressierungsfehler,<br />

Verletzung des Busprotokolls (meist des Zeitverhaltens) oder Hardware-Ausfall. Häufig<br />

werden Bustransaktionen von einer Uhr (watchdog timer) überwacht, die bei Ausbleiben<br />

der Reaktion eines Kommunikationspartners nach vorgegebener Zeit (timeout) eine Fehlerbehandlung<br />

anstößt, z. B. Wiederholung der Transaktion oder Rücksetzen des Systems.<br />

Sonstige Dienste. Darunter fallen beispielsweise Unterstützung der Systeminitialisierung<br />

oder des Rücksetzens, definiertes Abschalten von Busteilnehmern bei Spannungsverlust<br />

oder Neukonfiguration des Systems beim Entfernen <strong>und</strong> Einfügen von Karten im Betrieb.<br />

Cache-Kohärenz. Unterstützung für die Wahrung von Konsistenz zwischen mehreren<br />

Caches in Mehrprozessorsystemen ist heute eine wünschenswerte Eigenschaft von<br />

VAL<br />

ACK<br />

Daten<br />

Lesezyklus<br />

VAL . . . Adresse <strong>und</strong> Steuersignale gültig<br />

ACK . . . Daten gültig<br />

C3

226 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong><br />

Bussen. Dieses Problem <strong>und</strong> Lösungsansätze werden bei Multiprozessoren diskutiert<br />

(Verweis auf Volkert).<br />

3.4.4 Realisierung von Bussen<br />

Physisch sind die meisten Busse als geätzte Leitungen auf einer großformatigen Gr<strong>und</strong>karte<br />

realisiert, an die die zentralen Funktionseinheiten direkt angeschlossen sind. Bei Arbeitsplatzrechnern<br />

<strong>und</strong> Personal-Computern wird sie Gr<strong>und</strong>platine (motherboard) genannt.<br />

Zusätzlich können die Leitungen verlängert <strong>und</strong> mit Stecksockeln ausgestattet sein,<br />

in die meist senkrecht zur Gr<strong>und</strong>platine Erweiterungskarten (z. B. Grafik- oder Netzwerkkarten)<br />

eingeschoben oder über Flachbandkabel weitere Module (z. B. Festplatten) angeb<strong>und</strong>en<br />

sind. Rückwandbusse sind in einem festen Rahmen untergebrachte Platinen mit<br />

geätzten Leitungen <strong>und</strong> fest montierten Steckplätzen, in die alle Systemkomponenten<br />

senkrecht zur Rückwand eingesteckt werden. Über den Aufbau von Bussen sowie mechanische<br />

<strong>und</strong> elektrische Aspekte <strong>und</strong> Kenngrößen ist mehr z. B. in [Färber 87] zu finden.<br />

Bussen sind in ihrer Geschwindigkeit, Ausdehnung <strong>und</strong> Erweiterbarkeit physikalische<br />

Grenzen gesetzt. Zum einen begrenzt die Ausbreitungsgeschwindigkeit der Bussignale<br />

(<strong>und</strong> damit letztlich die Lichtgeschwindigkeit) die Länge <strong>und</strong> Geschwindigkeit von<br />

Bussen, da bei jeder Übertragung sichergestellt sein muß, daß die Signale bei allen Teilnehmern<br />

angekommen <strong>und</strong> stabil sind. Zum anderen entsteht auf dem Bus kapazitive<br />

Last, weil jeder Teilnehmer mit allen Signalleitungen verb<strong>und</strong>en ist. Dies schränkt die<br />

Zahl der möglichen Teilnehmer <strong>und</strong> die Übertragungsraten ein. Hochleistungsbusse sind<br />

daher kurz (maximal einen halben Meter), elektrisch sehr aufwendig gebaut <strong>und</strong> abgeschlossen.<br />

Einige Beiträge in [Zalewski 95] gehen ausführlich darauf ein.<br />

3.4.5 Maßnahmen zur Leistungssteigerung von Bussen<br />

Wichtigstes Leistungsmerkmal von Bussen ist ihre Übertragungsrate (bandwidth). Sie<br />

wird in MBytes/s ausgedrückt. Die maximale Übertragungsrate wird aus der Bustaktfrequenz,<br />

der Anzahl der Bustakte pro Datentransfer <strong>und</strong> der Anzahl der pro Transfer<br />

übertragenen Bytes ermittelt. Eine Leistungssteigerung kann also an diesen drei Faktoren<br />

ansetzen. Beispielsweise kann durch sorgfältige Realisierung die Taktfrequenz <strong>und</strong> durch<br />

einen breiten Datenbus die Datenmenge pro Transfer erhöht werden.<br />

Die Leistung eines Busses läßt sich auch durch Verbesserungen an den Protokollen steigern.<br />

Eine Möglichkeit liegt darin, die Anzahl der Arbitrierungsphasen zu vermindern.<br />

Ein Ansatz dazu ist das sog. bus parking, bei dem ein Master mit hoher Priorität die Kontrolle<br />

über den Bus so lange behält, bis sie ihm entzogen wird; er kann bis dahin viele<br />

Transaktionen abwickeln. Eine weitere Lösung bieten Blocktransfers (burst transfers).<br />

Hierbei werden zu Beginn eines Transfers Arbitrierung <strong>und</strong> Adressierung vorgenommen,<br />

in den Folgezyklen nur noch die Datentransfers. Andere Transaktionen werden dadurch<br />

lange zurückgestellt.<br />

Busaktivitäten können auch überlappend ausgeführt <strong>und</strong> dadurch der Bus im Fließbandbetrieb<br />

(als pipeline) betrieben werden. Getrennte Adreß- <strong>und</strong> Datenleitungen vorausgesetzt,<br />

kann während der Übertragung eines Datenworts bereits die nächste Adresse angelegt<br />

werden, oder es werden Arbitrierung <strong>und</strong> Transfers überlappt. Weitere Anordnungen<br />

sind denkbar <strong>und</strong> werden auch praktiziert. Fließbandverarbeitung macht die Bussteuerung<br />

komplexer, bringt aber eine deutliche Leistungssteigerung.<br />

Dieses Prinzip wird mit Bussen mit sog. geteilten Transaktionen (split transactions) fortgeführt.<br />

Transaktionen sind nun nicht mehr unteilbar, sondern in Anfrage (request) <strong>und</strong><br />

Antwort (response) geteilt, die als „Pakete“ über den Bus gesandt werden. Dadurch kann

C3.4 <strong>Bussysteme</strong> 227<br />

jeder Teilnehmer mehrere Transaktionen absenden, <strong>und</strong> auf dem Bus können viele Transaktionen<br />

aktiv sein. Dies ergibt sehr hohe Übertragungsraten.<br />

Schließlich kann man von synchroner Arbeitsweise <strong>und</strong> der üblichen elektrischen <strong>und</strong> mechanischen<br />

Auslegung von Bussen abgehen. Scalable Coherent Interface (SCI) [Gustavson<br />

92] ist ein neuer Verbindungsstandard, der typische Busfunktionen definiert, aber<br />

deren verteilte Realisierung auf Basis von Punkt-zu-Punkt-Verbindungen vorschlägt.<br />

Diese können asynchron sehr schnell betrieben werden <strong>und</strong> ermöglichen bei 16-Bit-Leitungen<br />

Datenraten bis zu 1 GByte/s.<br />

3.4.6 Gebräuchliche <strong>Bussysteme</strong><br />

Verbreitete <strong>Bussysteme</strong> aus den wichtigsten Hierarchiestufen eines Rechners sind: SCSI-<br />

2 (Small Computer System Interface), ein E/A-Bus mit bis zu 40 MBytes/s Übertragungsrate;<br />

PCI (Peripheral Component Interconnect), ein PC-Systembus <strong>und</strong> E/A-Bus mit 132<br />

bzw. 264 MBytes/s Übertragungsrate (bei 32 bzw. 64 Bits Datenbusbreite); MBus (Memory<br />

Bus von Sun), ein Workstations-Speicherbus mit 400 MBytes/s Übertragungsrate;<br />

<strong>und</strong> der standardisierte Rückwandbus Futurebus+, der mit einem 256 Bits breiten Datenbus<br />

bis zu 3200 MBytes/s übertragen kann.<br />

Allgemeine Literatur<br />

Flik, Th.; Liebig, H.: Mikroprozessortechnik. 4. Aufl. Berlin: Springer 1994<br />

Hennessy, J. L.; Patterson, D. A.: Computer architecture. A quantitative approach. Second Edition. San<br />

Francisco, CA: Morgan Kaufman 1996<br />

Liebig, H.; Flik, Th.: Rechnerorganisation. Prinzipien, Strukturen, Algorithmen. 2. Aufl. Berlin: Springer<br />

1993<br />

Patterson, D. A.; Hennessy, J. L.: Computer organization and design: The hardware/software interface. San<br />

Mateo, CA: Morgan Kaufman 1994<br />

Stallings, W.: Computer organization and architecture. Fourth Edition. Upper Saddle River, NJ: Prentice<br />

Hall 1996<br />

Spezielle Literatur<br />

[CompCon 94] CompCon Spring 94 (Digest of Papers): Session on new DRAM organizations. Los<br />

Alamitos, CA: IEEE Computer Society Press 1994<br />

[Denning 68] Denning, P.: The working set model for program behavior. Communications of the ACM 11<br />

(1968) 323-333<br />

[Färber 87] Färber, G. (Hrsg.): <strong>Bussysteme</strong>. Parallele <strong>und</strong> serielle <strong>Bussysteme</strong>, lokale Netze. 2. Aufl.<br />

München: Oldenbourg 1987<br />

[Gjessing 92] Gjessing, S.; Gustavson, D. B.; James, D. V.; Stone, G.; Wiggers, H.: A RAM link for high<br />

speed. IEEE Spectrum 29 (1992) 52-53<br />

[Gustavson 92] Gustavson, D. B.: The scalable coherent interface and related standards projects. IEEE<br />

Micro 12 (1992) 10-22<br />

[Smith 82] Smith, A. J.: Cache memories. Computing Surveys 14 (1982) 473-530<br />

[Przybylski 90] Przybylski, S. A.: Cache and memory hierarchy design. A performance-directed approach.<br />

San Francisco, CA: Morgan Kaufman 1990<br />

[Rhein 92] Rhein, D.; Freitag, H.: Mikroelektronische Speicher. Berlin: Springer 1992<br />

[Zalewski 95] Zalewski, J. (ed.): Advanced multimicroprocessor bus architectures. Los Alamitos, CA:<br />

IEEE Computer Society Press 1995<br />

C3

228 C3 <strong>Arbeitsspeicher</strong>- <strong>und</strong> <strong>Bussysteme</strong>