Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

EE207: Digital Systems I,<br />

Semester I 2003/2004<br />

CHAPTER 3 -ii: ii:<br />

Combinational Logic Design –<br />

Design Procedure, Encoders/<strong>Decoders</strong><br />

(Sections 3.4 – 3.6)

Design Procedure<br />

Code Converters<br />

Design Procedure<br />

Code Converters<br />

Binary <strong>Decoders</strong><br />

Overview<br />

Binary <strong>Decoders</strong><br />

Expansion<br />

Circuit implementation<br />

Circuit implementation<br />

Binary Encoders<br />

Priority Encoders

Combinational Circuit Design<br />

Design of a combinational circuit is the<br />

development of a circuit from a<br />

description of its function.<br />

Design<br />

Starts with a problem specification and<br />

produces a logic diagram or set of<br />

boolean equations that represent the<br />

circuit.

Design Procedure<br />

1. Determine the required number of inputs<br />

and outputs and assign variables to them.<br />

2. Derive the truth table that defines the<br />

required relationship between inputs and<br />

outputs.<br />

3. Obtain and simplify the Boolean function (K-<br />

maps, algebraic manipulation, CAD tools, …). ).<br />

Consider any design constraints (area, delay,<br />

power, available libraries, etc).<br />

4. Draw the logic diagram.<br />

5. Verify the correctness of the design.

Design Example<br />

Design a combinational circuit with 4<br />

inputs that generates a 1 when the # of<br />

1s equals the # of 0s. Use only 2-input 2 input<br />

NOR gates<br />

…

ore Examples - Code Converters<br />

Code Converters transform/convert<br />

information from one code to another:<br />

BCD-to BCD to-Excess Excess-3 3 Code Converter<br />

Useful in some cases for digital arithmetic<br />

BCD-to BCD to-Seven Seven-Segment Segment Converter<br />

Used to display numeric info on 7 segment<br />

displays

BCD CD-to to-Excess Excess-3 3 Code Converter<br />

Design a circuit that converts a binary-<br />

coded-decimal coded decimal (BCD) codeword to its<br />

corresponding excess-3 excess 3 codeword.<br />

Excess-3 Excess 3 code: Given a decimal digit n, , its<br />

corresponding excess-3 excess 3 codeword (n+3) 2<br />

Example:<br />

n=5 n+3=8 1000 excess-3 excess<br />

n=0 n+3=3 0011 excess-3 excess<br />

We need 4 input variables (A,B,C,D) and 4<br />

output functions W(A,B,C,D), X(A,B,C,D),<br />

Y(A,B,C,D), and Z(A,B,C,D).

BCD CD-to to-Excess Excess-3 3 Converter (cont.)<br />

The truth table relating the input and output variables is shown below<br />

Note that the outputs for inputs 1010 through 1111 are don't cares cares<br />

(n<br />

shown here).

Maps for BCD-to-Excess-3 Code Converter<br />

he K-maps K maps for are constructed using the don't care terms

CD-to CD to-Excess Excess-3 3 Converter (cont.

Another nother Code Converter Example:<br />

CD-to CD to-Seven Seven-Segment Segment Converter<br />

Seven-segment Seven segment display:<br />

7 LEDs (light emitting diodes), each one<br />

controlled by an input<br />

a<br />

1 means “on”, 0 means “off”<br />

Display digit “3”?<br />

f<br />

g<br />

b<br />

Set a, b, c, d, g to 1<br />

Set e, f to 0<br />

e<br />

d<br />

c

CD-to CD to-Seven Seven-Segment Segment Converter<br />

Input is a 4-bit 4 bit BCD code 4 inputs (w,<br />

x, y, z).<br />

Output is a 7-bit 7 bit code (a,b,c,d,e,f,g) that<br />

allows for the decimal equivalent to be<br />

displayed.<br />

a<br />

Example:<br />

Input: 0000 BCD<br />

Output: 1111110<br />

(a=b=c=d=e=f=1, g=0)<br />

f g<br />

e<br />

d<br />

c<br />

b

BCD<br />

BCD-to<br />

to-Seven<br />

Seven-Segment (cont.)<br />

Segment (cont.)<br />

Truth Table<br />

Truth Table<br />

11100X0<br />

11100X0<br />

0111<br />

0111<br />

7<br />

X011111<br />

X011111<br />

0110<br />

0110<br />

6<br />

1011011<br />

1011011<br />

0101<br />

0101<br />

5<br />

0110011<br />

0110011<br />

0100<br />

0100<br />

4<br />

1111001<br />

1111001<br />

0011<br />

0011<br />

3<br />

1101101<br />

1101101<br />

0010<br />

0010<br />

2<br />

0110000<br />

0110000<br />

0001<br />

0001<br />

1<br />

1111110<br />

1111110<br />

0000<br />

0000<br />

0<br />

abcdefg<br />

abcdefg<br />

wxyz<br />

wxyz<br />

Digit<br />

Digit abcdefg<br />

abcdefg<br />

wxyz<br />

wxyz<br />

Digit<br />

Digit<br />

XXXXXXX<br />

XXXXXXX<br />

1111<br />

1111<br />

XXXXXXX<br />

XXXXXXX<br />

1110<br />

1110<br />

XXXXXXX<br />

XXXXXXX<br />

1101<br />

1101<br />

XXXXXXX<br />

XXXXXXX<br />

1100<br />

1100<br />

XXXXXXX<br />

XXXXXXX<br />

1011<br />

1011<br />

XXXXXXX<br />

XXXXXXX<br />

1010<br />

1010<br />

111X011<br />

111X011<br />

1001<br />

1001<br />

9<br />

1111111<br />

1111111<br />

1000<br />

1000<br />

8<br />

??

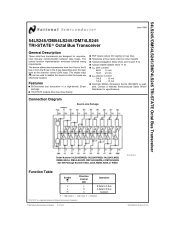

<strong>Decoders</strong><br />

A combinational circuit that converts<br />

binary information from n coded inputs<br />

to a maximum 2 n decoded outputs<br />

n-to to- 2n decoder<br />

n-to to-m decoder, m = 2n Examples: BCD-to BCD to-7-segment segment decoder,<br />

where n=4 and m=7

coders (cont.)

o-4 Decoder

o-4 Active Low Decoder

address<br />

3-to to-8 8 Decoder<br />

data

3-to to-8 8 Decoder (cont.)<br />

Three inputs, A 0, , A 1, , A 2, , are decoded into<br />

eight outputs, D 0 through D 7<br />

Each output D i represents one of the<br />

minterms of the 3 input variables.<br />

Di = 1 when the binary number A 2A1A0 = i<br />

Shorthand: D i = m i<br />

The output variables are<br />

The output variables are mutually exclusive; exclusive;<br />

exactly one output has the value 1 at any time,<br />

and the other seven are 0.

Implementing Boolean functions<br />

using decoders<br />

Any combinational circuit can be constructed<br />

using decoders and OR gates! Why?<br />

Here is an example:<br />

Implement a full adder circuit with a decoder<br />

and two OR gates.<br />

Recall full adder equations, and let X, Y, and Z<br />

be the inputs:<br />

S(X,Y,Z) = X+Y+Z = Sm(1,2,4,7) m(1,2,4,7)<br />

C (X,Y,Z) = Sm(3, m(3, 5, 6, 7).<br />

Since there are 3 inputs and a total of 8<br />

minterms, we need a 3-to 3 to-8 8 decoder.

Implementing a Binary Adder<br />

Using a Decoder<br />

S(X,Y,Z) = Sm(1,2,4,7)<br />

C(X,Y,Z) = Sm(3,5,6,7)

Decoder Expansions<br />

Larger decoders can be constructed using<br />

a number of smaller ones.<br />

-> HIERARCHICAL design!<br />

Example:<br />

A 6-to-64 decoder can be designed using<br />

four 4-to-16 and one 2-to-4 decoders.<br />

How? (Hint: Use the 2-to-4 decoder to<br />

generate the enable signals to the four 4to-16<br />

decoders).

-to to-8 8 decoder using two 2-to 2 to-4 4 decoders

4-input input tree decoder

Encoders<br />

An encoder is a digital circuit that<br />

performs the inverse operation of a<br />

decoder. An encoder has 2 n input lines<br />

and n output lines.<br />

The output lines generate the binary<br />

equivalent of the input line whose value<br />

is 1.

Encoders (cont.)

Encoder Example<br />

Example: 8-to 8 to-3 3 binary encoder (octal-to (octal to-binary) binary)<br />

A 0 = D 1 + D 3 + D 5 + D 7<br />

A 1 = D 2 + D 3 + D 6 + D 7<br />

A 2 = D 4 + D 5 + D 6 + D 7

Encoder Example (cont.)

Simple Encoder Design Issues<br />

There are two ambiguities associated with<br />

the design of a simple encoder:<br />

1. Only one input can be active at any given time. If<br />

two inputs are active simultaneously, the output<br />

produces an undefined combination (for example,<br />

if D 3 and D 6 are 1 simultaneously, the output of<br />

the encoder will be 111.<br />

2. An output with all 0's can be generated when all<br />

the inputs are 0's,or when D 0 is equal to 1.

Priority Encoders<br />

Solves the ambiguities mentioned above.<br />

Multiple asserted inputs are allowed;<br />

one has priority over all others.<br />

Separate indication of no asserted<br />

inputs.

Example: 4-to 4 to-2 2 Priority Encoder<br />

Truth Table

-to to-2 2 Priority Encoder (cont.)<br />

The operation of the priority encoder is<br />

such that:<br />

If two or more inputs are equal to 1 at<br />

the same time, the input in the highest-<br />

numbered position will take precedence.<br />

A valid output indicator, indicator,<br />

designated by<br />

V, is set to 1 only when one or more<br />

inputs are equal to 1. V = D 3 + D 2 + D 1 +<br />

D0 by inspection.

Example: 4-to 4 to-2 2 Priority Encoder<br />

K-Maps Maps

Example: 4-to 4 to-2 2 Priority Encoder<br />

Logic Diagram

8-to to-3 3 Priority Encoder

Matrix of switches = Keypad<br />

C0 C1 C2 C3<br />

1 2 3 F<br />

4 5 6 E<br />

7 8 9 D<br />

0 A B C<br />

R0<br />

R1<br />

R2<br />

R3

Keypad Decoder IC - Encoder<br />

1 2 3 F<br />

4 5 6 E<br />

7 8 9 D<br />

0 A B C<br />

COL.<br />

4-bit<br />

ROW<br />

4-bit<br />

4-bit<br />

Binary<br />

(encoded

Priority Interrupt Encoder<br />

Interrupting<br />

Devices<br />

Device A<br />

Device B<br />

Device C<br />

Device D<br />

Schematic<br />

Interrupt<br />

Encoder<br />

Req(1:0)<br />

IntRq<br />

Microprocessor

Priority Encoding - Interrupt<br />

Interrupting Device<br />

A B C D<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

1<br />

0<br />

0<br />

1<br />

1<br />

0<br />

Requests<br />

0<br />

1<br />

0<br />

1<br />

0<br />

Req (1:0)<br />

0 0<br />

0 0<br />

0 1<br />

0 1<br />

1 0<br />

IntRq<br />

0<br />

Exercise: Complete this table?<br />

1<br />

1<br />

1<br />

1