RANGKAIAN LOGIKA

RANGKAIAN LOGIKA

RANGKAIAN LOGIKA

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

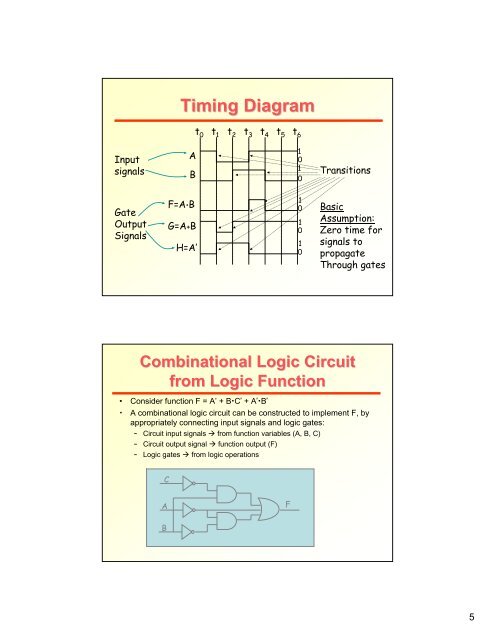

Input<br />

signals<br />

Gate<br />

Output<br />

Signals<br />

Timing Diagram<br />

A<br />

B<br />

F=A•B<br />

G=A+B<br />

H=A’<br />

t 0 t 1 t 2 t 3 t 4 t 5 t 6<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

Transitions<br />

Basic<br />

Assumption:<br />

Zero time for<br />

signals to<br />

propagate<br />

Through gates<br />

Combinational Logic Circuit<br />

from Logic Function<br />

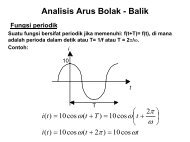

• Consider function F = A’ + B•C’ + A’•B’<br />

• A combinational logic circuit can be constructed to implement F, by<br />

appropriately connecting input signals and logic gates:<br />

– Circuit input signals from function variables (A, B, C)<br />

– Circuit output signal function output (F)<br />

– Logic gates from logic operations<br />

C<br />

A<br />

B<br />

F<br />

5