Towards a Power and Energy Efficient Use of Partial Dynamic ...

Towards a Power and Energy Efficient Use of Partial Dynamic ...

Towards a Power and Energy Efficient Use of Partial Dynamic ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

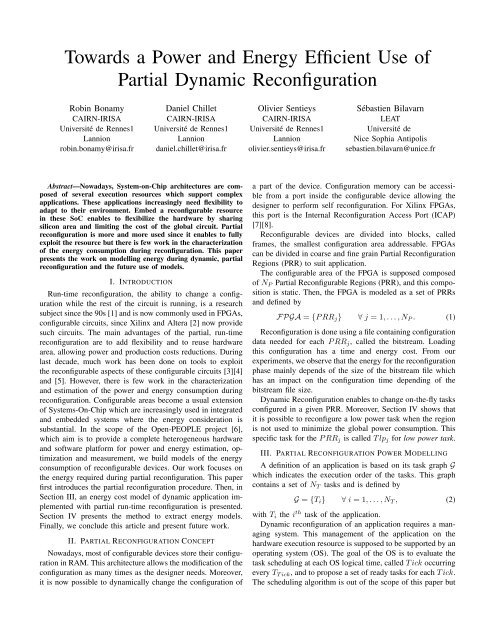

<strong>Towards</strong> a <strong>Power</strong> <strong>and</strong> <strong>Energy</strong> <strong>Efficient</strong> <strong>Use</strong> <strong>of</strong><br />

<strong>Partial</strong> <strong>Dynamic</strong> Reconfiguration<br />

Robin Bonamy<br />

CAIRN-IRISA<br />

Université de Rennes1<br />

Lannion<br />

robin.bonamy@irisa.fr<br />

Daniel Chillet<br />

CAIRN-IRISA<br />

Université de Rennes1<br />

Lannion<br />

daniel.chillet@irisa.fr<br />

Olivier Sentieys<br />

CAIRN-IRISA<br />

Université de Rennes1<br />

Lannion<br />

olivier.sentieys@irisa.fr<br />

Sébastien Bilavarn<br />

LEAT<br />

Université de<br />

Nice Sophia Antipolis<br />

sebastien.bilavarn@unice.fr<br />

Abstract—Nowadays, System-on-Chip architectures are composed<br />

<strong>of</strong> several execution resources which support complex<br />

applications. These applications increasingly need flexibility to<br />

adapt to their environment. Embed a reconfigurable resource<br />

in these SoC enables to flexibilize the hardware by sharing<br />

silicon area <strong>and</strong> limiting the cost <strong>of</strong> the global circuit. <strong>Partial</strong><br />

reconfiguration is more <strong>and</strong> more used since it enables to fully<br />

exploit the resource but there is few work in the characterization<br />

<strong>of</strong> the energy consumption during reconfiguration. This paper<br />

presents the work on modelling energy during dynamic, partial<br />

reconfiguration <strong>and</strong> the future use <strong>of</strong> models.<br />

I. INTRODUCTION<br />

Run-time reconfiguration, the ability to change a configuration<br />

while the rest <strong>of</strong> the circuit is running, is a research<br />

subject since the 90s [1] <strong>and</strong> is now commonly used in FPGAs,<br />

configurable circuits, since Xilinx <strong>and</strong> Altera [2] now provide<br />

such circuits. The main advantages <strong>of</strong> the partial, run-time<br />

reconfiguration are to add flexibility <strong>and</strong> to reuse hardware<br />

area, allowing power <strong>and</strong> production costs reductions. During<br />

last decade, much work has been done on tools to exploit<br />

the reconfigurable aspects <strong>of</strong> these configurable circuits [3][4]<br />

<strong>and</strong> [5]. However, there is few work in the characterization<br />

<strong>and</strong> estimation <strong>of</strong> the power <strong>and</strong> energy consumption during<br />

reconfiguration. Configurable areas become a usual extension<br />

<strong>of</strong> Systems-On-Chip which are increasingly used in integrated<br />

<strong>and</strong> embedded systems where the energy consideration is<br />

substantial. In the scope <strong>of</strong> the Open-PEOPLE project [6],<br />

which aim is to provide a complete heterogeneous hardware<br />

<strong>and</strong> s<strong>of</strong>tware platform for power <strong>and</strong> energy estimation, optimization<br />

<strong>and</strong> measurement, we build models <strong>of</strong> the energy<br />

consumption <strong>of</strong> reconfigurable devices. Our work focuses on<br />

the energy required during partial reconfiguration. This paper<br />

first introduces the partial reconfiguration procedure. Then, in<br />

Section III, an energy cost model <strong>of</strong> dynamic application implemented<br />

with partial run-time reconfiguration is presented.<br />

Section IV presents the method to extract energy models.<br />

Finally, we conclude this article <strong>and</strong> present future work.<br />

II. PARTIAL RECONFIGURATION CONCEPT<br />

Nowadays, most <strong>of</strong> configurable devices store their configuration<br />

in RAM. This architecture allows the modification <strong>of</strong> the<br />

configuration as many times as the designer needs. Moreover,<br />

it is now possible to dynamically change the configuration <strong>of</strong><br />

a part <strong>of</strong> the device. Configuration memory can be accessible<br />

from a port inside the configurable device allowing the<br />

designer to perform self reconfiguration. For Xilinx FPGAs,<br />

this port is the Internal Reconfiguration Access Port (ICAP)<br />

[7][8].<br />

Reconfigurable devices are divided into blocks, called<br />

frames, the smallest configuration area addressable. FPGAs<br />

can be divided in coarse <strong>and</strong> fine grain <strong>Partial</strong> Reconfiguration<br />

Regions (PRR) to suit application.<br />

The configurable area <strong>of</strong> the FPGA is supposed composed<br />

<strong>of</strong> N P <strong>Partial</strong> Reconfigurable Regions (PRR), <strong>and</strong> this composition<br />

is static. Then, the FPGA is modeled as a set <strong>of</strong> PRRs<br />

<strong>and</strong> defined by<br />

FPGA = {P RR j } ∀ j = 1, . . . , N P . (1)<br />

Reconfiguration is done using a file containing configuration<br />

data needed for each P RR j , called the bitstream. Loading<br />

this configuration has a time <strong>and</strong> energy cost. From our<br />

experiments, we observe that the energy for the reconfiguration<br />

phase mainly depends <strong>of</strong> the size <strong>of</strong> the bitstream file which<br />

has an impact on the configuration time depending <strong>of</strong> the<br />

bitstream file size.<br />

<strong>Dynamic</strong> Reconfiguration enables to change on-the-fly tasks<br />

configured in a given PRR. Moreover, Section IV shows that<br />

it is possible to reconfigure a low power task when the region<br />

is not used to minimize the global power consumption. This<br />

specific task for the P RR j is called T lp j for low power task.<br />

III. PARTIAL RECONFIGURATION POWER MODELLING<br />

A definition <strong>of</strong> an application is based on its task graph G<br />

which indicates the execution order <strong>of</strong> the tasks. This graph<br />

contains a set <strong>of</strong> N T tasks <strong>and</strong> is defined by<br />

G = {T i } ∀ i = 1, . . . , N T , (2)<br />

with T i the i th task <strong>of</strong> the application.<br />

<strong>Dynamic</strong> reconfiguration <strong>of</strong> an application requires a managing<br />

system. This management <strong>of</strong> the application on the<br />

hardware execution resource is supposed to be supported by an<br />

operating system (OS). The goal <strong>of</strong> the OS is to evaluate the<br />

task scheduling at each OS logical time, called T ick occurring<br />

every T T ick , <strong>and</strong> to propose a set <strong>of</strong> ready tasks for each T ick.<br />

The scheduling algorithm is out <strong>of</strong> the scope <strong>of</strong> this paper but

we consider that the scheduler produces a valid list <strong>of</strong> ready<br />

tasks for each T ick.<br />

The execution time <strong>of</strong> each task T i depends on its instantiation,<br />

<strong>and</strong> is defined by the variable C i,j (t) for task<br />

T i instantiated in P RR j . This variable is decreased by the<br />

scheduler at each cycle if the task T i is included in the set<br />

<strong>of</strong> read tasks at the current T ick. The power consumption <strong>of</strong><br />

each task T i is also dependent from its instantiation, <strong>and</strong> is<br />

defined by the variable P i,j for task T i instantiated in P RR j .<br />

The time <strong>and</strong> the power to configure a specific task T i<br />

depend on the bitstream size <strong>of</strong> this task which depends on<br />

the PRR size selected for the task. These time <strong>and</strong> power for<br />

uploading the bitstream in the configuration memory are given<br />

by the variables T u prrj <strong>and</strong> P u prrj for the P RR j .<br />

From these definitions, we propose to model the optimization<br />

problem through the minimization <strong>of</strong> an energy expression<br />

<strong>of</strong> the global system. The goal <strong>of</strong> the optimization is to<br />

compute the task configurations which limit the power consumption<br />

<strong>of</strong> the system at each T ick. These task instantiations<br />

are defined though the variable X i,j (t) which is equal to 1 if<br />

the task T i is instantiated on P RR j at time T ick = t, or equal<br />

to 0 otherwise. Due to the OS behavior, i.e. new schedule<br />

computed at each T ick, the optimization problem must be<br />

solved at each T ick. At each T ick, the OS knows which tasks<br />

are configured on which P RR. So the OS knows the values<br />

<strong>of</strong> variable X i,j (t − 1), <strong>and</strong> then the power consumption is<br />

known before the new scheduling. This power consumption<br />

related to this T ick are the power consumed by task already<br />

implemented, P T A (t, j), by low power tasks, P T lp (t, j), by<br />

reconfiguration <strong>of</strong> new tasks, P P R (t, j) <strong>and</strong> the power consumed<br />

by newly implemented tasks, once reconfiguration is<br />

finished, P NT (t, j) for each P RR j . These power pr<strong>of</strong>iles are<br />

defined in the following equations:<br />

∑N T<br />

P T A (t, j) = (1 − (X i,j (t) − (X i,j (t − 1))) × P i,j<br />

i=1<br />

N T<br />

∑<br />

P T lp (t, j) = (1 − X i,j (t)) × P T lp,j<br />

i=1<br />

N T<br />

∑<br />

P P R (t, j) = | (1 − (X i,j (t) − X i,j (t − 1))) | × P u prrj<br />

i=1<br />

N T<br />

∑<br />

P NT (t, j) = (1 − (X i,j (t) − (X i,j (t − 1))) × P i,j (3)<br />

i=1<br />

With these expressions <strong>of</strong> the power consumption, the<br />

energy consumption during one T ick is given by:<br />

E T ick (t) =<br />

∑N P<br />

j=1<br />

P T A (t, j) × T T ick<br />

+ P T lp (t, j) × T T ick<br />

+ P P R (t, j) × T uprrj<br />

+ P NT (t, j) × (T T ick − T uprrj ). (4)<br />

From this expression, the optimization problem must compute<br />

the X i,j values for the new T ick according to G <strong>and</strong><br />

C i,j (t). These new values lead to reduce the energy which<br />

will be consumed between the current T ick (t) <strong>and</strong> the next<br />

T ick (t + 1).<br />

IV. POWER MEASURES<br />

In order to build power consumption models <strong>and</strong> to validate<br />

the previously presented approach, real measures <strong>of</strong> the energy<br />

<strong>of</strong> dynamic reconfiguration are needed. We implemented an<br />

application similar to the one proposed in [9] in a Virtex-<br />

5. Figure 1 presents the power consumption obtained while<br />

reconfiguring a P RR j for a T i to T lp j . This figure shows<br />

that there is an important reduction <strong>of</strong> the power consumption,<br />

in this case, power is reduced by 25 mW . This confirms the<br />

advantage to use <strong>Partial</strong> Reconfiguration (PR) <strong>and</strong> low power<br />

tasks to reduce global energy consumption.<br />

Fig. 1. <strong>Power</strong> consumption <strong>of</strong> a Virtex-5 during the reconfiguration <strong>of</strong> a<br />

PRR from a Task to a low power task versus time.<br />

V. CONCLUSION<br />

This paper has presented our work on power <strong>and</strong> energy<br />

characterization <strong>of</strong> partial reconfiguration. The measures realized<br />

confirm the potential <strong>of</strong> reconfiguration to reduce energy<br />

consumption <strong>and</strong> the lack <strong>of</strong> tools to estimate <strong>and</strong> optimize the<br />

use <strong>of</strong> this feature. Our future work will focus on continuing<br />

building energy consumption models on other platforms with<br />

different reconfiguration flows <strong>and</strong> energy optimization with<br />

these models <strong>and</strong> a validation on a real application.<br />

ACKNOWLEDGMENT<br />

The authors would like to thank the French National Agency<br />

for the support <strong>of</strong> this work in the scope <strong>of</strong> the OpenPEOPLE<br />

project.<br />

REFERENCES<br />

[1] P. Lysaght <strong>and</strong> J. Dunlop, <strong>Dynamic</strong> reconfiguration <strong>of</strong> FPGAs in Selected<br />

papers from the Oxford 1993 international workshop on field<br />

programmable logic <strong>and</strong> applications on More FPGAs pp.82-94, Oxford,<br />

1994<br />

[2] Altera Corporation, Increasing Design Functionality with <strong>Partial</strong> <strong>and</strong><br />

<strong>Dynamic</strong> Reconfiguration in 28-nm FPGAs. White paper, 2010.<br />

[3] V. Tadigotla, L. Sliger, S. Commuri, FPGA Implementation <strong>of</strong> <strong>Dynamic</strong><br />

Run-Time Behavior Reconfiguration in Robots in Proceedings <strong>of</strong> the 2006<br />

IEEE International Symposium on Intelligent Control, Munich, Germany.<br />

pp.1220-1225.<br />

[4] L. Sterpone, D. Matos, L. Carro, S. Wong, F. Anjam A New Reconfigurable<br />

Clock-gating Technique for Low <strong>Power</strong> SRAM-based FPGAs at<br />

DATE2011: IEEE Design, Automation <strong>and</strong> Test in Europe, Grenoble,<br />

France, 2011<br />

[5] M. Rullmann <strong>and</strong> R. Merker, A Cost Model for <strong>Partial</strong> <strong>Dynamic</strong> Reconfiguration<br />

in Transactions on HiPEAC: Vol.4, 2009<br />

[6] Open-PEOPLE - Open-<strong>Power</strong> <strong>and</strong> <strong>Energy</strong> Optimization PLatform <strong>and</strong><br />

Estimator, http://www.open-people.fr/<br />

[7] Alfke, P. (Xilinx Inc.). Application note: <strong>Dynamic</strong> Reconfiguration, 1997.<br />

[8] Xilinx Inc. Xilinx Virtex-II Pro <strong>and</strong> Virtex-II Pro X Platform FPGA <strong>Use</strong>r<br />

Guide, 2002.<br />

[9] Xilinx Inc. UG744, PlanAhead S<strong>of</strong>tware Tutorial: <strong>Partial</strong> Reconfiguration<br />

<strong>of</strong> a Processor Peripheral