Ethernet Technology

Ethernet Technology

Ethernet Technology

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

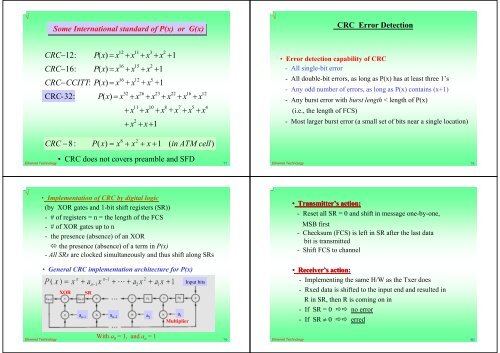

Some International standard of of P(x) or or G(x)<br />

<br />

CRC Error Detection<br />

CRC12:<br />

CRC16:<br />

CRCCCITT:<br />

CRC-32:<br />

P(<br />

x)<br />

x<br />

P(<br />

x)<br />

x<br />

P(<br />

x)<br />

x<br />

12<br />

16<br />

16<br />

P(<br />

x)<br />

x<br />

x<br />

x<br />

+ x<br />

32<br />

x<br />

x<br />

11<br />

15<br />

12<br />

x<br />

11<br />

2<br />

x<br />

+ x<br />

26<br />

x<br />

3<br />

x<br />

2<br />

5<br />

x<br />

10<br />

x<br />

x1<br />

1<br />

+1<br />

23<br />

2<br />

x<br />

8<br />

1<br />

x<br />

22<br />

+ x<br />

x<br />

7<br />

16<br />

x<br />

x<br />

5<br />

12<br />

x<br />

4<br />

• Error detection capability of CRC<br />

- All single-bit error<br />

- All double-bit errors, as long as P(x) has at least three 1’s<br />

- Any odd number of errors, as long as P(x) contains (x+1)<br />

- Any burst error with burst length < length of P(x)<br />

(i.e., the length of FCS)<br />

- Most larger burst error (a small set of bits near a single location)<br />

CRC P x x x x in ATM cell<br />

8 2<br />

8: ( ) 1 ( )<br />

• CRC does not covers preamble and SFD<br />

<strong>Ethernet</strong> <strong>Technology</strong> 77<br />

<strong>Ethernet</strong> <strong>Technology</strong> 78<br />

<br />

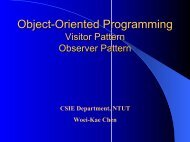

• Implementation of CRC by digital logic<br />

(by XOR gates and 1-bit shift registers (SR))<br />

- # of registers = n = the length of the FCS<br />

- # of XOR gates up to n<br />

- the presence (absence) of an XOR<br />

the presence (absence) of a term in P(x)<br />

- All SRs are clocked simultaneously and thus shift along SRs<br />

• General CRC implementation architecture for P(x)<br />

<br />

<br />

<br />

<br />

<br />

XOR<br />

<br />

<br />

Input bits<br />

SR<br />

a a a n-1<br />

a n-2 2<br />

1<br />

Multiplier<br />

• Transmitter’s s action:<br />

- Reset all SR = 0 and shift in message one-by-one,<br />

MSB first<br />

- Checksum (FCS) is left in SR after the last data<br />

bit is transmitted<br />

- Shift FCS to channel<br />

• Receiver’s s action:<br />

- Implementing the same H/W as the Txer does<br />

- Rxed data is shifted to the input end and resulted in<br />

R in SR, then R is coming on in<br />

- If SR = 0 no error<br />

-If SR 0 erred<br />

With a 0 = 1, and a n = 1<br />

<strong>Ethernet</strong> <strong>Technology</strong> 79<br />

<strong>Ethernet</strong> <strong>Technology</strong> 80