LAB3 - Suraj @ LUMS

LAB3 - Suraj @ LUMS

LAB3 - Suraj @ LUMS

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

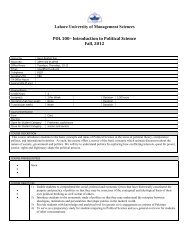

CS 523 Advanced Computer Architecture<br />

LAB 3<br />

(Due Date: April 21, 2006)<br />

1. Introduction<br />

The aim of this lab is to familiarize students with the SimpleScalar simulation tool set.<br />

After a brief introduction of the tool set, an experiment will be performed to get a feel of<br />

the working of simulator. The experiment will record miss rate of a single processor for<br />

various cache configurations.<br />

2. SimpleScalar Tool Set<br />

The tool set contains several simulators, each of them oriented toward a specific type of<br />

analysis:<br />

• sim-safe: minimal SimpleScalar functional simulator<br />

• sim-fast: fast (optimized sim-safe) SimpleScalar functional simulator<br />

• sim-profile: program profiling simulator<br />

• sim-cache: multi-level cache simulator<br />

• sim-cheetah: multi-configuration cache simulator<br />

• sim-outorder: the most complex and detailed SimpleScalar simulator in the tool<br />

set<br />

All these programs help you simulate the hardware, the SimpleScalar architecture. For<br />

details about each individual simulator please refer to Todd Austin’s SimpleScalar<br />

hacker’s guide (www.simplescalar.com/docs/hack_guide_v2.pdf ). All these programs can<br />

be found under the directory /home/SimpleScalar03/simple-sim3.0/ at the EDA machine<br />

server.

3. Pre-Lab<br />

The EDA machine at RICE lab will act as a server for this lab. You will login to the<br />

machine remotely using “PUTTY” telnet client. Course Web site has an internet link<br />

from where you can download PUTTY. IP address of EDA machine is 172.28.6.88.<br />

Every student will login with the login ID of the format “aastudentID”. For instance a<br />

student with ID 2005-06-007 will login as aa05060007. Initially the password has been<br />

set same as the student ID. But we strongly recommend you to change this first time you<br />

log in using the command passwd. You have to set up the PATH variable to refer to<br />

directories where SimpleScalar tools are located. To set the PATH give the following<br />

command.<br />

$export PATH=$PATH:/home/SimpleScalar03/simplesim-3.0/.<br />

First ‘$’ represents your command prompt.<br />

4. Cache Simulator<br />

In this lab we will use the multilevel cache simulator sim-cache. The commands to simcache<br />

are given through a configuration file. In order to learn about the cache simulator<br />

itself type<br />

$ sim-cache<br />

Study the output of the above command very carefully, as it clearly explains options and<br />

arguments used while writing a configuration file. Specifically note the format of<br />

specifying a cache configuration. A five colon separated fields<br />

name:sets:block_size:associativity:replacement_method. For instance a 32 kilobyte<br />

level 1 data cache with 32 byte blocks, an associativity of 4 and least recently used<br />

policy is specified as dl1:256:32:4:1, as 256 sets of four 32 byte blocks each have a total<br />

capacity of 32 Kbytes.

You will be modifying the configuration file to get different parameters of a simulated<br />

cache. In order to get a sample configuration file type<br />

$ ./sim-cache –dumpconfig myconfig<br />

There are two ways two evaluate performance of a functional cache simulator. One<br />

way is to use some benchmark programs and obtain the statistics of a cache design<br />

and the other way is develop own code to exploit properties of a design. In this lab we<br />

will go with the first method. SPEC95 bench mark programs are located under the<br />

directory /home/SimpleScalar03/Spec95/. We will use the ijpeg.ss binary to simulate<br />

performance of cache. The command is:<br />

$sim-cache –config myconfig /home/SimpleScalar03/spec95-little/ijpeg.ss<br />

A whole bunch of information will be displayed. There are cache statistics with default<br />

configuration. We will be focusing on the dl1.miss_rate parameter.<br />

4.1 Assignment<br />

In this experiment we will assume no L2 instruction or data caches. In the configuration<br />

file use the following configuration for L1 instruction cache.<br />

-cache:il1 il1:512:32 :1:1<br />

Also to disable any TLB for either instruction or data do this<br />

-cache: dl2<br />

-cache:il2<br />

-tlb:itlb<br />

-tlb:dtlb<br />

none<br />

none<br />

none<br />

none

Use sim-cache to simulate the performance (miss rate) of the cache under the following<br />

conditions:<br />

a) Vary the number of sets in level 1 data cache from 1 to 1024 in powers of 4 while<br />

keeping the block size at 32 bytes, the associativity at 4 and the algorithm as least<br />

recently used. Comment on the effects of increasing the cache size on program<br />

execution and recommend a size for this particular application. Plot Miss Rate<br />

versus cache size.<br />

b) Change the associativity of the level 1 data cache from 1 to 32 in powers of 2<br />

while keeping the same block size and replacement policy as before. Keep the<br />

total size of the data cache fixed at 8192 bytes. What can you say about the effects<br />

of assosiativity on the effectiveness of the cache. Generate a plot to verify your<br />

answer.<br />

c) Adjust the block size of the level 1 data cache (8 bytes, 32 bytes, 128 bytes, 512<br />

bytes, 2048 bytes) while preserving the same assosiativity, replacement policy and total<br />

cache capacity. Why does performance degrade for small block sizes. Again generate an<br />

appropriate plot.