The Haystack 2nd generation digitalâbackend system - CIRA

The Haystack 2nd generation digitalâbackend system - CIRA

The Haystack 2nd generation digitalâbackend system - CIRA

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

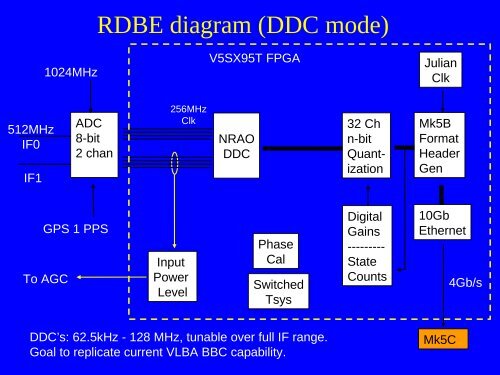

RDBE diagram (DDC mode)<br />

1024MHz<br />

V5SX95T FPGA<br />

Julian<br />

Clk<br />

512MHz<br />

IF0<br />

IF1<br />

ADC<br />

8-bit<br />

2 chan<br />

256MHz<br />

Clk<br />

NRAO<br />

DDC<br />

32 Ch<br />

n-bit<br />

Quantization<br />

Mk5B<br />

Format<br />

Header<br />

Gen<br />

GPS 1 PPS<br />

To AGC<br />

Input<br />

Power<br />

Level<br />

Phase<br />

Cal<br />

Switched<br />

Tsys<br />

Digital<br />

Gains<br />

---------<br />

State<br />

Counts<br />

10Gb<br />

Ethernet<br />

4Gb/s<br />

DDC’s: 62.5kHz - 128 MHz, tunable over full IF range.<br />

Goal to replicate current VLBA BBC capability.<br />

Mk5C