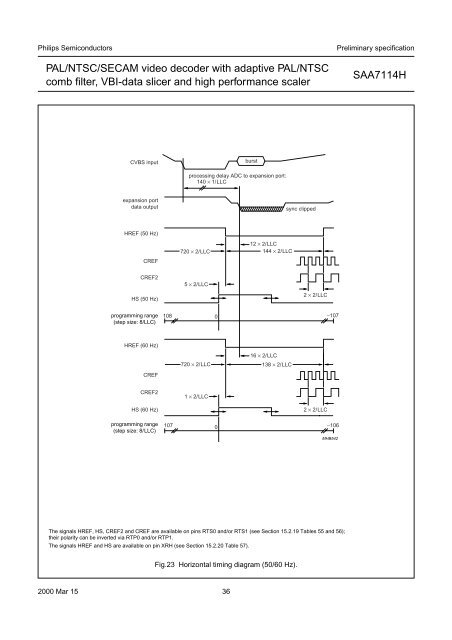

Philips Semiconductors <strong>PAL</strong>/<strong>NTSC</strong>/<strong>SECAM</strong> <strong>video</strong> <strong>decoder</strong> <strong>with</strong> <strong>adaptive</strong> <strong>PAL</strong>/<strong>NTSC</strong> <strong>comb</strong> filter, VBI-data slicer and high performance scaler Preliminary specification SAA7114H handbook, full pagewidth CVBS input burst processing delay ADC to expansion port: 140 × 1/LLC expansion port data output sync clipped HREF (50 Hz) CREF 12 × 2/LLC 720 × 2/LLC 144 × 2/LLC CREF2 HS (50 Hz) 5 × 2/LLC 2 × 2/LLC programming range (step size: 8/LLC) 108 0 −107 HREF (60 Hz) CREF 720 × 2/LLC 16 × 2/LLC 138 × 2/LLC CREF2 1 × 2/LLC HS (60 Hz) programming range (step size: 8/LLC) 2 × 2/LLC 107 0 −106 MHB542 The signals HREF, HS, CREF2 and CREF are available on pins RTS0 and/or RTS1 (see Section 15.2.19 Tables 55 and 56); their polarity can be inverted via RTP0 and/or RTP1. The signals HREF and HS are available on pin XRH (see Section 15.2.20 Table 57). Fig.23 Horizontal timing diagram (50/60 Hz). 2000 Mar 15 36

Philips Semiconductors <strong>PAL</strong>/<strong>NTSC</strong>/<strong>SECAM</strong> <strong>video</strong> <strong>decoder</strong> <strong>with</strong> <strong>adaptive</strong> <strong>PAL</strong>/<strong>NTSC</strong> <strong>comb</strong> filter, VBI-data slicer and high performance scaler Preliminary specification SAA7114H 8.3 Scaler The High Performance <strong>video</strong> Scaler (HPS) is based on the system as implemented in SAA7140, but enhanced in some aspects. Vertical upsampling is supported and the processing pipeline buffer capacity is enhanced, to allow more flexible <strong>video</strong> stream timing at the image port, discontinuous transfers, and handshake. The internal data flow from block to block is discontinuous dynamically, due to the scaling process itself. The flow is controlled by internal data valid and data request flags (internal handshake signalling) between the sub-blocks. Therefore the entire scaler acts as a pipeline buffer. Depending on the actually programmed scaling parameters the effective buffer can exceed to an entire line. The access/bandwidth requirements to the VGA frame buffer are reduced significantly. The high performance <strong>video</strong> scaler in SAA7114H has the following major blocks. • Acquisition control (horizontal and vertical timer) and task handling (the region/field/frame based processing) • Prescaler, for horizontal down-scaling by an integer factor, <strong>comb</strong>ined <strong>with</strong> appropriate band limiting filters, especially anti-aliasing for CIF format • Brightness, saturation, contrast control for scaled output data • Line buffer, <strong>with</strong> asynchronous read and write, to support vertical up-scaling (e.g. for <strong>video</strong>phone application, converting 240 into 288 lines, YUV 4 : 2 : 2) • Vertical scaling, <strong>with</strong> phase accurate Linear Phase Interpolation (LPI) for zoom and down-scale, or phase accurate Accumulation Mode (ACM) for large down-scaling ratios and better alias suppression • Variable Phase Delay (VPD), operates as horizontal phase accurate interpolation for arbitrary non-integer scaling ratios, supporting conversion between square (SQR) and rectangular (CCIR) pixel sampling • Output formatter for scaled YUV 4 : 2 : 2, YUV 4:1:1 and Y only (format also for raw data) • FIFO, 32-bit wide, <strong>with</strong> 64 pixel capacity in YUV formats • Output interface, 8 or 16 (only if extended by H-port) data pins wide, synchronous or asynchronous operation, <strong>with</strong> stream events on discrete pins, or coded in the data stream. The overall H and V zooming (HV_zoom) is restricted by the input/output data rate relations. With a safety margin of 2% for running in and running out, the maximum HV_zoom is equal to: T_input_field – T_v_blanking 0.98 × ------------------------------------------------------------------------------------------------------------------------------------- in_pixel × in_lines × out_cycle_per_pix × T_out_clk For example: 1. Input from <strong>decoder</strong>: 50 Hz, 720 pixel, 288 lines, 16-bit data at 13.5 MHz data rate, 1 cycle per pixel; output: 8-bit data at 27 MHz, 2 cycles per pixel; the maximum HV_zoom is equal to: 20 ms – 24 × 64 µs 0.98 × 720 -------------------------------------------------------- = × 288 × 2 × 37 ns 1.18 2. Input from X-port: 60 Hz, 720 pixel, 240 lines, 8-bit data at 27 MHz data rate (ITU 656), 2 cycles per pixel; output via I + H-port: 16-bit data at 27 MHz clock, 1 cycle per pixel; the maximum HV_zoom is equal to: 16.666 ms 22 64 µs 0.98 × ------------------------------------------------------------- – × = 720 × 240 × 1 × 37 ns 2.34 The <strong>video</strong> scaler receives its input signal from the <strong>video</strong> <strong>decoder</strong> or from the expansion port (X-port). It gets 16-bit YUV 4:2:2 input data at a continuous rate of 13.5 MHz from the <strong>decoder</strong>. Discontinuous data stream can be accepted from the expansion port (X-port), normally 8-bit wide ITU 656 like YUV data, accompanied by a pixel qualifier on XDQ. The input data stream is sorted into two data paths, one for luminance (or raw samples), and one for time multiplexed chrominance U and V samples. An YUV 4:1:1 input format is converted to 4:2:2forthehorizontal prescaling and vertical filter scaling operation. The scaler operation is defined by two programming pages A and B, representing two different tasks, that can be applied field alternating or to define two regions in a field (e.g. <strong>with</strong> different scaling range, factors, and signal source during odd and even fields). Each programming page contains control: • For signal source selection and formats • For task handling and trigger conditions • For input and output acquisition window definition • For H-prescaler, V-scaler and H-phase scaling. 2000 Mar 15 37