PM3393 S/UNI® 1x10GE-XP Single Chip 10 Gigabit Ethernet LAN ...

PM3393 S/UNI® 1x10GE-XP Single Chip 10 Gigabit Ethernet LAN ...

PM3393 S/UNI® 1x10GE-XP Single Chip 10 Gigabit Ethernet LAN ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Advance<br />

<strong>PM3393</strong><br />

S/<strong>UNI®</strong> <strong>1x<strong>10</strong>GE</strong>-<strong>XP</strong><br />

<strong>Single</strong> <strong>Chip</strong> <strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> <strong>LAN</strong> PHY For XAUI-Based Optics<br />

GENERAL DESCRIPTION<br />

• The S/<strong>UNI®</strong>-<strong>1x<strong>10</strong>GE</strong>-<strong>XP</strong> is a highly<br />

integrated single chip <strong>10</strong> <strong>Gigabit</strong><br />

<strong>Ethernet</strong> <strong>LAN</strong> PHY supporting XAUIbased<br />

optical modules. The S/UNI<br />

<strong>1x<strong>10</strong>GE</strong>-<strong>XP</strong> provides a POS-PHY<br />

Level 4 system-side interface and<br />

XAUI line-side interface.<br />

FEATURES<br />

• Implements <strong>10</strong> <strong>Gigabit</strong> <strong>LAN</strong> PHY<br />

according the IEEE 802.3ae standard.<br />

• Provides direct connection to XENPAK<br />

optical modules via a 4-bit by 3.125<br />

Gbit/s IEEE 802.3ae XAUI line-side<br />

interface.<br />

• Provides SATURN® POS-PHY<br />

Level 4 16-bit LVDS System-side<br />

Interface (clocked at 700 MHz<br />

nominal).<br />

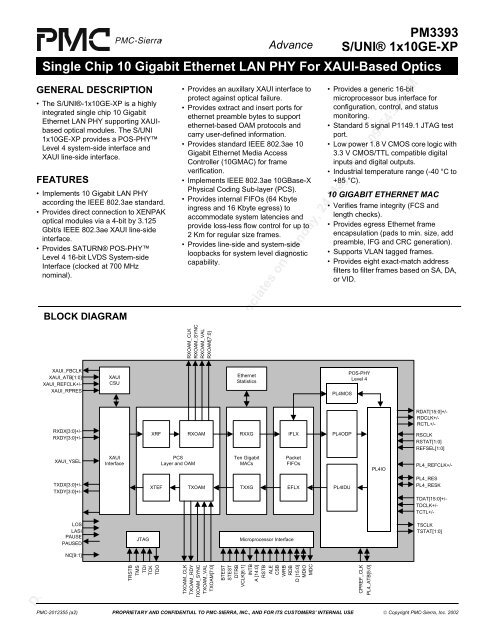

BLOCK DIAGRAM<br />

XAUI_YSEL<br />

XAUI_FBCLK<br />

XAUI_ATB[1:0]<br />

XAUI_REFCLK+/-<br />

XAUI_RPRES<br />

RXDX[3:0]+/-<br />

RXDY[3:0]+/-<br />

TXDX[3:0]+/-<br />

TXDY[3:0]+/-<br />

LOS<br />

LASI<br />

PAUSE<br />

PAUSED<br />

NC[9:1]<br />

XAUI<br />

CSU<br />

XAUI<br />

Interface<br />

JTAG<br />

XRF<br />

XTEF<br />

TRSTB<br />

TMS<br />

TDI<br />

TCK<br />

TDO<br />

PCS<br />

Layer and OAM<br />

• Provides an auxillary XAUI interface to<br />

protect against optical failure.<br />

• Provides extract and insert ports for<br />

ethernet preamble bytes to support<br />

ethernet-based OAM protocols and<br />

carry user-defined information.<br />

• Provides standard IEEE 802.3ae <strong>10</strong><br />

<strong>Gigabit</strong> <strong>Ethernet</strong> Media Access<br />

Controller (<strong>10</strong>GMAC) for frame<br />

verification.<br />

• Implements IEEE 802.3ae <strong>10</strong>GBase-X<br />

Physical Coding Sub-layer (PCS).<br />

• Provides internal FIFOs (64 Kbyte<br />

ingress and 16 Kbyte egress) to<br />

accommodate system latencies and<br />

provide loss-less flow control for up to<br />

2 Km for regular size frames.<br />

• Provides line-side and system-side<br />

loopbacks for system level diagnostic<br />

capability.<br />

RXOAM_CLK<br />

RXOAM_SYNC<br />

RXOAM_VAL<br />

RXOAM[7:0]<br />

RXOAM<br />

TXOAM<br />

TXOAM_CLK<br />

TXOAM_RDY<br />

TXOAM_SYNC<br />

TXOAM_VAL<br />

TXOAM[7:0]<br />

BTEST<br />

STEST<br />

DTRB<br />

VCLK[6:1]<br />

<strong>Ethernet</strong><br />

Statistics<br />

Ten <strong>Gigabit</strong><br />

MACs<br />

• Provides a generic 16-bit<br />

microprocessor bus interface for<br />

configuration, control, and status<br />

monitoring.<br />

• Standard 5 signal P1149.1 JTAG test<br />

port.<br />

• Low power 1.8 V CMOS core logic with<br />

3.3 V CMOS/TTL compatible digital<br />

inputs and digital outputs.<br />

• Industrial temperature range (-40 °C to<br />

+85 °C).<br />

<strong>10</strong> GIGABIT ETHERNET MAC<br />

• Verifies frame integrity (FCS and<br />

length checks).<br />

• Provides egress <strong>Ethernet</strong> frame<br />

encapsulation (pads to min. size, add<br />

preamble, IFG and CRC generation).<br />

• Supports V<strong>LAN</strong> tagged frames.<br />

• Provides eight exact-match address<br />

filters to filter frames based on SA, DA,<br />

or VID.<br />

Downloaded [controlled] by Julie Biorkman of Gillaspy Associates on Monday, 24 May, 20<strong>10</strong> 09:54:24 AM<br />

RXXG<br />

TXXG<br />

PMC-2012355 (a2) PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE © Copyright PMC-Sierra, Inc. 2002<br />

IFLX<br />

Packet<br />

FIFOs<br />

EFLX<br />

Microprocessor Interface<br />

INTB<br />

A [14:0]<br />

RSTB<br />

ALE<br />

CSB<br />

WRB<br />

RDB<br />

D [15:0]<br />

MDIO<br />

MDC<br />

PL4MOS<br />

PL4ODP<br />

PL4IDU<br />

POS-PHY<br />

Level 4<br />

CPREF_CLK<br />

PL4_ATB[5:0]<br />

PL4IO<br />

RSCLK<br />

RSTAT[1:0]<br />

REFSEL[1:0]<br />

TDAT[15:0]+/-<br />

TDCLK+/-<br />

TCTL+/-<br />

RDAT[15:0]+/-<br />

RDCLK+/-<br />

RCTL+/-<br />

PL4_REFCLK+/-<br />

PL4_RES<br />

PL4_RESK<br />

TSCLK<br />

TSTAT[1:0]

Advance <strong>PM3393</strong> S/<strong>UNI®</strong> <strong>1x<strong>10</strong>GE</strong>-<strong>XP</strong><br />

<strong>Single</strong> <strong>Chip</strong> <strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> <strong>LAN</strong> PHY For XAUI-Based Optics<br />

• Provides 64-bin hash based algorithm<br />

to filter multicast addresses.<br />

• Minimum frame size of 64 bytes.<br />

• Provides statistics counters to support<br />

RMON/SNMP.<br />

• Supports jumbo frames up to 9.6<br />

Kbytes.<br />

• Programmable inter-packet gap (IPG).<br />

• Implements in-band PAUSE flowcontrol<br />

and provides support for out-ofband<br />

flow control.<br />

• Upper layer device can flow-control<br />

using dedicated pins or host signaling<br />

to cause generation of a PAUSE<br />

frame.<br />

DEVICE INTERWORKING<br />

• Other PMC-Sierra devices that<br />

implement the POS-PHY Level 4<br />

interface include:<br />

TYPICAL APPLICATION<br />

Head Office:<br />

PMC-Sierra, Inc.<br />

8555 Baxter Place<br />

Burnaby, B.C. V5A 4V7<br />

Canada<br />

Tel: +1.604.415.6000<br />

Fax: +1.604.415.6200<br />

• S/UNI <strong>1x<strong>10</strong>GE</strong>.<br />

• S/UNI 9953.<br />

• S/UNI 9953-POS.<br />

• S/UNI <strong>10</strong>xGE.<br />

POS-PHY LEVEL 4 INTERFACE<br />

• Designed to transmit cells, packets or<br />

frames between physical and data-link<br />

layer devices.<br />

• Requires less pins and draws less<br />

power than other <strong>10</strong> <strong>Gigabit</strong> interface<br />

options.<br />

• Compliant with the following<br />

standards:<br />

• Optical Internetworking Forum -<br />

System Physical Interface Level 4<br />

Phase 2 (SPI-4 P2 and associated<br />

specification OIF-SPI4.02.0).<br />

To order documentation,<br />

send email to:<br />

document@pmc-sierra.com<br />

or contact the head office,<br />

Attn: Document Coordinator<br />

All product documentation is available<br />

on our web site at:<br />

http://www.pmc-sierra.com<br />

For corporate information,<br />

send email to:<br />

info@pmc-sierra.com<br />

PMC-2012355 (a2)<br />

© Copyright PMC-Sierra,<br />

Inc. 2002. All rights reserved.<br />

SATURN and S/UNI are<br />

registered trademarks and<br />

POS-PHY and PMC-Sierra<br />

are trademarks of PMC-<br />

Sierra, Inc.<br />

Downloaded [controlled] by Julie Biorkman of Gillaspy Associates on Monday, 24 May, 20<strong>10</strong> 09:54:24 AM<br />

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS’ INTERNAL USE<br />

• SATURN® POS-PHY Level 4,<br />

Issue 6, March 2001.<br />

APPLICATIONS<br />

<strong>10</strong> GIGABIT ETHERNET SWITCH/ROUTER PORT CARD APPLICATIONS<br />

4 X OC-48 POS Line Card<br />

Optics<br />

Optics<br />

Optics<br />

Optics<br />

(Protect Mate)<br />

CRSU<br />

4x2488<br />

S/UNI<br />

9953<br />

IP Processor<br />

1 X OC-192 POS/<strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> <strong>LAN</strong> & WAN<br />

Line Card<br />

Integrated<br />

Optics<br />

Integrated<br />

Optics<br />

1 X OC-192 POS/<strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> <strong>LAN</strong> & WAN<br />

Line Card<br />

SFI-4<br />

XSBI<br />

SFI-4<br />

XSBI<br />

S/UNI<br />

9953<br />

S/UNI<br />

9953<br />

APS Port<br />

APS Port<br />

L2/L3<br />

Processor<br />

L2/L3<br />

Processor<br />

Traffic<br />

Manager<br />

Traffic<br />

Manager<br />

Traffic<br />

Manager<br />

TT1<br />

Multi-Gbit/s<br />

to Terabit<br />

Switch<br />

Fabric<br />

• Edge and Core Routers.<br />

• Multi-Service (Multi-Protocol)<br />

Switches.<br />

• Internet POP and Transport POP L2<br />

<strong>Ethernet</strong> Switches.<br />

• Data cards for Multi-service<br />

Provisioning Platforms<br />

• Optical cross-connects.<br />

• <strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> Enterprise<br />

Switches with XENPAK uplinks.<br />

• <strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> test equipment.<br />

Traffic<br />

S/UNI<br />

Manager IP Processor <strong>10</strong>x<br />

<strong>10</strong>xGE<br />

Traffic<br />

Manager<br />

<strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> XAUI Based <strong>LAN</strong> PHY Line Card<br />

Traffic<br />

Manager<br />

L2/L3<br />

Processor<br />

L2/L3<br />

Processor<br />

<strong>10</strong> x <strong>Gigabit</strong> <strong>Ethernet</strong> Line Card<br />

S/UNI<br />

<strong>1x<strong>10</strong>GE</strong>-<strong>XP</strong><br />

XAUI<br />

Optics<br />

Optics<br />

<strong>10</strong> <strong>Gigabit</strong> <strong>Ethernet</strong> <strong>LAN</strong> Line Card<br />

S/UNI<br />

<strong>1x<strong>10</strong>GE</strong><br />

XSBI<br />

200/300<br />

MSA<br />

Optics<br />

XENPAK<br />

Optics

![Architecture, Engineering, and Related Services [NAICS 5413]](https://img.yumpu.com/34014793/1/190x245/architecture-engineering-and-related-services-naics-5413.jpg?quality=85)