Hardware Design of Independent Experimental Platform ... - GSE

Hardware Design of Independent Experimental Platform ... - GSE

Hardware Design of Independent Experimental Platform ... - GSE

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

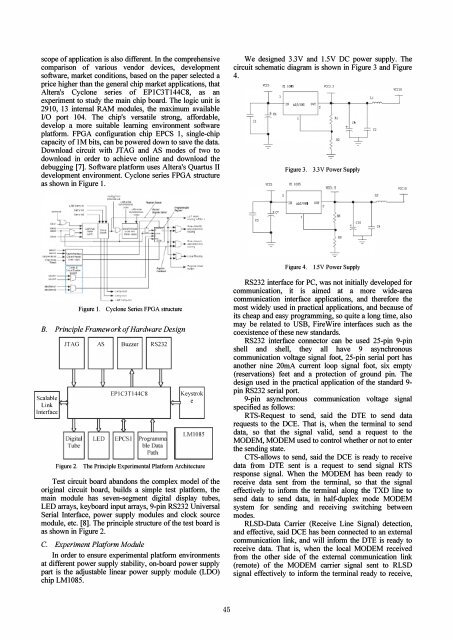

scope <strong>of</strong> application is also different. In the comprehensive<br />

comparison <strong>of</strong> various vendor devices, development<br />

s<strong>of</strong>tware, market conditions, based on the paper selected a<br />

price higher than the general chip market applications, that<br />

Altera's Cyclone series <strong>of</strong> EPIC3T144C8, as an<br />

experiment to study the main chip board. The logic unit is<br />

2910, 13 internal RAM modules, the maximum available<br />

110 port 104. The chip's versatile strong, affordable,<br />

develop a more suitable learning environment s<strong>of</strong>tware<br />

platform. FPGA configuration chip EPCS 1, single-chip<br />

capacity <strong>of</strong> 1M bits, can be powered down to save the data.<br />

Download circuit with JT AG and AS modes <strong>of</strong> two to<br />

download in order to achieve online and download the<br />

debugging [7]. S<strong>of</strong>tware platform uses Altera's Quartus II<br />

development environment. Cyclone series FPGA structure<br />

as shown in Figure 1.<br />

We designed 3.3V and 1.5V DC power supply. The<br />

circuit schematic diagram is shown in Figure 3 and Figure<br />

4.<br />

1 -::+e5<br />

vees<br />

--<br />

Lf<br />

---.L<br />

-=-<br />

3<br />

UI 1085<br />

IN<br />

ADJ!GND<br />

I<br />

I<br />

Figure 3.<br />

alIT<br />

2<br />

VCC3.3<br />

--<br />

+<br />

<br />

-=-<br />

-'-<br />

RI<br />

R2<br />

C9<br />

3.3V Power Supply<br />

vecs 112 1085<br />

,--__ ---, VCC1.S<br />

C2<br />

VCCIO<br />

VCCIO<br />

.---J.IN ADJ/GND alIT I--+---"-<br />

rl--+---