You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

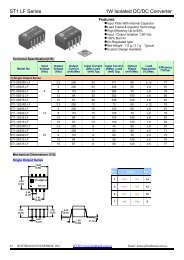

MSPS High-Speed A/D Converters<br />

ADC14C105 – PowerWise ® 14-bit, 105/95 MSPS ADC for High IF Sampling<br />

Features<br />

• 1 GHz full power bandwidth<br />

• 72 dBFS SNR at 240 MHz input<br />

• 82 dBFS SFDR at 240 MHz input<br />

• -79.3 dBFS THD at 240 MHz input<br />

• Power consumption: 400 mW<br />

• Single 3.3V supply operation<br />

• Available in LLP-32 packaging (5 x 5 x 0.8 mm)<br />

• 12-bit, 105/95 MSPS ADC ( ADC12C105)<br />

• 12-bit, 80/65 MSPS ADC ( ADC12C080)<br />

• 14-bit, 80/65 MSPS ADC ( ADC14C080)<br />

dBFS<br />

90<br />

85<br />

80<br />

75<br />

70<br />

65<br />

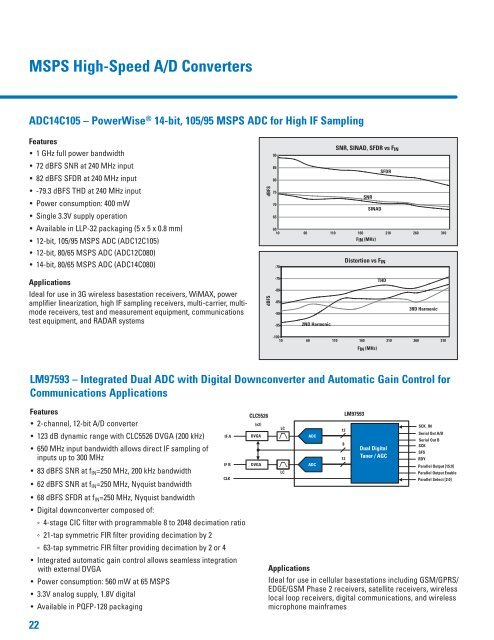

SNR, SINAD, SFDR vs F IN<br />

SINAD<br />

SFDR<br />

60<br />

10 60 110 160 210 260 310<br />

FIN (MHz)<br />

-70<br />

SNR<br />

Distortion vs F IN<br />

Applications<br />

Ideal for use in 3G wireless basestation receivers, WiMAX, power<br />

amplifier linearization, high IF sampling receivers, multi-carrier, multimode<br />

receivers, test and measurement equipment, communications<br />

test equipment, and RADAR systems<br />

dBFS<br />

-75<br />

-80<br />

-85<br />

-90<br />

-95<br />

2ND Harmonic<br />

THD<br />

3RD Harmonic<br />

-100<br />

10 60 110 160 210 260 310<br />

FIN (MHz)<br />

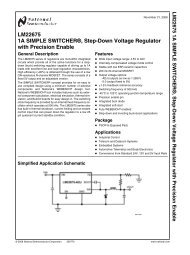

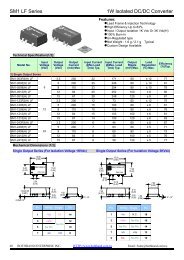

LM97593 – Integrated Dual ADC with Digital Downconverter and Automatic Gain Control for<br />

Communications Applications<br />

Features<br />

• 2-channel, 12-bit A/D converter<br />

• 123 dB dynamic range with CLC5526 DVGA (200 kHz)<br />

IF A<br />

• 650 MHz input bandwidth allows direct IF sampling of<br />

inputs up to 300 MHz<br />

IF B<br />

• 83 dBFS SNR at f IN =250 MHz, 200 kHz bandwidth<br />

CLK<br />

• 62 dBFS SNR at f IN =250 MHz, Nyquist bandwidth<br />

• 68 dBFS SFDR at f IN =250 MHz, Nyquist bandwidth<br />

• Digital downconverter composed of:<br />

˚ 4-stage CIC filter with programmable 8 to 2048 decimation ratio<br />

˚ 21-tap symmetric FIR filter providing decimation by 2<br />

˚ 63-tap symmetric FIR filter providing decimation by 2 or 4<br />

• Integrated automatic gain control allows seamless integration<br />

with external DVGA<br />

• Power consumption: 560 mW at 65 MSPS<br />

• 3.3V analog supply, 1.8V digital<br />

• Available in PQFP-128 packaging<br />

22<br />

CLC5526<br />

(x2)<br />

DVGA<br />

DVGA<br />

LC<br />

LC<br />

ADC<br />

ADC<br />

12<br />

8<br />

12<br />

LM97593<br />

Dual Digital<br />

Tuner / AGC<br />

SCK_IN<br />

Serial Out A/B<br />

Serial Out B<br />

SCK<br />

SFS<br />

RDY<br />

Parallel Output [15:0]<br />

Parallel Output Enable<br />

Parallel Select [2:0]<br />

Applications<br />

Ideal for use in cellular basestations including GSM/GPRS/<br />

EDGE/GSM Phase 2 receivers, satellite receivers, wireless<br />

local loop receivers, digital communications, and wireless<br />

microphone mainframes