AMSV Newsletter 2011

AMSV Newsletter 2011

AMSV Newsletter 2011

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

State Key Laboratory of<br />

Analog and Mixed-Signal VLSI<br />

State Key Lab of Analog and Mixed-Signal VLSI (SKL AMS-VLSI)<br />

<strong>Newsletter</strong><br />

Motto: “Locally, from (World) Quality towards (National) Quantity”<br />

座 右 銘 : 立 足 本 土 人 才 培 養 , 以 世 界 級 質 量 創 建 國 家 級 規 模<br />

Year 1<br />

No. 1<br />

<strong>2011</strong> Milestones<br />

December <strong>2011</strong><br />

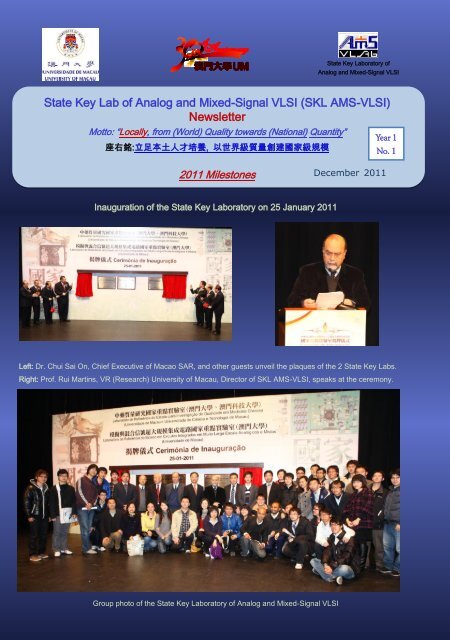

Inauguration of the State Key Laboratory on 25 January <strong>2011</strong><br />

Left: Dr. Chui Sai On, Chief Executive of Macao SAR, and other guests unveil the plaques of the 2 State Key Labs.<br />

Right: Prof. Rui Martins, VR (Research) University of Macau, Director of SKL AMS-VLSI, speaks at the ceremony.<br />

Group photo of the State Key Laboratory of Analog and Mixed-Signal VLSI

“Chip Olympics” – 58 th International Solid-State Circuits Conference - ISSCC <strong>2011</strong><br />

The 58 th IEEE International Solid-State Circuits Conference – ISSCC <strong>2011</strong> held between February 20 and 23, in San<br />

Francisco, USA, is the flagship conference of the Solid-State Circuits Society (SSCS), one of the largest of the 40<br />

societies of IEEE (Institute of Electrical and<br />

Electronics Engineers), and at the forefront of the<br />

current Information Age Revolution.<br />

UM (through SKL AMS-VLSI) was this year<br />

positioned as the 15 th in the world among 46<br />

universities that were able to publish there, 5th in<br />

Asia and 1 st in China with 2 chips selected for<br />

presentation and entitled: “A 0.46mm 2 4dB-NF Unified Receiver Front-End for Full-Band Mobile TV in 65nm CMOS” (left),<br />

and “A 0.024mm 2 8-bit 400 MS/s SAR ADC with 2-bit/Cycle and Resistive DAC in 65 nm CMOS” [Silk Road Award for<br />

Region 10 – Asia, Australia, the Pacific.] (right)<br />

Important Events<br />

Two PhD Oral Defenses on<br />

Microelectronics held on 22-July <strong>2011</strong><br />

Title: High Speed Power / Area<br />

Optimized Multi-Bit / Cycle SAR<br />

ADCs (Silk Road Award ISSCC<strong>2011</strong>)<br />

Candidate: He-Gong Wei (Abner)<br />

Title: Circuit Techniques for<br />

High-Performance SAR Type<br />

ADCs (Award ASSCC<strong>2011</strong>,TopAsia)<br />

Candidate: Yan Zhu (Julia)<br />

State Key Lab of AMS-VLSI / Science Series<br />

22-23 July <strong>2011</strong><br />

1 st Distinguished Lectures, PhD Oral Defenses<br />

& Lab Workshop<br />

Prof. Ian A. Galton, IEEE Fellow, Univ. of California, San<br />

Diego, USA<br />

• Mismatch-Shaping Techniques for<br />

Delta-Sigma Data Converters<br />

• Digital Background Calibration in<br />

Pipelined ADCs<br />

PhD Oral Defenses on Microelectronics<br />

Prof. Bram Nauta, IEEE Fellow, Univ. of Twente, The<br />

Netherlands<br />

• Ultra low-power & Wideband<br />

High-speed Nyquist AD Converter<br />

• RF Circuit Techniques in<br />

Nanometer CMOS<br />

Prof. Boris Murmann, Stanford Univ.,<br />

San Francisco, USA<br />

• Analysis and Design of<br />

Switched-Capacitor Circuits<br />

• Design of Pipelined A/D Converters<br />

• Digitally Assisted Data Converter<br />

Design<br />

First Distinguished Lectures, PhD Oral Defenses & Lab Workshop on 22 and 23 July <strong>2011</strong>

Second Class Award of The State Scientific and Technological Progress Award<br />

[China National Award]<br />

Second Class Award of The State Scientific and Technological Progress Award to be received by Prof. Seng-Pan U,<br />

Prof. Pui-In Mak and Dr. Sai-Weng Sin for their contribution in microelectronics research. The State Science and<br />

Technology Prizes ( 國 家 科 學 技 術 獎 勵 ) is the highest honor in China in science and technology, in order to recognize<br />

citizens and organizations that have made remarkable contributions to scientific and technological progress, and to<br />

promote the development of science and technology.<br />

PhD Student Ranks No. 1 at the Student Design Contest in A-SSCC <strong>2011</strong><br />

Three PhD students Ms. Zhu Yan (Julia), Mr. Chan Chi Hang and Mr. Wong Si Seng, led by Dr. Sin Sai Weng, Prof. U<br />

Seng Pan and Prof. Rui Martins, have developed three advanced nanometer analog-to-digital converter and comparator<br />

chips that were all accepted by the IEEE Asian Solid-State Circuits Conference (A-SSCC), known as “Asia’s Chip<br />

Olympics”. One of the relevant papers also won the student design contest, ranking No. 1, ahead of Korea Advanced<br />

Institute of Science and Technology (KAIST) and Tokyo Institute of Technology (TIT). Macao was the only region to<br />

achieve a paper acceptance rate of 100% at this year’s A-SSCC, with all the papers from UM.<br />

Left: SKL AMS-VLSI onsite demonstration at this year’s A-SSCC for the paper award design contest attracts many world-renowned experts<br />

Right: Announcement of the Awardees with PhD student Julia ranking No. 1 in Asia, with UM ahead of KAIST & TIT at the student design contest.<br />

A-SSCC is Asia’s most prestigious conference in the field of integrated circuits and provides a platform for top institutions<br />

from the industry and the academia (most from Asia, but also many from Europe and the U.S.) to showcase their latest<br />

technological achievements. This year’s conference was held in Jeju, South Korea.<br />

US Patents Granted in <strong>2011</strong><br />

• PUI-IN MAK, SENG-PAN U, R.P.MARTINS, DC-Offset Canceled Programmable Gain Array for Low-Voltage<br />

Wireless LAN System and Method Using the Same, US Patent No. 7,948,309, from May 24, <strong>2011</strong>.<br />

• PUI-IN MAK, SENG-PAN U, R.P.MARTINS, Two-step Channel Selection for Wireless Transmitter Front-Ends, US<br />

Patent No. 8,019,290 B2, from September 13, <strong>2011</strong>.<br />

Books<br />

• PUI-IN MAK, R.P.MARTINS, High-/Mixed-Voltage Analog and RF Circuit Techniques for Nanoscale CMOS,<br />

Springer - USA, to appear in January 2012.<br />

• SAI-WENG SIN, SENG-PAN U, R.P.MARTINS, Generalized Low-Voltage Circuit Design Techniques for Very<br />

High-Speed Time-Interleaved Pipelined ADC, Springer - Analog Circuits and Signal Processing, ISBN<br />

978-90-481-9709-5, Dordrecht, The Netherlands: Springer, January <strong>2011</strong>.

Journal Papers in <strong>2011</strong><br />

• PUI-IN MAK, R.P.MARTINS, “A 0.46mm 2 4-dB NF Unified Receiver Front-End for Full-Band Mobile TV in 65nm CMOS”,<br />

IEEE Journal of Solid-State Circuits, vol. 46, No.9, pp.1970-1984, September <strong>2011</strong>.<br />

• ZUSHU YAN, PUI-IN MAK, R.P.MARTINS, “Double recycling technique for folded-cascode OTA”, Analog Integrated<br />

Circuits and Signal Processing, Springer, 28 August <strong>2011</strong>.<br />

• ZUSHU YAN, PUI-IN MAK, R.P.MARTINS, “Two-Stage Operational Amplifiers: Power-and-Area-Efficient Frequency<br />

Compensation for Driving a Wide Range of Capacitive Load”, IEEE CAS Magazine, vol. 11, No.1, pp.26-42, 1st Quarter<br />

<strong>2011</strong>.<br />

IEEE Conferences – 26 Papers (25 in <strong>2011</strong>)<br />

ISSCC 2012, San Francisco, USA, February 2012<br />

1. “A 0.016mm 2 144μW Three-Stage Amplifier Capable of Driving 1-to-15nF Capacitive Load with >0.95MHz GBW”<br />

RFIT <strong>2011</strong>, Beijing, China, December<br />

2. “Design Techniques for Nanometer Wideband Power-Efficient CMOS ADCs”<br />

ISOCC <strong>2011</strong>, Jeju, South-Korea, November<br />

3. “Hybrid Loopfilter Sigma-Delta Modulator With NTF Zero Compensation”<br />

A-SSCC <strong>2011</strong>, Jeju, South-Korea, November<br />

4. “A Reconfigurable Low-Noise Dynamic Comparator with Offset Calibration in 90nm CMOS”<br />

5. “A 35 fJ 10b 160 MS/s Pipelined-SAR ADC with Decoupled Flip-Around MDAC and Self-Embedded Offset Cancellation”<br />

(Award - Top Asia)<br />

6. “A 5-bit 500MS/s Comparator-Strengthening Binary-Search ADC”<br />

PRIMEASIA <strong>2011</strong>, Macao, China, October<br />

7. “A Double Active-Decoupling Technique for Reducing Package Effects in a Cognitive-Radio Balun-LNA” (Award - Gold<br />

Leaf)<br />

8. “A Novel Digital Predistortion Technique for Class-E PA with Delay Mismatch Estimation” (Award - Silver Leaf)<br />

9. “A Nonlinearity Digital Background Calibration Algorithm for 2.5bit/stage Pipelined ADCs with Opamp sharing<br />

Architecture” (Award - Bronze Leaf)<br />

10. “NTF Zero Compensation Technique for Passive Sigma-Delta Modulator”<br />

11. “A FPGA-Based Power Electronics Controller for Hybrid Active Power Filters”<br />

12. “A Time-Efficient Dither-Injection Scheme for Pipeline SAR ADC”<br />

ESSCIRC <strong>2011</strong>, Helsinki, Finland, September<br />

13. “A 7-bit 300-MS/s Subranging ADC with Embedded Threshold & Gain-Loss Calibration”<br />

EMBC <strong>2011</strong>, Boston, Massachusetts, USA, August<br />

14. “An Ultra-Low-Power Filtering Technique for Biomedical Applications”<br />

MWSCAS <strong>2011</strong>, Seoul, South-Korea, August<br />

15. “A Dual-VCO-Based Quantizer with Highly Improved Linearity and Enlarged Dynamic Range”<br />

16. “Multi-Merged-Switched Redundant Capacitive DACs for 2b/cycle SAR ADC”<br />

17. “Noise Shaping Implementation in Two-Step/SAR ADC Architectures Based on Delayed Quantization Error”<br />

18. “A Charge Pump Based Timing-Skew Calibration for Time-Interleaved ADC”<br />

19. “Clock-Jitter Sensitivity Reduction in CT Sigma-Delta Modulators Using Voltage-Crossing Detection DAC”<br />

20. “A Passive Excess-Loop-Delay Compensation Technique for Gm-C Based Continuous-Time Sigma-Delta Modulators”<br />

ICIEA <strong>2011</strong>, Beijing, China, June<br />

21. “FPGA-based Decoupled Double Synchronous Reference Frame PLL for Active Power Filters”<br />

ISCAS <strong>2011</strong>, Rio de Janeiro, Brazil, May<br />

22. “A Single-to-Differential LNA Topology with Robust Output Gain-Phase Balancing against Balun Imbalance”<br />

23. “A High-Voltage-Enabled Recycling Folded Cascode Opamp for Nanoscale CMOS Technologies”<br />

EUROCON <strong>2011</strong>, Lisbon, Portugal, April<br />

24. “A Linearity-Improved Ultra-Wideband Balun-LNA for Cognitive Radio”<br />

ISSCC <strong>2011</strong>, San Francisco, USA, February<br />

25. “A 0.024mm 2 8-bit 400 MS/s SAR ADC with 2-bit/Cycle and Resistive DAC in 65 nm CMOS" (Silk-Road Award)<br />

26. “A 0.46mm 2 4dB-NF Unified Receiver Front-End for Full-Band Mobile TV in 65nm CMOS”<br />

State Key Laboratory of Analog and Mixed-Signal VLSI / UM<br />

http://www.fst.umac.mo/en/lab/ans_vlsi/